#### BACHELOR THESIS COMPUTING SCIENCE

RADBOUD UNIVERSITY

### Optimizing the NIST Post Quantum Candidate SPHINCS+ using AVX-512

Author: Dor Mariel Alter S1027021 dor.alter@student.ru.nl First supervisor/assessor: Prof. dr. Peter Schwabe peter@cryptojedi.org

Second supervisor: Prof, dr. Bo-Yin Yang byyangat@iis.sinica.edu.tw

> Second assessor: Prof. dr. Joan Daemen j.daemen@cs.ru.nl

August 25, 2021

#### Abstract

Today's cryptography is not strong enough to ensure the security risks we might face in the future. One of the threats to cryptography is quantum computers, and for that reason, NIST created the NIST Post Quantum Cryptography Standardization (PQC), a standardization process for post-quantum schemes. SPHINCS+ is one of the schemes in the alternative candidates in the third round of this project. The main disadvantage of SPHINCS+ is its speed performance. This thesis analyzes ways to improve its performance using parallelism, more precisely using Intel's AVX-512. Using this approach, we can achieve  $1.8 \times$  or  $1.45 \times$  speed up for key generation and signing (for the s and the f options of the scheme) and a near 1.3x time improvement for verification in the case of SHA256, compared to the AVX2 version, which is submitted to the NIST Post Quantum Cryptography Standardization. In the case of SHAKE256, we get  $2.7 \times$  speed up performance for key generation and signing and  $1.9 \times$ improvement for verification, comparing to the AVX2 version, which is submitted to the NIST Post Quantum Cryptography Standardization. We also present a comparison to the other NIST candidates who are still part of the third round.

**Keywords:** AVX2, AVX-512, hash, SHA256, SHAKE256, SPHINCS+, NIST PQC, vectorization.

## Contents

| 1        | Int                                    | roduction                                                                                                                                                                                                                                                                                  | 3                                                                                  |

|----------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| <b>2</b> | Pre                                    | liminaries                                                                                                                                                                                                                                                                                 | 5                                                                                  |

| _        | 2.1                                    | SPHINCS+                                                                                                                                                                                                                                                                                   | 5                                                                                  |

|          |                                        | 2.1.1 One Time Signature (OTS) Scheme                                                                                                                                                                                                                                                      | 5                                                                                  |

|          |                                        | 2.1.2 WOTS+                                                                                                                                                                                                                                                                                | 6                                                                                  |

|          |                                        | 2.1.3 Hypertree and FORS                                                                                                                                                                                                                                                                   | 10                                                                                 |

|          |                                        | 2.1.4 SPHINCS+                                                                                                                                                                                                                                                                             | 14                                                                                 |

|          |                                        | 2.1.5 SPHINCS+ Instantiation                                                                                                                                                                                                                                                               | 15                                                                                 |

|          | 2.2                                    | Hash Functions                                                                                                                                                                                                                                                                             | 16                                                                                 |

|          |                                        | 2.2.1 SHA256                                                                                                                                                                                                                                                                               | 16                                                                                 |

|          |                                        | 2.2.2 SHAKE256                                                                                                                                                                                                                                                                             | 19                                                                                 |

|          | 2.3                                    | Intel Advanced Vector Extensions 512                                                                                                                                                                                                                                                       | 25                                                                                 |

|          |                                        | 2.3.1 Single Instruction Multiple Data                                                                                                                                                                                                                                                     | 25                                                                                 |

|          |                                        | 2.3.2 Intel Advanced Vector Extensions 512                                                                                                                                                                                                                                                 | 26                                                                                 |

| 3        | $\operatorname{Rel}$                   | ated Work                                                                                                                                                                                                                                                                                  | 28                                                                                 |

| 4        | Opt                                    | imizing SPHINCS+                                                                                                                                                                                                                                                                           | 30                                                                                 |

|          | 4.1                                    | SHA256 Implementation                                                                                                                                                                                                                                                                      | 31                                                                                 |

|          | 4.2                                    |                                                                                                                                                                                                                                                                                            | 0.4                                                                                |

|          |                                        | SHAKE256 Implementation                                                                                                                                                                                                                                                                    | 34                                                                                 |

| 5        | ΑT                                     | -                                                                                                                                                                                                                                                                                          |                                                                                    |

| 5        | <b>A I</b><br>5.1                      | ower Bound on the Amount of Cycles per Hash                                                                                                                                                                                                                                                | 36                                                                                 |

| 5        |                                        | ower Bound on the Amount of Cycles per Hash                                                                                                                                                                                                                                                |                                                                                    |

| -        | $5.1 \\ 5.2$                           | cower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256                                                                                                                                                                                                               | <b>36</b><br>37<br>39                                                              |

| 5<br>6   | 5.1<br>5.2<br><b>Res</b>               | Lower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256         SHAKE256         Sults and Comparison                                                                                                                                                                 | <b>36</b><br>37<br>39<br><b>43</b>                                                 |

| -        | 5.1<br>5.2<br><b>Res</b><br>6.1        | Lower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256         SHAKE256         Sults and Comparison         Comparison of Lower Bound to Run Time                                                                                                                   | <b>36</b><br>37<br>39<br><b>43</b><br>43                                           |

| -        | 5.1<br>5.2<br><b>Res</b><br>6.1<br>6.2 | Lower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256         SHAKE256         Sults and Comparison         Comparison of Lower Bound to Run Time         Comparison of Single Hash in AVX2 and AVX512                                                              | <ul> <li>36</li> <li>37</li> <li>39</li> <li>43</li> <li>43</li> <li>44</li> </ul> |

| -        | 5.1<br>5.2<br><b>Res</b><br>6.1        | Lower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256         SHAKE256         Gults and Comparison         Comparison of Lower Bound to Run Time         Comparison of Single Hash in AVX2 and AVX512         Comparision of different implementations of SPHINCS+ | <b>36</b><br>37<br>39<br><b>43</b><br>43<br>44<br>45                               |

| -        | 5.1<br>5.2<br><b>Res</b><br>6.1<br>6.2 | Lower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256         Sults and Comparison         Comparison of Lower Bound to Run Time         Comparison of Single Hash in AVX2 and AVX512         Comparision of different implementations of SPHINCS+         6.3.1    | <b>36</b><br>37<br>39<br><b>43</b><br>43<br>44<br>45<br>45                         |

| -        | 5.1<br>5.2<br><b>Res</b><br>6.1<br>6.2 | Lower Bound on the Amount of Cycles per Hash         SHA256         SHAKE256         SHAKE256         Gults and Comparison         Comparison of Lower Bound to Run Time         Comparison of Single Hash in AVX2 and AVX512         Comparision of different implementations of SPHINCS+ | <b>36</b><br>37<br>39<br><b>43</b><br>43<br>44<br>45                               |

7 Conclusions and Future Work

$\mathbf{58}$

## Chapter 1 Introduction

Today, cryptographic schemes such as signature schemes can be found in most of our daily used devices and online activities. For instance, when we connect to a website that uses the TLS protocol or run a software update, the browser or the app verifies that the web page or update arrived from the right source using such cryptographic shchemes [33]. Nowadays, most schemes rely on a hard problem to solve, such as discrete logarithm or factorization. However, some of those problems will no longer be hard to solve if quantum computers will be used [35].

At the state of the art, quantum computers are still not able to threaten those schemes, however experts believe that within 15-30 years this will no longer be the case [24]. Therefore, the National Institute of Standards and Technology (NIST) initiated the Post-Quantum Cryptography Standardization process (PQC), where at the end, NIST will announce their recommendation for post-quantum schemes [29]. This project started with 69 candidates in its first round for both public-key encryption and kev-establishment algorithms and digital signature algorithms [30]. This list was narrowed down to seventeen candidates for public-key encryption and key-establishment algorithms and nine candidates for digital signature algorithms in the second round [31]. Moreover, at the time of writing this thesis, this competition is in its third round, and there are four finalists for public-key encryption and key-establishment algorithms and five alternative candidates, and there are three finalists for digital signature algorithms and another three alternative candidates [32].

One of the candidates that is part of the alternative candidates for the digital signature algorithms is the SPHINCS+ scheme. SPHINCS+ is a stateless hash-based signature scheme that is believed to be quantum secure [4]. There are quite a few advantages for using SPHINCS+: minimal security assumptions, state-of-the-art attacks are easily analyzed, small key

sizes and reuse of established building blocks. To sum up the advantages and limitations of SPHINCS+ in one sentence, SPHINCS+ is probably the most conservative design of a post-quantum signature scheme. However, it is relatively inefficient in terms of signature size and speed [4]. Due to this disadvantage, SPHINCS+ is not one of the finalists of the third round but rather on the list of alternative candidates.

This leads us to the purpose of this thesis: to investigate how to speed up SPHINCS+ performance. Different parameters can be used for SPHINCS+, which balance between the speed and the signature size, such that the smaller the signature size is, the slower the scheme becomes. So, boosting the performance in terms of speed might be able to improve both issues. Currently, there are mainly two implementations for SPHINCS+, one of them, the so-called optimized implementation, using the Advanced Vector Extensions 2 (AVX2), [17]. The Advanced Vector Extensions (AVX) is a family of vector extensions used in Intel processors, allowing us to perform more operations simultaneously. In 2017, Intel released a new extension called AVX-512 [11], which allows us to perform even more operations at once compared to AVX2. Therefore, we can further optimize the performance of the SPHINCS+ scheme using this AVX-512.

In this thesis, we will try to answer the question: To what extent can we improve the speed of the NIST candidate SPHINCS+ using AVX-512? For that purpose, we propose a new implementation for SPHINCS+ using AVX-512, which can be found at [1]. We will first explain how SPHINCS+ and its lower level schemes work and the improvements in using AVX-512 (chapter 2). After we understand the scheme, we will talk about other NIST candidates, to which we will compare our implementation and another implementation that was used in our code (chapter 3). Then, we will move on to a higher-level explanation of the scheme's implementation using AVX-512 (chapter 4). Afterward, we will derive a lower bound on the amount of operation for the hashes (chapter 5). Thereupon, we will show the results and compare our implementation to other SPHINCS+ implementation and NIST PQC candidates (chapter 6). Finally, in chapter 7, we will conclude this thesis and discuss further impairments of the scheme as future work.

### Chapter 2

### Preliminaries

#### 2.1 SPHINCS+

SPHINCS+ is a post-quantum stateless hash-based signature scheme designed and implemented by Bernstein, Dobraunig, Eichlseder, Fluhrer, Gazdag, Hülsing, Kampanakis, Kölbl, Lange, Lauridsen, Mendel, Niederhagen, Rechberger, Rijneveld, and Schwabe [4]. SPHINCS+ is a participant in the NIST Post-Quantum Cryptography Standardization Process (PQC), in which NIST will announce which one of the candidates will become their standard scheme [25]. SPHINCS+ is built on the original SPHINCS scheme [6]. However, it has some improvements such as multi-target attack protection, compressed treeless WOTS+ public key, FORS instead of HORST and verifiable index selection [4]. As SPHINCS+ is a hash-based signature scheme, it relies on a hash function. There are three possible versions of hashes used, SHA-256 (SHA2), SHAKE256 (SHA3) and Haraka. However, for the scope of this thesis, we are going to focus on the two mainstream hashes, which are SHA-256 and SHAKE256. before we explain the SPHINC+ scheme, we will first introduce its dependencies, namely WOTS+, FORC and the hyper trees. In the next two subsections, we will look at how each of them works and later, we will see how they are used to create the final SPHINCS+ scheme.

#### 2.1.1 One Time Signature (OTS) Scheme

One Time Signatures are schemes that can be used to sign only one message. These schemes are the basis of some of the more complicated signature schemes, therefore, it is important first to understand them. The simplest example is the 0-bit message signature, in which the sender does not send a specific message, but the receiver knows that the message received is from the sender. A real-life example of this was the Yo App [27], an app that allowed the users to only send the message "Yo" to each other. It works as follows: the sender uses a secret key and publishes its hash as their public key. Then, after sending the message, the sender also sends the private key. The receiver hashes the private key, compares it to the sender's public key and if they match, the sender is authenticated. This idea, although rather simple, is the building block for more complex schemes. Let us also consider the 1-bit message scheme, which works as follows: the sender generates two random values  $(sk_0, sk_1)$  which are the private key, then hashes each one of them and publishes the result, as their public key. Then, when the sender wants to send a message, they send either  $sk_0$  or  $sk_1$  for the bit to be 0 or 1, respectively. Now, the receiver can hash the message and compare it to the public key, which will tell them if the value is zero or one and that the signature on the 1-bit message is verified. After we understand the simple cases of OTS, we can move on to more complicated schemes used in SPHINCS+.

#### 2.1.2 WOTS+

WOTS+ is a one-time signature (OTS) scheme designed by Hülsing [16], which is an improved version of the famous Winternitz OTS (WOTS) scheme [8]. The main idea of both schemes is to use the so-called chain functions starting from the private key up to the public key. Those chain functions are recursively applied to their output several times, until we get the final value, whence their name as chain functions. Next, we will explain how WOTS works and afterward, we will see how it matured to WOTS+.

#### WOTS

We start by looking at how WOTS works [8]. WOTS is a one time signature scheme. In this scheme, we sign messages, those messages could be either fixed length messages or the hash values of the messages with a fixed length. In WOTS, there are two keys (public and private), consisting of l pseudo-random values of w bits each, where w is the base used, which is the fixed length we mentioned above.

To compute the length of l, there are two other values that needed to be calculated first. Those being  $l_1$ , the amount of blocks we divide the message into and  $l_2$  the length of the checksum. Then l is the sum of  $l_1$  and  $l_2$ . Given the length of the message  $l_m$  and base w,  $l_1$  and  $l_2$  are computed as follows,  $l_1 = \lceil \frac{l_m}{\log_2(w)} \rceil$  and  $l_2 = \lfloor \frac{\log_2(l_1 \cdot (w-1))}{\log_2(w)} \rfloor + 1$ .

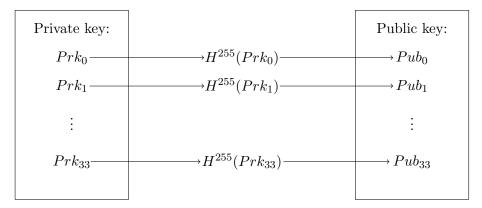

For simplicity, we are going to use base 256 and message length 256 bits as well in our explanation and figures, which gives us  $l_1 = 32$  and  $l_2 = 2$ . Hence the private key is denoted by  $Prk_0$  to  $Prk_{33}$  and the public key is denoted by  $Pub_0$  to  $Pub_{33}$ , where each value is 256-bits long. The function H is defined as follows  $H : \{0,1\}^{256} \rightarrow \{0,1\}^{256}$ , this function can be seen as a non-compressive cryptographic hash function. The public key is generated by applying the hash function H 255 times on each 256-bit value from the private key and then concatenating the results, as shown in Figure 2.1.

Figure 2.1: WOTS+ generation of the public key using the private key.

To elaborate upon this idea and better understand how to perform key generation for WOTS, a pseudocode is also given for that algorithm, Algorithm 1. Unlike in the case of the figures, the pseudocode does not use a specific base, such as 256, but rather w as the base value.

Algorithm 1 Key generation for WOTS

1: function KEYPAIR\_WOTS()

2:  $sk \leftarrow \$(sk_1, sk_2, \dots, sk_l)$

3: for i = 0 to l do

4:  $pk_i = H^{w-1}(sk_i)$

5: end for

6: return  $sk \ pk$

7: end function

Notice that the  $\$  represents generating values uniformly at random and H is the non-compressive cryptographic hash function mentioned above.

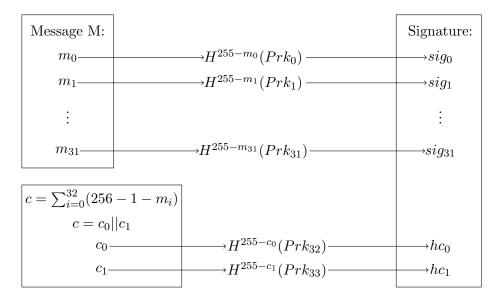

After we got a notion of how the keys are generated, we look at how to sign a message. Let message M be a message with a length of 256 bits, otherwise, apply a hash function to turn it to 256 bits. We break M into 32 values denoted by  $m_i$ , as it is 256 bits, we know that each element will be 8-bits long. Then, for each  $m_i$  we compute  $H^{255-m_i}(Prk_i)$ . Unfortunately, this is not enough for signing the message as it is still prone to forgery. For example, given a message and its signature  $m = (6, m_1, \ldots, m_{31})$  an attacker can perform another iteration of the hash resulting in a new valid signature for a different message,  $m = (7, m_1, \ldots, m_{31})$ . To deal with this, the scheme introduces a checksum for each  $m_i$ . We compute the checksum across all values of  $m_i$  as follows:  $c = \sum_{i=0}^{32} (256 - 1 - m_i)$ . Then we can write c as two values  $c_0$  and  $c_1$  and compute the hash chain function H on them. So, if we increase one of the  $m_i$ , the values of the  $c_i$  decrease and the signature is no longer valid. An illustration of this procedure is shown in Figure 2.2.

Figure 2.2: WOTS+ singing a message M with 256 bits length.

Again for better understanding, a pseudocode for that algorithm, Algorithm 2 is also provided.

| Algorithm 2 Signing a message using WOTS                                        |  |  |

|---------------------------------------------------------------------------------|--|--|

| 1: function SIGNING_WOTS $(M, sk)$                                              |  |  |

| 2: $CS \leftarrow c_0   c_1   \dots   c_{l_2} = \sum_{i=1}^{l_1} (w - 1 - M_i)$ |  |  |

| 3: for $i = 0$ to $l_1$ do                                                      |  |  |

| 4: $sig_i \leftarrow H^{w-1-m_i}(sk_i)$                                         |  |  |

| 5: end for                                                                      |  |  |

| 6: for $i = 0$ to $l_2$ do                                                      |  |  |

| 7: $hc_i \leftarrow H^{w-1-c_i}(sk_{i+32})$                                     |  |  |

| 8: end for                                                                      |  |  |

| 9: return $sig, hc$                                                             |  |  |

| 10: end function                                                                |  |  |

Note that bars (||) represent concatenation.

This works as we know that M is 256 bits long, so if we break M into 32 values, we will get 8-bit values (as 256/32 = 8) and we know that  $2^8 = 256$ . So, 255 is the highest value we can get for  $m_i$ , which means that we will always get a non-negative value for the expression of  $H^{255-m_i}$ .

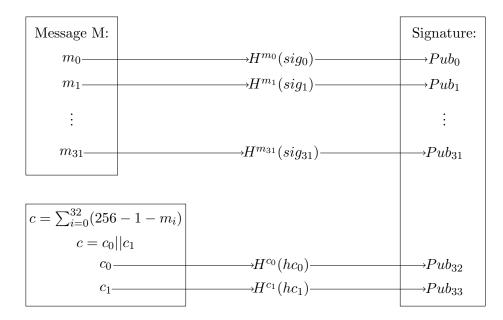

Verifying is as simple as taking each  $sig_i$  value and applying H on it  $m_i$  times as shown in Figure 2.3 and then comparing it to the public key and verifying the checksum in the same manner.

Figure 2.3: WOTS+ verifying a message M with 256 bits length.

The algorithm for verifying will return True if the signature is valid and False otherwise. The following pseudocode for verification, Algorithm 3 is used.

Algorithm 3 Verifying a signature using WOTS

1: function VERIFYING\_WOTS(M, sig, pk, hc)for i = 0 to  $l_1$  do 2: 3:  $ver_i \leftarrow H^{m_i}(sig_i)$ end for 4:  $c_0 ||c_1|| ... ||c_{l_2} \leftarrow \sum_{i=1}^{l_1} (w - 1 - M_i)$ for i = 0 to  $l_2$  do 5:6:  $ver_{l_1+i} \leftarrow H^{c_i}(hc_i)$ 7: 8: end for if pk == ver then 9: return True 10: else 11:return False 12:end if 13:14: end function

#### From WOTS to WOTS+

Since its first introduction, WOTS has been modified and improved upon, while the most noticeable improvement is WOTS+ [16]. Similar to WOTS, WOTS+ also has several versions. Unfortunately, they share the same name, although they have slight differences. As a result, the WOTS+ used in SPHINCS+ is different from the original version. The WOTS+ used in SPHINCS+ introduces two additional parameters which turn the hash function into a tweakable hash function compared to the WOTS discussed above. This notion is beyond the scope of this thesis, but more information can be found in [2]. For this thesis, we can consider WOTS+ as a version of WOTS which takes two extra parameters [5], those being the position of the node in the tree, called address, and a public seed while the signatures have the same procedures as WOTS.

#### 2.1.3 Hypertree and FORS

As the name might suggest, WOTS+ alone is not sufficient for a signature scheme as it is a one-time signature scheme. This means that every time we want to sign a message, we will have to generate a new key pair, which is inconvenient if we want to sign a large number of messages under the same key at the same time. Therefore, we combine WOTS+ with hypertrees in order to address this issue. However, before we can talk about hypertrees, we will first explain how trees can be used to sign messages. For that purpose, we will discuss Merkle trees in the next part.

#### Merkle tree

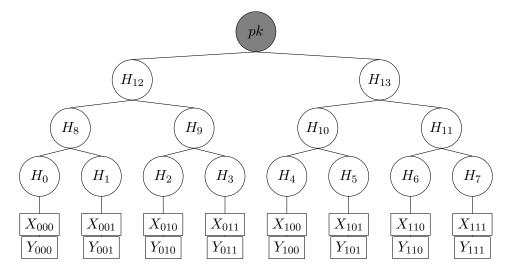

A Merkle tree is a type of hash tree used to sign and verify messages, which was designed by dr. Merkle [23]. One of the main disadvantages of schemes that use this method is being stateful, meaning that we need to save the state in which our tree is. The main idea of Merkle tree is to have a tree with a root (gray circle node), nodes (circle nodes) and leaf elements (rectangle node) as can be seen in Figure 2.4. Now, the root of this tree is designated as the public key. The leaf elements are the public key,  $Y_i$ , and private key,  $X_i$ , of the given signature scheme. The nodes are the hashed value of the concatenation of their children. Notice that when talking about height, the leaves are not taken into consideration because they are not an actual part of the tree, but rather an initializer for the nodes. Therefore, in the tree below Figure 2.4, they are not represented as nodes.

Figure 2.4: Merkle tree of height 3

To sign a message M using the Merkle tree, we will first use the signature scheme given in the leaf, which gives us  $sig' = sign'(M, X_i)$ . However, unlike in the previous scheme, just publishing the signature, sig', and the public key, whether it is the public key of the leaf  $(Y_i)$  or the public key of the scheme (pk), is not enough. In order to get the public key pk from a leaf used to sign it, we need the path from that leaf to the root. Therefore, we will include an additional parameter, AUTH in the signature, being the concatenation of all nodes in the path leading from the leaf to the root. So, the signature will look like this  $sig = (i, sign(M, X_i), Y_i, AUTH)$ . As an example, assuming we want to sign message M using  $X_{010}$ , we first sign M using  $X_{010}$  so we have  $sig'_{010} = sign'(M, X_{010})$ , then we add  $Y_{010}$ , the public key of  $X_{010}$ , then we add the index of the leaf 010 and finally the authentication path, which gives us  $sig = (010, sig'_{010}, Y_{010}, (H_8||H_3||H_{13})$ . To verify sig, we will first use the leaf scheme to verify that  $sign'(M, X_i)$  indeed gives  $Y_i$  and then use  $Y_i$  together with the authentication path to reconstruct the public key. We compare it to the known public key pk and if they match, then we know that the signature is valid.

The idea of stateful here comes from the fact that we also need to update the i for every signature and ensure the same i's do not repeat. If we do not, we risk using the same leaf twice, which might reveal information about the message or might allow attackers to create a forgery, depending on the scheme we use in the leaf. This is due to the fact that the scheme used in the leaves is a one time signature scheme, which means that it must only be used once.

#### Hypertree

Now, after having a better understanding of the way trees can be used for signing, we can look at hypertrees schemes, which is equivalent to the XMSS scheme [9], where the main idea is to use a tree as the constructor for the scheme. Afterward, we will extend upon this idea to get a multi-tree setting rather than one big tree, which is equivalent with  $XMSS^{MT}$  [15].

So, as explained earlier, we do not want to use the same leaf twice, and we want to have enough leaves to sign more messages. The straightforward approach to solve this issue would be to create a signal tree called a hyper tree that is large enough such that there would be sufficient leaves. However, as we increase the height of a tree, we need to consider that we increase the cost of using and constricting this tree. By doing so, we will get  $2^h$  leaves, where h is the height.

In order to improve upon this issue, we use multi hypertree, thus reducing the cost, by using multiple smaller trees instead of a single big tree. This approach will give us  $a \times 2^{h'}$  leaves, where a is the number of trees, and h' is the height of those trees. In this case, we can have the same amount of leaves, but as we have multiple unrelated trees, on which we can work in parallel, it increases the efficiency of the scheme.

#### FORS

Another method that can be used to reduce the impact of using the same leaf twice is to use a few time signature scheme (FTS), rather than an OTS. This way, we will ensure that we will not leak any vital information even if we use the same leaf twice. After discussing how trees could be used for OTS signing, we will look at their use for FTS signing. The scheme used for that purpose is Forest of Random Subsets (FORS), where the main idea is not to use only one tree, but rather a forest of trees.

Let us look at how FORS works. As in the case of the Merkle tree, we have a public key associated with the sender. However, unlike in the Merkle tree scheme, it is not the root of a single tree, but the concatenation of the roots of all the trees. This public key is computed before sending any message and is published by the sender. To sign a message, we need it to be the same size as the block size,  $k \times a$ , which means that we need k strings of length a bits. Then, we do the following: we have k trees, and each of them has  $2^a$  leaves, so each value of a string will be interpreted as a leaf in one of the k trees. Afterward, as we have seen in the Merkle tree above, we can sign by using the node representing one string of a together with the authentication path to the root. So, our signature will be the leaf represented by the value of a and the authentication path to the root of that tree, and we can concatenate the results and send it. To verify the signature, we need to reconstruct the k roots of the trees and compare it to the value of the roots given in the public key.

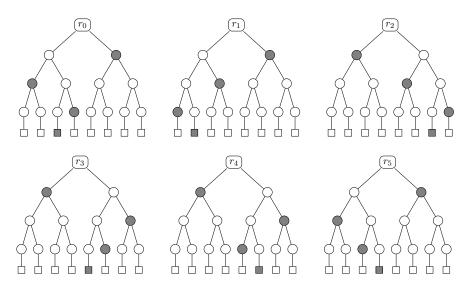

Figure 2.5: An illustration of a FORS signature with k = 6 and a = 3, for the message 010 001 110 100 101 011.

In Figure 2.5 we can see an example of a signature using FORS. In this case, we see that we have six trees (k = 6), and the tree's height is 3 (a = 3). Thus, a message should be of length  $3 \times 6 = 18$  bits. In this case, we want to sign the following message 010 001 110 100 101 011, which is indeed 18 bits

long. So, we split it into six values of 3 bits each as a is 3. The signature will consist of the gray leaf (representing the leaves corresponding to the six values we split m into) and the gray nodes. As can be seen in Figure 2.5 for each tree, we can construct its root using the gray nodes, thus, verifying the signature. We can also see that the message m is not the value of the leaf node, but rather a pointer towards a specific node, meaning that the values of the roots and leaves are not dependent on the message. But instead, the leaves are chosen by the message, which means that we can compute the leaves when generating the public and private keys.

#### 2.1.4 SPHINCS+

Finally, after discussing the smaller schemes used in SPHINCS+, we can discuss how the scheme works as a whole.

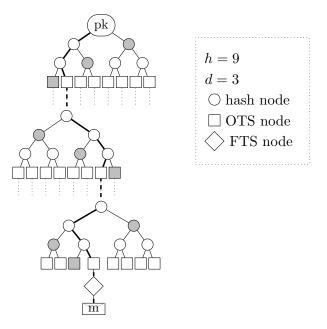

Figure 2.6: Illustration of a small SPHINCS+ structure, Figure reprinted from [2].

In Figure 2.6 we can see an illustration of how we sign a message m. However, before we can sign any message, we need to generate the SPHINCS+ key pair. Like any other public-key scheme, SPHINCS+ consists of a public key and a private key. The public key is composed of two *n*-bit values: the root node of the top trees in the scheme and a random public seed. The private key is also composed of two *n*-bit values, two random seeds, one for WOTS+ and FORS and another for the randomized message digest. As we discussed in FORS, we do not generate the leaves when signing a message, but rather we create them in the key generation process. After generating these keys and understanding how the tree is created, we can discuss how we sign a message. We sign a message using FORS, and then we sign the FORS pubic key using WOTS+, which gives us a node in the lowest tree. Additionally, we add the authentication path leading to the top root from that node, giving us the SPHINCS+ signature. In order to verify the signature, we use the authentication path, and we keep going up the trees until we get to the top root node, which is the public key. Then, we simply compare if the top root we got is identical to the known public key and if so, the message is authenticated. There are two important aspects to notice here: first, the whole tree is not present in the verification process, but only the nodes needed to get from the signed node to the root (so, for instance, if the node is on the right branch of the tree, considering its first two children, we only need the left child and not the whole tree resulting from that child). Secondly, the FORS public key and WOTS public keys are never explicitly verified, but rather used to construct the top root of the tree. Those are important aspects that reduce the time and space complexity of the scheme.

#### 2.1.5 SPHINCS+ Instantiation

We proceed to discuss the different parameter sets and implementations we use within it. The first two implementations we can talk about are the simple and robust versions. Each focuses on a different aspect of the scheme. While the simple version is more about speed, the robust version is more about security, in the sense that we have fewer security assumptions, so those two are two versions of the SPHINCS+, which balance the scheme's security and speed. Next, we have six options for the scheme, which uses different parameters to provide different security strengths as required by NIST. We are going to represent those options in the following table Table 2.1 where we have the following abbreviations, n - hash output length, h - the height of the hypertree, d - number of subtree layers,  $\log(t)$  -FORS tree height, k - Number of FORS Trees and w - Winternitz parameter.

|               | n  | h  | d  | $\log(t)$ | k  | w  | security bits | pk bytes | sk bytes | signature bytes |

|---------------|----|----|----|-----------|----|----|---------------|----------|----------|-----------------|

| SPHINCS+-128s | 16 | 63 | 7  | 12        | 14 | 16 | 133           | 32       | 64       | 7,856           |

| SPHINCS+-128f | 16 | 66 | 22 | 6         | 33 | 16 | 128           | 32       | 64       | 17,088          |

| SPHINCS+-192s | 24 | 63 | 7  | 14        | 17 | 16 | 193           | 48       | 96       | 16,224          |

| SPHINCS+-192f | 24 | 66 | 22 | 8         | 33 | 16 | 194           | 48       | 96       | 35,664          |

| SPHINCS+-256s | 32 | 64 | 8  | 4         | 22 | 16 | 255           | 64       | 128      | 29,792          |

| SPHINCS+-256f | 32 | 68 | 17 | 9         | 35 | 16 | 255           | 64       | 128      | 49,856          |

Table 2.1: SPHINCS+ Instantiation.

#### 2.2 Hash Functions

As mentioned above, SPHINCS+ is a hash-based signature scheme, which means that the main operations in this scheme are hashing. Therefore, it is important to explain how the hash functions used in this scheme work. In this thesis, we will consider the implementations of SPHINCS+ using both SHA2 and SHA3, more specifically SHA256 and SHAKE256, so in the next part, we will explain how each of those hashes works.

#### 2.2.1 SHA256

The first hash function we will discuss is SHA256, which is part of the SHA2 hash function family. As the name suggests, it is a more secure scheme comparing to its previous version of SHA1. This function is a standard by the National Institute of Standards and Technology (NIST) and was published in FIPS 180-2 [26], and since then, it was and still is widely used.

Now, we discuss how this function works. Given an input message, we divide it into values of 512-bit length and hash each block separately. Therefore, we are going to focus on the operations we perform on a single block. If we do not have 512 bits, we will pad the message to end up with a 512-bit value. The first thing we need to consider is the 8 constants that will initialize the hash values, let us note them by  $h_i$  where  $i \in \mathbb{N} \land i \in \{0, 1, ..., 7\}$ . We obtain those constants by taking the 32 first bits of the fractional parts of the square roots of the first eight primes. Those values are usually hardcoded in the code. The values, represented in hexadecimal, are as follow:

$\begin{array}{l} h_0 := 0x6a09e667\\ h_1 := 0xbb67ae85\\ h_2 := 0x3c6ef372\\ h_3 := 0xa54ff53a\\ h_4 := 0x510e527f\\ h_5 := 0x9b05688c\\ h_6 := 0x1f83d9ab\\ h_7 := 0x5be0cd19 \end{array}$

In addition to those constants, there are another 64 constants consisting of 32 bits each. We are going to place them in an array K, which has 64 entries of 32 bits each. Those constants are the first 32 bits of the fractional parts of the cube roots of the first 64 primes. Again, those constants are hardcoded into the code. The values of the constants, represented in hexadecimal, are: Now that we have established all the constants, it is time to start operating on the input. However, before that, let us define the following functions and their notation: 32-bit add (+), which adds two values of 32 bits, bitwise flip (not), which flips the 32-bit value given to it, bitwise or ( $\lor$ ), which takes two 32-bit values and returns the bitwise or between them bitwise and ( $\land$ ), which takes two 32-bit values and returns the bitwise and between them, rotate right ( $ROTR^n(x) = (x \gg n) \lor (x \ll w - n)$ , where w is the size of the word in bits), which takes a 32-bit value, x, and an integer n and rotates it to the right n times, rotate left ( $ROTL^n(x) = (x \ll n) \lor (x \gg w - n)$ , where w is the size of the word in bits), which takes a 32-bit value, x, and an integer n and rotates it to the left n times, shift right ( $x \gg n$ ), which takes a 32-bit value and an integer n and shifts it to the right n times and shift left ( $x \ll n$ ), which takes a 32-bit value and an integer n and shifts it to the left n times.

The following steps happen for each chunk of 512 bits. We start by initializing an array W with 64 entries, each being 32 bits. The first 16 elements (W[0..15]) are our 512 bits input and the rest, for now, will be 0. Then, we perform the following:

**Algorithm 4** Sigmas computation, initializing W

1: function SIGMAS(W)for i = 16 to 63 do 2: 3:  $x_1 \leftarrow i - 15$  $x_2 \leftarrow i - 2$ 4:  $s_0 \leftarrow ROTR^7(W[x_1]) \oplus ROTR^{18}(W[x_1]) \oplus (W[x_1] >> 3)$ 5: $s_1 \leftarrow ROTR^{17}(W[x_2]) \oplus ROTR^{19}(W[x_2]) \oplus (W[x_2] >> 10)$ 6:  $W[i] \leftarrow W[i-16] + s_0 + w[i-7] + s_1$ 7: end for 8: 9: end function

Next, we are going to copy the values of the constants of  $h_i$  to new variable denoted from a to h such that  $a = h_0$ ,  $b = h_1$  and so on. Then we are going to perform the following:

Algorithm 5 SHA256 rounds

| 1: function $ROUNDS(a, b)$            | (c, d, e, f, g, h, W, K)                        |

|---------------------------------------|-------------------------------------------------|

| 2: <b>for</b> $i = 0$ to 63 <b>do</b> |                                                 |

| 3: $S_0 \leftarrow ROTR^2(a$          | $) \oplus ROTR^{13}(a) \oplus ROTR^{22}(a)$     |

| 4: $S_0 \leftarrow ROTR^2(a$          | $) \oplus ROTR^{13}(a) \oplus ROTR^{22}(a)$     |

| 5: $S_1 \leftarrow ROTR^6(e)$         | $) \oplus ROTR^{11}(e) \oplus ROTR^{25}(e)$     |

| 6: $ch \leftarrow (e \land f) \oplus$ | $(not(e) \land g)$                              |

| 7: $maj \leftarrow (a \land b) \in$   | $\oplus \ (a \wedge c) \ \oplus \ (b \wedge c)$ |

| 8: $temp_1 \leftarrow h + S_1$        | + ch + K[i] + W[i]                              |

| 9: $temp_2 \leftarrow S_0 + n$        | naj                                             |

| 10: $h \leftarrow g$                  |                                                 |

| 11: $g \leftarrow f$                  |                                                 |

| 12: $f \leftarrow e$                  |                                                 |

| 13: $e \leftarrow d + temp_1$         |                                                 |

| 14: $d \leftarrow c$                  |                                                 |

| 15: $c \leftarrow b$                  |                                                 |

| 16: $b \leftarrow a$                  |                                                 |

| 17: $a \leftarrow temp_1 + ter$       | $np_2$                                          |

| 18: <b>end for</b>                    |                                                 |

| 19: end function                      |                                                 |

Next, we are going to add the 8 constants to the values we obtained for a, b, c, d, e, f and g one last time:

$h0 = h_0 + a$   $h1 = h_1 + b$   $h2 = h_2 + c$  $h3 = h_3 + d$   $h4 = h_4 + e$  $h5 = h_5 + f$  $h6 = h_6 + g$  $h7 = h_7 + h$

Finally, we concatenate all the  $h_i$  and we got the hashed value.

#### 2.2.2 SHAKE256

The second hash function that we will discuss is SHAKE256, a hash function from the function family SHA3, or more precisely, the Keccak family. This function is an improvement to the SHA2 family of functions in terms of security, but not only. Unlike the previous versions of SHA, which were fixed digest length, this version allows us to modify the output size to any number of bits. This function became a standard by the National Institute of Standards and Technology (NIST), published in FIPS 202 in 2015 [28] and it is the latest version of the SHA family of functions.

The first aspect we will discuss while talking about SHAKE256 is the parameters. In order to decide on the size of the state, we have parameter  $b = 25 \times 2^{l} = \{25, 50, 100, 200, 400, 800, 1600\}$ . In the case of SHAKE256, the state size is 1600. After we have chosen a state size, we determine the number of rounds,  $Rounds = 12 + 2 \times l$ . So, for instance, for a state size of 1600 like in SHAKE256, we have l = 6, so we have 24 rounds. Another important parameter is the w parameter, which is equal to w = b/25. We will use this parameter when writing the dimensions of the state, which are 5 by 5 by w. Next, we can talk about the rate denoted by r and the capacity denoted by c, the values are such that r + c = b. Those two variables are different for each member of the SHA3 family and in our case, for SHAKE256, the values are r = 1088 and c = 512. As we can see, adding those two will give us 1600, which is our state size.

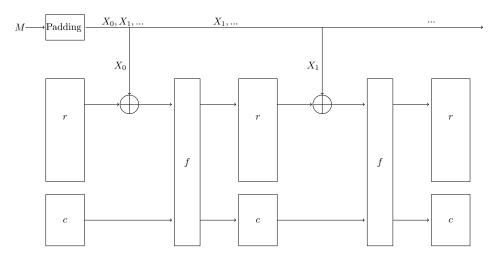

Before we dive deeper into understanding how SHAKE256 works, we will see a more general diagram that shows us how Keccak works. Keccak is also known as a sponge function, this is due to the way we can split it into two parts, the absorbing phase and the squeezing phase. In Figure 2.7 below, we are going to look at how the absorbing phase works.

Figure 2.7: Illustration of the absorbing phase of Keccak.

In Figure 2.7 we can see the absorbing phase of a message M, which is the first phase in its hashing. The first step is to add padding, such that the length is divisible by r. Then we XOR r bits from the message with the values of r. Notice that the initial values of r and c are 0's. Then we add to those r bits the additional c and perform the permutation operations on it, which are called f, representing the rounds discussed earlier. We will perform these operations until we have covered all the input from message M. This is known as the absorbing phase, because using the input M we create, "absorbed", our state and we repeat this, until we have "absorbed" the whole input. Afterward, we will "squeeze" the state into output. Next, we are going to look at how the squeezing phase works.

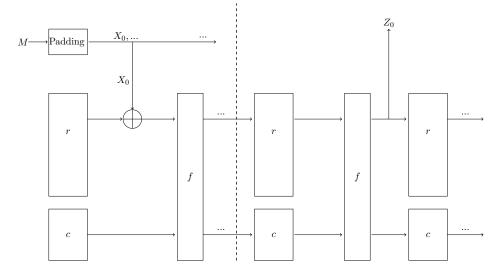

Figure 2.8: Illustration of the squeezing phase of Keccak.

On the left side, we can see the absorbing phase we talked about above and on the right hand, we can see the squeezing phase. In the squeezing phase, we take the state (r and c) that we got from the absorbing phase, run the f function on it again, and take the resulted r to be the output. As mentioned above, we can get the output size to be as we wish. This is done by squeezing until we get the amount of Z's needed. If we want less output than the length of r, we will take the first x-bits out of the  $Z_0$ , where xis the length needed. The idea for the name squeezing is because after we absorbed the input, we can "squeeze" as much output as we want from the state.

After understanding the absorption and squeezing phases, we need to comprehend how the f function from above works. As we can see from the Figures 2.7 and 2.8 above, it takes as input a state which in the case of SHAKE256 is 1600 bits, and it returns a state of the same length. This state is an array of b bits with dimension 5 by 5 by w and it is going to be denoted by A, while the output state will be denoted as A'. Now, the f function is built up out of 5 smaller functions denoted by  $\theta, \rho, \pi, \chi$  and  $\iota$ . Next, we will explain how each of them works and then see how we can combine them to create one round of function f, as explained in [28]. Recall from above that we mentioned that depending on the chosen value of l, we have different number of rounds in each call to f. In the next definitions we are going to denote the array as an array of x by y by z, where we know that  $x \in \{0, 1, 2, 3, 4\}, y \in \{0, 1, 2, 3, 4\}$  and  $z \in \{0, 1, 2, ..., w - 1\}$ . Another term we will use throughout those definitions is the lane, lane is a sub-array of w bits with constant x and y coordinates. Now that we have covered all the terms and notations, we can explain how the smaller functions work.

First is the  $\theta$  function, the idea is to XOR each bit in the state with the parities of two columns in the state. We do that as follows:

**Algorithm 6** The  $\theta$  function, SHAKE256

1: function THETA(A, w)for x = 0 to 5 do 2: for z = 0 to w do 3:  $C[x,z] \leftarrow A[x,0,z] \oplus A[x,1,z] \oplus A[x,2,z] \oplus A[x,3,z] \oplus$ 4: A[x,4,z]end for 5:end for 6: for x = 0 to 5 do 7: for z = 0 to w do 8:  $D[x, z] \leftarrow C[(x-1) \mod 5, z] \oplus C[(x+1) \mod 5, (z-1)]$ 9:  $\mod w$ end for 10: 11: end for for x = 0 to 5 do 12:for y = 0 to 5 do 13:for z = 0 to w do 14: $A'[x, y, z] \leftarrow A[x, y, z] \oplus D[x, z]$ 15:end for 16:end for 17:18: end for 19:return A' 20: end function

Next, we are going to talk about  $\rho$ , the idea behind this function is to rotate the bits of each lane by a length, called the offset, which depends on the fixed x and y coordinates of the lane. We perform that as follows:

Algorithm 7 The  $\rho$  function, SHAKE256

| 1:  | function $RHO(A, w)$                                  |

|-----|-------------------------------------------------------|

| 2:  | for $z = 0$ to $w$ do                                 |

| 3:  | $A'[0,0,z] \leftarrow A[0,0,z]$                       |

| 4:  | end for                                               |

| 5:  | $(x,y) \leftarrow (1,0)$                              |

| 6:  | for $t = 0$ to 23 do                                  |

| 7:  | for $z = 0$ to $w$ do                                 |

| 8:  | $A'[x,y,z] \leftarrow A[x,y,(z-(t+1)(t+2)/2) \mod w]$ |

| 9:  | end for                                               |

| 10: | $(x,y) \leftarrow (y,(2x+3y) \mod 5)$                 |

| 11: | end for                                               |

| 12: | return A'                                             |

| 13: | end function                                          |

Now, we are going to talk about the  $\pi$  function. In this function, we are going to rearrange the positions of the lanes. We are performing this as follows:

**Algorithm 8** The  $\pi$  function, SHAKE256

| 1:  | : function $PI(A, w)$                   |          |                 |

|-----|-----------------------------------------|----------|-----------------|

| 2:  | for x = 0 to 5 do                       |          |                 |

| 3:  | for y = 0 to 5 do                       |          |                 |

| 4:  | $for \ z = 0 \ to \ w \ d$              | lo       |                 |

| 5:  | $b: \qquad \qquad A'[x,y,z] \leftarrow$ | A[(x+3y) | $\mod 5, x, z]$ |

| 6:  | end for                                 |          |                 |

| 7:  | end for                                 |          |                 |

| 8:  | end for                                 |          |                 |

| 9:  | e return A'                             |          |                 |

| 10: | e end function                          |          |                 |

Next on the list is the  $\chi$  function, the effect of this function is to XOR each bit with a nonlinear function of two other bits in its row. We perform this as follows:

Algorithm 9 The  $\chi$  function, SHAKE256 1: function CHI(A, w)for x = 0 to 5 do 2: for y = 0 to 5 do 3: 4: for z = 0 to w do  $A'[x, y, z] \leftarrow A[x, y, z] \oplus$ 5: $((A[(x+1) \mod 5, y, z] \oplus 1) \cdot A[(x+2) \mod 5, y, z])$ 6: 7: end for end for 8: end for 9: return A' 10: 11: end function

Note that the dot  $(\cdot)$  represents integer multiplication.

Finally, we got to the last function  $\iota$ , but before we can define this function we are going to define another function which we will use in the definition of  $\iota$ . Let us call this function rc. rc receives an integer denoted by t and returns a one-bit value. The function rc is defined as follows:

Algorithm 10 The *rc* function, SHAKE256

```

1: function RC(t)

if t \mod 255 == 0 then

2:

3:

return 1

end if

4:

R \leftarrow [1, 0, 0, 0, 0, 0, 0, 0]

5:

for i = 1 to t \mod 255 do

6:

R \leftarrow 0 \mid\mid R

7:

R[0] \leftarrow R[0] \oplus R[8].

8:

R[4] \leftarrow R[4] \oplus R[8].

9:

R[5] \leftarrow R[5] \oplus R[8].

10:

R[6] \leftarrow R[6] \oplus R[8].

11:

R = Trunc_8[R]

12:

13:

end for

return R[0]

14:

15: end function

```

Note that the bars (||) represent concatenation and  $Trunc_i(x)$  is a function that returns the first and the i - 1 (last) bits of x.

Now, we can define the  $\iota$  function, the idea of this function is to modify some of the bits of lane (0,0) in a manner that depends on the round index  $i_r$ . This means that, unlike the previous function, this function apart from the state also gets the round index. We define the function as follows:

#### **Algorithm 11** The $\iota$ function, SHAKE256

| 1:  | function $IOTA(A, i_r)$                       |

|-----|-----------------------------------------------|

| 2:  | for $x = 0$ to 5 do                           |

| 3:  | for $y = 0$ to 5 do                           |

| 4:  | for $z = 0$ to $w$ do                         |

| 5:  | $A'[x,y,z] \leftarrow A[x,y,z]$               |

| 6:  | end for                                       |

| 7:  | end for                                       |

| 8:  | end for                                       |

| 9:  | $RC \leftarrow [0, 0,, 0] $ (w times)         |

| 10: | for $j = 0$ to $len(i_r) - 1$ do              |

| 11: | $RC[2^j - 1] \leftarrow RC(j + 7 * i_r)$      |

| 12: | end for                                       |

| 13: | for $z = 0$ to $w$ do                         |

| 14: | $A'[0,0,z] \leftarrow A'[0,0,z] \oplus RC[z]$ |

| 15: | end for                                       |

| 16: | return A'                                     |

| 17: | end function                                  |

After we have covered all the functions that make up a round, we can properly define a round. Each round is given a state array A and a round index  $i_r$ , so we define a round as:

$round(A, i_r) = \iota(\chi(\pi(\rho(\theta(A)))), i_r).$

Now, after we understand how a round works and how the absorption and squeezing work, we have a complete image of how SHAKE256 works. We first absorb the input as explained above, then perform the round function 24 times and squeeze the output to a 256-bit value.

#### 2.3 Intel Advanced Vector Extensions 512

Today, we can find different applications in non-computer-science-related fields which require the use of supercomputers [34] [38]. As a result, scientists are looking at different methods to increase the performance of computers, which will allow us to do more operations per unit of time (let it be minute, second or cycle). In order to achieve such improvements, it is a common practice to use parallelism, meaning executing multiple tasks at the same time. There are three main methods of parallelism in today's architecture and software: multi-core [14], multi-threading [37] and single instruction multiple data vectorization. Each of those methods works on a different CPU level and allows it to perform multiple tasks at once. Before we start discussing Intel Advanced Vector Extensions 512, we first discuss the parallel approach it uses.

#### 2.3.1 Single Instruction Multiple Data

AVX-512 uses the Single instruction multiple data (SIMD) vectorization parallel approach. In this case, the idea is to increase the size of the registers such that instead of containing a single value, it will contain a vector consisting of multiple values. Operations on this vector will be performed the same way as operations on one register, as all the values are in one register. For instance, let us say we have eight floats, each of 32 bits and we want to add four of them to the other four. If we do that in sequence, having two registers, each with a size of 32 bits, it will take us four operations to complete the task. However, if instead of two registers of 32 bits, we will have two registers with 128 bits, then we can fill each register with four floats values and add those two registers. So, we will only need one operation in order to add all the floats, instead of four. This way, we can work in parallel within the same thread, using just the registers available.

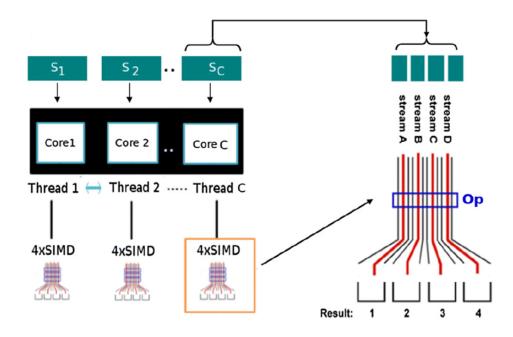

Figure 2.9: An illustration of different parallel approaches, Figure reprinted from [20].

For a better understanding of the differences between the approaches the following example is given. In Figure 2.9 we can see an illustration of all three approaches on one task. Let us say we have Task T which can be broken into C different tasks denoted by  $S_i$ , where  $i \in \mathbb{N} \land i \in \{1, 2, ..., C\}$  such that each core,  $Core_i$  is assigned one task to perform. After that, we can further break down each task  $S_i$  into another C sub-tasks  $Thread_i$ , which can be done by each thread and communicated within the same core to result in the final task  $S_i$ . Then, each thread needs to perform different operations on different variables, which can again be done in parallel. As we can see in Figure 2.9 on the right, each operation is carried out on four different streams, which is the same idea as operating on the floats, as discussed above.

#### 2.3.2 Intel Advanced Vector Extensions 512

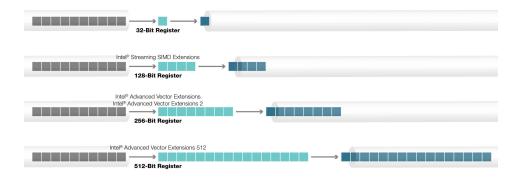

Now, that we know the different parallelism methods, we can talk about Intel Advanced Vector Extensions 512, also known as AVX-512. AVX-512 is an extension that implements the SIMD vectorization approach. However, before we can understand the benefits of AVX-512, we will first look at the previous implementation of AVX. The first implementation in this series is AVX, which was an improvement for the known SSE, AVX has a register size of 256 bits and limited Intel operations set [21]. Afterward, Intel introduced AVX-2, which has the same register size of 256 bits but additional operations, which allows us to not only work on 256 bits register but also run more sophisticated operations [17]. Lastly, AVX-512 extended the register size again to 512 bits, extended the number of registers from 16 to 32 and added additional instruction sets for more complex operations [11].

Figure 2.10: Comparison of different version of AVX and traditional register size, Figure reprinted from [36].

In order to see the differences in scale, we can look at Figure 2.10 which illustrates the differences in register size between the different versions of AVX and the traditional register size.

As mentioned above, in each version of AVX, Intel introduces more powerful instruction sets. When discussing the hashes in Section 2.2, we have seen that we need some logic and arithmetical operations to hash values. When comparing AVX2 and AVX-512, we can see that new operations, such as the rotate intrinsic, can help us speed up the performance of hashing. Also, we can use the ternary logic operation to boost the performance of logic operations on three values. More about those benefits will be discussed in Section 6.2 where we explain the motivation for the results we got.

Another benefit of AVX-512 comparing to previous versions is the increase in the number of registers. While in the previous version, AVX2, there were only 16 registers in AVX-512, there are 32 registers, allowing us to keep more data in memory. Later in Section 6.2 we will see how this helps us to improve the performance of our scheme.

To conclude this section, it can be seen that the new AVX-512 has some advantages over its predecessors. Those advantages can help boost the speed of a program, which will allow us to perform more tasks in a given unit of time.

## Chapter 3 Related Work

In this paper, we propose a new implementation of SPHINCS+ using AVX-512. By using AVX-512, we hope to optimize the performance in terms of speed for the SPHINCS+. In order to better understand our implementation and the possible optimization, we compare it to other implementations and analyze the results.

The first comparison that comes to mind is to compare it to the REF implementation proposed in [4]. However, we need to consider that this version is not optimized in terms of efficiency and is instead used as proof of concept for the SPHINCS+ scheme.

Another implementation of SPHINCS+ to which we can compare our results is the AVX2 implementation [39], which is also part of the code submitted to the third round of the NIST post-quantum competition [5]. By comparing those three implementations, we will better understand the different operations of the scheme and the benefit of using AVX-512. In addition, we will be able to grasp and understand which parts we are getting a meaningful improvement. For instance, if we expect AVX-512 to be twice as fast as AVX2 and observe that we only get an improvement of  $1.5 \times$  for some parts, we might think the implementation is not optimal. However, suppose we also see that we get an improvement of  $1.6 \times$  for the same parts comparing to the REF and AVX2, it will become clear that it is not about the implementation not being optimal enough or due to overhead, but rather due to parts that cannot benefit from the use of this type of parallelism.

As we mentioned above, SPHINCS+ is a candidate in the NIST postquantum competition, [25]. It is one of the alternative schemes of the third round for the Digital Signature Algorithms competition. Therefore, we are going to end the last section with a comparison to the other five NIST candidates. It is important to mention that, unlike our implementation, the other implementations are not optimized for AVX-512. However, as they are all part of the NIST post-quantum competition, it is still essential to see the different performances for each candidate and compare them to our implementation. For this comparison, we are going to use SUPERCOP [3] which has the implementation of the other candidates. SUPERCOP is toolkit used to measure the performance of cryptographic software. Also, we are going to integrate our implementation into SUPERCOP, in order to make the comparison as fair as possible. Next, we are going to introduce each one of the candidates.

There are two lattice-based post-quantum signature schemes, CRYSTALS-DILITHIUM [22] and FALCON [13], two multivariate based post-quantum signature schemes, Rainbow [19] and GeMSS (A Great Multivariate Short Signature) [10] and one other scheme, Picnic [41]. Unlike the other schemes, Picnic is not based on number-theoretic or structured hardness assumptions, but rather on zero-knowledge proofs, where Alice convinces Bob that she knows a secret without revealing any information about the secret. It uses this idea together with symmetric cryptography, hash functions, and block ciphers.

Apart from those schemes, which we will compare to our implementation, there is another implementation we should acknowledge. As mentioned above, SPHINCS+ uses SHAKE256 as one of its hash functions. For that purpose, we used the eXtended Keccak Code Package for AVX-512, which was written by the Keccak team [40] and further discussed in [7]. It is an optimized version of Keccak for AVX-512, and we used its implementation of the 24 rounds (the f function) on the state array in our proposed implementation.

# Chapter 4 Optimizing SPHINCS+

As we have seen in Section 2.1, where we explain how the SPHINCS+ scheme works, the main operations we are performing are creating the keys, signing a message, and verifying a signature. It should not be a surprise that the main operation in a hash-based scheme is hashing. Therefore, if we want to optimize the speed of the scheme, we will have to focus on improving the performance of hashing, and later on, combine this new version of hashing in the calls of the scheme. That is why it is essential to understand how the hashes work, as we explained in Section 2.2. As we have seen in Section 2.1, we have  $a \cdot 2^{h'}$  leaves in our tree, and each one of them is using hashes that are independent of each other, meaning that the hash value of one of the leaves is not dependent on the hash value of another leaf. Therefore, we can parallelize them by hashing different leaves simultaneously, which would speed up the performance. It is important to mention that this approach is already present in another implementation of the SPHINCS+ code [39]. However, in that case, they used an older version of the AVX family, AVX2, while in this thesis, we are using the newer version AVX-512. This proposed implementation works the same way as the original scheme, which implies it does not affect its security, but only improves upon its speed by performing a similar operation on the hash values, using the AVX-512 as we saw in Section 2.3.1, when we talked about SIMD vectorization. Below, we will explain this idea further and see how each hash is implemented, using AVX-512 in our implementation of SPHINCS+. As we have seen in Section 2.1.5, SPHINCS+ has two types of implementation: the simple version, which focuses on speed, and the robust version, which provides a more secure version. However, for simplicity, in this section, we do not go into details about either of them, but rather explain how we improved their main operations. For more details, see the code [1].

#### 4.1 SHA256 Implementation

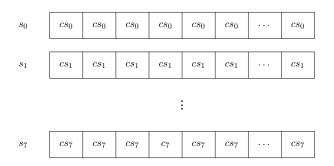

Let us start by explaining how we implemented SHA2 (SHA256) using AVX-512. Similar to what we saw in Section 2.2.1 we will follow those steps, but instead of hashing one value at the time, we are going to hash 16 values at the time. Since we are working with 32-bit values for SHA256, and as we know that AVX-512 has a register size of 512 bits, we can work on 512/32 = 16values at once. Therefore, in the code, [1] we can see the x16 added to some of the function and file names to emphasize that their idea is the same, but they perform 16 hash values at one call. Now, we are working with 32-bit values and as we have seen in Section 2.2.1 we have eight values we are working with  $(a, b, \ldots, h)$ . This means that we have  $32 \cdot 8 = 256$ -bit values which we work with for one hash value. In order to work with the 512-bit registers, two of those 256-bit values are placed within one register. This is done as follows: hash values 0 through 7 are placed in the first part of the register and hash values 8 through 15 are placed in the second part of the register, as shown in Figure 4.1. Next, we are going to explain how we perform the hashing on 16 values at once.

Figure 4.1: Illustration of the ordering of the 16 hash values in the registers.

As explained above, we are going to store the 16 values in 8 registers, for convenience, an array, called s, of eight entries each of 512 bits is used. As expected, the first step in hashing is initializing the array with the SHA256 constants. Since there are 16 values hashed at once, there are sixteen values of each constant. As each constant is 32 bits and we have a 512-bit

register, this fits perfectly. For an illustration of the code, the initialization part is given in Figure 4.2, where  $_m512\_set1\_epi32$  is an Intel intrinsic for broadcasting the value given to the register as a 32-bit value.

```

void sha256_init16x(sha256ctx *ctx) {

ctx->s[0] = _mm512_set1_epi32(0x6a09e667);

ctx->s[1] = _mm512_set1_epi32(0xb67ae85);

ctx->s[2] = _mm512_set1_epi32(0x3c6ef372);

ctx->s[3] = _mm512_set1_epi32(0xa54ff53a);

ctx->s[4] = _mm512_set1_epi32(0x510e527f);

ctx->s[5] = _mm512_set1_epi32(0x9b05688c);

ctx->s[6] = _mm512_set1_epi32(0x1f83d9ab);

ctx->s[7] = _mm512_set1_epi32(0x5be0cd19);

ctx->datalen = 0;

ctx->msglen = 0;

}

```

Figure 4.2: The initialization of array s.

For a better illustration of how the  $_m512\_set1\_epi32$  intrinsic works in Figure 4.2 we are also given an example of how the registers would look like in Figure 4.3 where  $cs_i$  refers to the constants such that  $cs_0 = 0x6a09e667$ ,  $cs_1 = 0xbb67ae85$ , ...,  $cs_7 = 0x5be0cd19$ .

Figure 4.3: Illustration of the ordering of the constants in s, where we have 16 values within one entry.

The next step is to upload the values we want to hash into an array of 512-bit values, called W, and transpose the data to correspond with the constants we filled in our *s* array. Then, we create functions that will perform the operations used in SHA256. We start with computing the values for W using the sigmas, as we saw in 2.2.1. In the code, these sigmas are called  $WSIGMA1\_AVX$  and  $WSIGMA0\_AVX$ . Below, in Figure 4.4 the

most significant functions used in this part are given.

Figure 4.4: Definition of s's functions for SHA256.

Then we have another function called  $SHA256ROUND_AVX$ , where we perform the S's , ch, maj, temp<sub>1</sub>, temp<sub>2</sub> and the a - h updates, which can be seen in Figure 4.5. Again, for readability, we only show the most relevant parts of the code.

Figure 4.5: Definition of SHA256ROUND\_AVX functions for SHA256.

For the MAJ and CH functions, we use a new intrinsic that allows us to perform fast logical operations on three values at once. To achieve that, we pass a constant as the last element, which specifies how to interpret the logical operation. For instance, for the XOR3, we pass the hexadecimal value 0x96, which in binary is 10010110, this value being the result of the truth table of the expression  $a \oplus b \oplus c$ . The same values were calculated to give the equivalent results for the MAJ and CH.

After executing those functions, we add the constants one last time, and we get the hashed values in s. However, before extracting the values, we transpose them again in order to get them in the order needed for extraction. Then we simply extract them.

#### 4.2 SHAKE256 Implementation

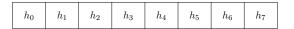

Moving on, we will explain how SHA3, SHAKE256, is implemented using AVX-512. Similar to the case of SHA256, we follow the steps from Section 2.2.2, but instead of performing hashing on one value at the time, we are going to hash eight values at once. The idea here is that we are working on 1600 bits state that is split into 25 lanes, so our w is 64, which means that we have 25 lanes of size 64 bits. So, using the AVX-512, we can perform 512/64 = 8 hashes simultaneously, hence the eight values at once.

For this part, we used an existing Keccak implementation for AVX-512, [40] which was optimized by the Keccak team. This idea is similar to the SHA256 version above: we pass eight values and we run the functions on them simultaneously. As expected, we start with a zero state, then we initialize the state array with the values such that we place eight values of 64 bits in a 512 bits entry of the state. So, the state will look like Figure 4.6.

Figure 4.6: Illustration of the ordering of the initial values in one register of 512 bits where h represents the initial 64-bit values.

We have the state, which is represented as an array of 25 entries of 512-bit values called state, and in the initialization, we upload the values in the same way as shown in Figure 4.6. The code for this part can be seen in Figure 4.7.

Figure 4.7: Initialization of the state of SHAKE256.

After we initialize the state with our input and fill the state array with the corresponding values, we can run the f functions. This means that we are going to run the 24 rounds on the state array. For that, we are using the function *KeccakP1600times8\_PermuteAll\_24rounds*, which is taken from the Keccak implementation for AVX-512 [40]. In that function, we perform all the smaller functions we discussed in Section 2.2.2. Depending on the scenario, we either run this function once or until we are done with the absorption and squeezing phases. After the hashing, we extract the first 256 bits of the values, as shown in Figure 4.8.

```

__m256i_u take1, take2;

for (int i = 0; i < 8; i++) {

(take1) = _mm512_extracti64x4_epi64(state[i],0);

(take2) = _mm512_extracti64x4_epi64(state[i],1);

((int64_t*)out0)[i] = _mm256_extract_epi64(take1, 0);

((int64_t*)out1)[i] = _mm256_extract_epi64(take1, 1);

((int64_t*)out2)[i] = _mm256_extract_epi64(take1, 2);

((int64_t*)out3)[i] = _mm256_extract_epi64(take1, 3);

((int64_t*)out4)[i] = _mm256_extract_epi64(take2, 0);

((int64_t*)out5)[i] = _mm256_extract_epi64(take2, 1);

((int64_t*)out6)[i] = _mm256_extract_epi64(take2, 2);

((int64_t*)out6)[i] = _mm256_extract_epi64(take2, 2);

((int64_t*)out7)[i] = _mm256_extract_epi64(take2, 3);

}

```

Figure 4.8: Extracting the hashed values from the state array.

## Chapter 5

# A Lower Bound on the Amount of Cycles per Hash

As mentioned above, we are going to use AVX-512 in order to optimize the implementation of SPHINCS+. The idea will be to measure the execution time using clock cycles and compare the implementation proposed in this thesis to other implementations. However, before talking about optimization and asking to what extent we can improve the speed of the scheme, we will first look at the theoretical improvement that can be gained from using the AVX-512. In order to do so, we are going to derive a lower bound on the amount of cycles per one hash. As SPHINCS+ is a hash-based scheme, most of the execution time is spent on hashing. Therefore, it is important to see how many cycles it takes to perform one hash. By doing so, we will better understand the improvement and see the limitations of using the AVX-512. It is also important to distinguish between the theoretically expected speed up and the practical one. In theory, we should be able to derive the amount of cycle it takes to perform a hash. However, this is not always the case in practice, as running the code will give us a different amount of cycles compared to the theoretical one. This is due to the differences in communication and execution of the CPU, which is not taken into consideration when calculating the theoretical amount of cycles and due to different optimizations done by the CPU. Therefore, we are going to name the derived amount of cycles the lower bound on the amount of cycles rather than the expected amount of cycles. Notice that we will only calculate the amount of cycles that it takes to compute the hash of a value and not the amount of cycles of other operations, such as loading the values to the registers, copying them to variables, etc.

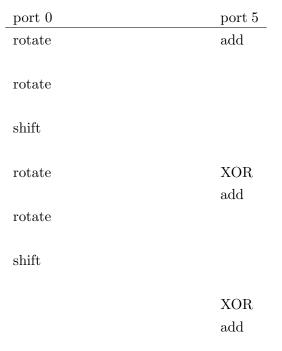

After we have discussed the meaning and motivation behind deriving the lower amount of cycles, we are going to calculate it. To do so, we will use our implementation together with the fourth Software Optimization Resources manual [12] and Intel intrinsics guide [18], which will provide us with the throughput of the operations we perform in order to hash. We are using the throughput and ports given for the Skylake microarchitecture.