#### BACHELOR THESIS COMPUTING SCIENCE

RADBOUD UNIVERSITY

# Blueprints for out-of-core code generation using CUDA

Author: Patrick van Beurden s1003725 First supervisor/assessor: Prof. dr. Sven-Bodo Scholz svenbodo.scholz@ru.nl

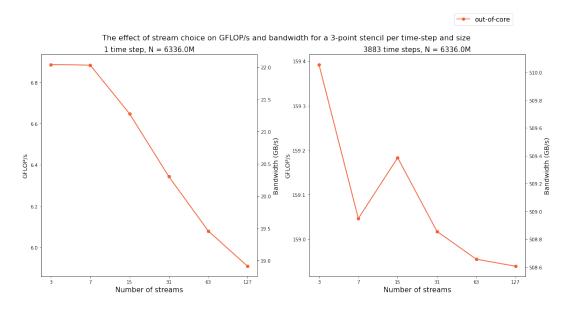

> Second assessor: Dr. Pieter Koopman pieter@cs.ru.nl

June 23, 2022

#### Abstract

Most parallel computing systems today are a combination of a central processing unit (CPU) and one or more graphics processing units (GPUs). Both types of devices maintain their own dynamic RAM (DRAM), but the average amount available to each typically varies significantly. Whereas it is relatively inexpensive to have 64, 128 or even 256 gigabytes of DRAM available to the CPU, a lot of high-end GPUs only have 8 to 16 gigabytes to work with. This discrepancy limits the data complexity of algorithms that can benefit from GPU acceleration.

It is possible to rewrite an algorithm in such a way that the data it processes does not have to fit the GPU memory in one go. However, doing this manually is error prone and complex, so we are looking into ways to automate this process. Hence, this paper is meant as a stepping stone for generating data size agnostic code for map-like operations, such as vector addition, and (3-point) stencil computations using NVIDIA's CUDA.

# Contents

| 1        | Intr         | roduction                                   | 3               |

|----------|--------------|---------------------------------------------|-----------------|

| <b>2</b> | Bac          | kground                                     | <b>5</b>        |

|          | 2.1          | CUDA                                        | 5               |

|          |              | 2.1.1 What is CUDA?                         | 5               |

|          |              | 2.1.2 Programming model                     | 6               |

|          |              | 2.1.3 Threading model                       | $\overline{7}$  |

|          | 2.2          | Asynchronous memory transfers               | 9               |

|          | 2.3          | Tiling                                      | 11              |

|          |              | 2.3.1 Map-like operations                   | 11              |

|          |              | 2.3.2 Stencil computations                  | 12              |

| 3        | Out          | t-of-core code generation                   | 15              |

| 0        | 3.1          | Map-like operations                         | 15              |

|          | 0.1          | 3.1.1 In-core                               | 15              |

|          |              | 3.1.2 In-core streamed                      | 16              |

|          |              | 3.1.3 Out-of-core                           | 21              |

|          | 3.2          | 3-point stencil computations                | 27              |

|          | 0.2          | 3.2.1 In-core                               | 27              |

|          |              | 3.2.2 In-core streamed                      | $\frac{-1}{28}$ |

|          |              | 3.2.3 Out-of-core                           | $\frac{1}{35}$  |

| 4        | Per          | formance evaluation                         | 41              |

| -        | 4.1          | Experimental setup                          | 41              |

|          | 4.2          | Map-like operations                         | 44              |

|          | 4.3          | 3-point stencil computations                | 48              |

| 5        | Rol          | ated Work                                   | 51              |

| 0        | 5.1          | Asynchronous memory transfers               | 51              |

|          | $5.1 \\ 5.2$ | Optimizing stencil computations for the GPU | 51              |

|          | $5.2 \\ 5.3$ | Code generation for streaming arrays        | 52              |

|          | $5.3 \\ 5.4$ | Out-of-core stencil computations on the GPU | 52<br>52        |

|          | J.4          | out-of-core stellen computations on the GFU | 52              |

| 6        | Cor          | nclusions                                   | <b>54</b>       |

|          | 6.1          | Future work                                 | 55              |

| Α | App | endix                        | 60 |

|---|-----|------------------------------|----|

|   | A.1 | Even trapezoids              | 60 |

|   | A.2 | Odd trapezoids               | 67 |

|   | A.3 | Code for performance metrics | 72 |

# Chapter 1 Introduction

GPUs are known for their high memory bandwidth, fast computation speed and relatively low energy cost for high parallelism. These attributes make them especially attractive for performing algorithms that can process large blocks of data in parallel. Not surprisingly, GPUs are increasingly being used for high performance computing and data-intensive scientific applications such as weather forecasting [16], physics simulations [7] and machine learning [25].

In order to take advantage of the large computational power of a GPU, the data required for a given algorithm first needs to be transferred to the device's dedicated memory. Currently, most high-end GPUs only have between eight and sixteen gigabytes of space available, whereas the main memory of a modern parallel computing system can easily be several hundred gigabytes. Unfortunately, this discrepancy limits the problem size of applications that can benefit from GPU acceleration.

The indicated memory problem relates to a similar challenge in the past when the data structures in use for purposes such as numerical linear algebra, scientific visualisation and computer graphics became too large to fit in the main memory of a computer. Consequently, research has been done on the development of algorithms [22, 27] that are designed to achieve high performance on the CPU when their data is stored in external memory. These type of algorithms are often referred to as *out-of-core* algorithms.

Lately, it has become increasingly more common that the memory available on the GPU for immediate computation is insufficient in size to keep the entire data in memory during the execution of an algorithm. As one might expect, the need for executing large problem domains in a distributed fashion on one or multiple GPUs has been a topic of recent research on stencil computations [12, 13, 23, 24]. However, creating a correct and efficient solution is non-trivial, because it usually involves multiple technologies and a lot of domain-specific knowledge.

This research looks at generating out-of-core code on the GPU for two

different types of common algorithms; map-like operations and (3-point) stencil computations. In order to achieve this, CUDA's asynchronous communication model is first used to concurrently process, or *stream*, chunks of data on the GPU when the data does fit. This *in-core* streaming method is then extended to realize out-of-core execution.

The main contribution of this paper are rewriting schematics, or *blueprints*, for in-core streamed and out-of-core code generation. My approach to establishing these blueprints is to first identify two commonly used algorithmic classes. From there, I manually investigate the respective challenges for creating out-of-core code for these algorithms. Finally, I look at the performance one can expect by implementing a simple variant of both algorithmic classes in C++. Ultimately, these blueprints could then function as a starting point for implementing streamed or out-of-core code generation in a domain-specific array language such as SaC [21].

In the second chapter of this report, the background for this research is covered. After that, chapter three presents the in-core specification, and based on that, the in-core streamed and out-of-core blueprints for both maplike operations and 3-point stencils in a C++-like pseudo-language. Next, chapter four evaluates the performance of the aforementioned blueprints when implemented in C++. Finally, chapter five discusses related work and chapter six contains the concluding remarks and possible future work.

### Chapter 2

## Background

#### 2.1 CUDA

In section 2.1, an introduction to CUDA is given by providing a brief description of CUDA and going over several technical details such as the programming model and the threading model. Figure 2.1 compares the addition of two vectors of a sequential C++ program and a possible CUDA counter part. Although the syntax of the CUDA program may still be unfamiliar at this point, it is further explained in subsections 2.1.1 through 2.1.3.

#### 2.1.1 What is CUDA?

CUDA is a parallel computing platform and programming model that allows programmers to utilise the computational power of GPUs. Its programming model emphasizes two important design goals, the first of which is to provide a low learning curve for programmers familiar with a supported programming language [4]. This is done by extending a standard language (e.g. C++) with a minimalist set of keywords for expressing parallelism [6]. The second goal is to allow for the design of highly scalable code [6] and an example of this is the concept of grids and (thread-)blocks, which will be discussed in more detail in subsection 2.1.3 of this chapter.

Furthermore, it was the first API that allowed for general purpose computing on GPUs (GPGPU), because prior to CUDA's release in 2007, the only alternatives were designed for graphics programming (e.g. openGL). This seems to be one of the reasons why CUDA applications are now commonly used for several different purposes such as medical imaging, computational fluid dynamics and environmental science [20].

Figure 2.1: A comparison of adding two vectors in a sequential program and in a (parallel) CUDA program.

#### 2.1.2 Programming model

First of all, CUDA programs are heterogeneous co-processing programs. This means that both a CPU and a GPU are involved in the execution of CUDA code. Each of these components are dedicated to their own specific task. The CPU, which is referred to as the *host*, executes the serial parts of the program and the GPU, which is referred to as the *device*, executes the parallel parts of the program. This kind of co-processing approach gives the best performance for parallel-intensive programs, but also many mostly-

sequential codes [18].

Furthermore, CUDA kernels are special functions that are executed N times in parallel by N different CUDA threads on the device [4]. They are defined using the "\_\_global\_\_" keyword and are called in the same manner as regular C++ functions, except that the amount of threads that will execute the kernel are specified with a special syntax: " $\langle \langle \langle ... \rangle \rangle \rangle$ ". Within a kernel, the programmer also has access to built-in variables, such as the thread ID of the executing thread.

Finally, the programming model assumes that both the host and the device have their own separate dynamic RAM (DRAM) [4], which are aptly referred to as the *host memory* and the *device memory*. In order for the device to operate on data from the host, the program first has to call for a memory transfer from the host to the device. When the device has finished its computation, the resulting data in turn is often transferred back to the host. For this purpose, CUDA provides the programmer with several runtime functions, of which "cudaMemcpy(...)" is one of them that is commonly used. It has four arguments: the destination buffer, the source buffer, the size of the data that should be transferred and the direction of the memory transfer (e.g. cudaMemcpyHostToDevice), respectively.

#### 2.1.3 Threading model

In order to leverage parallelism, it is important to understand CUDA's threading model. First, when launching a kernel, the programmer has to indicate by how many threads the kernel should be executed. All the executing threads requested at kernel launch are then grouped together in so-called blocks. These blocks can combine their threads together in several different shapes spanning up-to three dimensions, which is illustrated in figure 2.2. One reason why this is useful is that data belonging to a given algorithm usually has up-to three dimensions, so several blocks could then be combined to match the shape of the data, which in turn gives easy and predictable access to any element.

| Α | 1D      | inte      | ger      | arra      | ay o      | flen      | igth 6 | A matching 1D block of length 6 |           |           |         |          |           | ngth 6    |        |

|---|---------|-----------|----------|-----------|-----------|-----------|--------|---------------------------------|-----------|-----------|---------|----------|-----------|-----------|--------|

|   | 6       | 1         | 2        | 0         | 8         | 4         |        |                                 | 0         | 1         | 2       | 3        | 4         | 5         |        |

|   |         |           |          |           |           |           |        |                                 |           |           |         |          |           |           |        |

|   |         |           |          |           |           |           |        |                                 |           |           |         |          |           |           |        |

| A | 2D      | inte      | ger      | arra      | ay o      | fsiz      | e 2x6  | A m                             | atch      | ning      | 2D      | blo      | ck o      | fsiz      | ze 2x6 |

| A | 2D<br>6 | inte<br>1 | ger<br>2 | arra<br>0 | ay o<br>8 | fsiz<br>4 | e 2x6  | A m                             | atch<br>0 | ning<br>1 | 2D<br>2 | blo<br>3 | ck o<br>4 | fsiz<br>5 | ze 2x6 |

Figure 2.2: An example of two random shapes of input data and matching blocks of threads. The values in the blocks are the thread IDs.

The amount of threads in any of the three block dimensions can be specified

at launch, but the size limit in the x-dimension is 1024. All blocks combined form a so-called *grid*, which can also have up to three dimensions and has a limit of  $2^{31} - 1$  blocks in the x-dimension [4]. Each block in a grid executes independently and their order of execution cannot be guaranteed. This means that, currently, the only way of synchronizing blocks is by exiting the kernel. On the other hand, synchronization between threads within a block is possible using provided functions such as "\_\_syncthreads()".

As hinted at earlier, this model allows the programmer to consider a problem as a grid and divide it into smaller blocks of sub-problems that can be solved cooperatively by the threads in that block [4]. To illustrate this better, let us consider a common shape of input (and output) data: a vector of size N. There are many different algorithms that can be performed on this data type. For example, there might be a second input vector of size n that a programmer wants to add to the first vector.

In order to maximise parallelism, it would be ideal to request a thread for each element in the vector. In this case, a matching grid would then have (n + 128 - 1)/128 blocks with each block having 128 threads. Each thread in the grid now corresponds to exactly one index of the output vector (except for some threads in the last block if n is not divisible by 128). An appropriate kernel queries the thread ID of the executing thread and then performs the addition for the corresponding index. This can be implemented as shown in figure 2.3

```

1

__global__

\mathbf{2}

void add_vector(int n, float *a, float *b)

3

{

int index = blockIdx.x * blockDim.x + threadIdx.x;

4

int stride = blockDim.x * gridDim.x;

5

6

for (int i=index; i < n; i+=stride)

7

ł

a[i] = a[i] + b[i];

8

9

}

10

}

```

Figure 2.3: A CUDA kernel code example of vector addition.

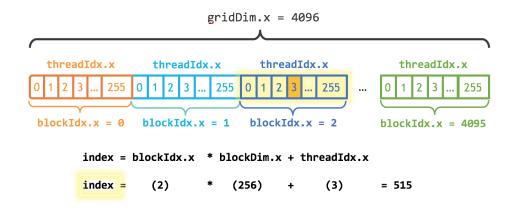

First, a variable "index" is created by using the keywords "blockIdx.x", "blockDim.x" and "threadIdx.x" that are provided by CUDA. The first keyword refers to the location of the executing thread's block within the grid, the second one refers to the size of each block and the third refers to the executing thread's position within its own block.

Unfortunately, situations might arise where the executing grid is not large enough, because of a bug or hardware limitations. In this case, some or all threads are responsible for the calculation of more than one index, with each of their indices separated in distance by the size of the grid. Therefore, a stride, which corresponds to the size of the grid, is calculated and a loop is used to prevent unintended behaviour, which is called a *grid-stride loop*<sup>1</sup>. Figure 2.4 gives a more visual and intuitive example of how the previous kernel calculates the index of the output vector corresponding to the executing thread.

Figure 2.4: In this example, the grid contains 4096 blocks and each block has 256 threads. When the third thread in the third block of this grid executes, its corresponding index in the vector is calculated as shown. See footnote 1 for figure source.

#### 2.2 Asynchronous memory transfers

The standard communication model in CUDA is synchronous, which means the memory transfers in figure 2.1 are also synchronous. Therefore, whenever a memory transfer is initiated, further execution on the *host* is blocked until the data transfer to the *device* has been completed.

Moreover, the device first copies the entire data from the host, then launches a kernel for the requested computation and afterwards it copies the resulting data back to the host. This entire process happens in what is referred to as the *default* (or *null*) stream. In general, a CUDA stream is a sequence of commands that execute in order [4].

Instead of only using the default stream, CUDA also support the notion of multiple streams. These different streams could then potentially be executed concurrently. Consequently, while the commands within one stream happen sequentially, the order in which they happen between streams is not guaranteed. Although this additional concurrency introduces an extra

<sup>&</sup>lt;sup>1</sup>https://developer.nvidia.com/blog/even-easier-introduction-cuda/

layer of complexity, it also allows for asynchronous interaction between the host and device. For example, an asynchronous alternative for the memory transfers in figure 2.1 can be implemented as shown in figure 2.5

```

1

cudaHostRegister(a, N*sizeof(float), 0);

\mathbf{2}

cudaStream_t stream;

3

cudaStreamCreate(&stream);

4

5

cudaMemcpyAsync(dev_a, a, N*sizeof(float),

\mathbf{6}

cudaMemcpyHostToDevice, stream);

7

kerne \ll blocks, block_n, 0, stream \gg (N, dev_a);

cudaMemcpyAsync(a, dev_a, N*sizeof(float))

8

9

cudaMemcpyDeviceToHost, stream);

10

cudaDeviceSynchronize();

```

```

Figure 2.5: An example of any nchronous communication in CUDA.

```

First, it is required to *pin* the host memory, which can be done with *cu-daHostRegister(..)* and is shown on line 1. This pinning page-locks the memory and prevents it from being swapped out [28], which is vital, because asynchronous transfers allow the GPU to directly access the host's main memory [4]. On lines 2-3, a stream that is different from the default stream is declared and created. Next, on lines 5 and 8 a new method is shown, namely, *cudaMemcpyAsync(..)*, which initiates a memory transfer in the specified *stream*. As one might expect, *cudaMemcpyAsync(..)* does not block the host until the memory transfer is finished, unlike *cudaMemcpy(..)*. Lastly, *cudaDeviceSynchronize()* is introduced on line 10 to actually ensure that the host is blocked till all prior commands have finished, so that race conditions are prevented.

In general, switching to asynchronous communication can improve data throughput and overall performance depending on the combination of hardware used, the size of the input data and the ratio between computation and communication [28].

As hinted at earlier, it is possible to leverage these asynchronous transfers for the purpose of creating multiple streams, which each transfer a portion, or *chunk*, of the entire vector. On top of that, one could also divide the kernel computation between the different streams, so that each stream independently (1) transfers data to the device, (2) launches a kernel on this subset of data and then (3) transfers the final result back to the host.

In theory, this leads to transfers and computations within a stream overlapping with the commands in other streams [4]. Overlapping communication and computation can lead to increased performance and can, for example, be used to more efficiently split a stencil computation between multiple GPUs [23, 24].

#### 2.3 Tiling

Using several streams to execute a given algorithm comes with a new challenge. Partitioning the input vector(s) into chunks of data and streaming them through the device will not produce the correct result if one stream is dependent on a value calculated by or assigned to another stream. Therefore, the key challenge is to find a partitioning scheme that does not violate any possible data dependencies.

Tiling is a strategy often used to both improve the data locality and to maximize parallelism of stencil computations [9]. I draw inspiration from this technique to make streaming, and ultimately out-of-core execution, possible for both map-like operations and stencil computations. Note that improving data locality in the context of out-of-core in recent work is also referred to as *temporal blocking* [5, 12, 24].

Several variants of tiling exist and the one preferred for a given stencil can depend on various factors such as dimensionality of the inputs, the processing device (i.e. CPU, GPU or both) and the memory architecture (i.e. shared or distributed). In this subsection, rectangular tiling [19] is introduced in the context of map-like operations, and, overlapped tiling [9, 19], [10, 11, 15] and split tiling [1, 8, 26] are introduced in the context of stencil computations.

#### 2.3.1 Map-like operations

In this paper, a map-like operation is an index-wise function application with one or multiple lists as input. For example, common list operations in functional programming languages such as *map* and *zip* can be considered map-like operations. Another example would be vector addition, since it essentially is index-wise addition of multiple lists (typically two).

In order to stream map-like operations, it is necessary to divide the input vector(s) between the streams, so that the outputs corresponding to the resulting chunks of data can be calculated independently. The work of P.S. Rawat et al. [19] shows rectangular tiling to illustrate that this approach would not work for stencil computations. However, it is perfectly suitable for map-like operations.

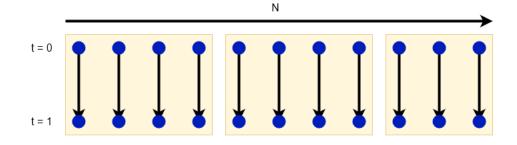

An example of rectangular tiling for map-like operations is shown in figure 2.6. The dots resemble values in a vector at different time steps t. The arrows show which values in time step 0 are necessary to calculate a value in time step 1. If the calculation of a value in a given tile does not depend on a value in another tile, then that portion of the data can be computed concurrently. Clearly, the rectangular tiles are independent in the case of map-like operations for any number of iterations.

Figure 2.6: An example of rectangular tiling with map-like operations.

#### 2.3.2 Stencil computations

An n-point stencil is a computational pattern that is iteratively applied on a k-dimensional data structure for several time steps. Stencil computations are used for a wide range of scientific and engineering disciplines [17] and have as a result been studied extensively in areas such as high performance computing, compilers and code generation [1, 8, 9, 10, 11, 15, 17, 19, 23, 24, 26].

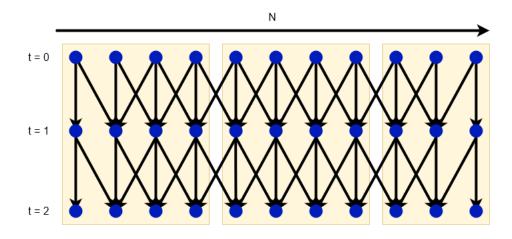

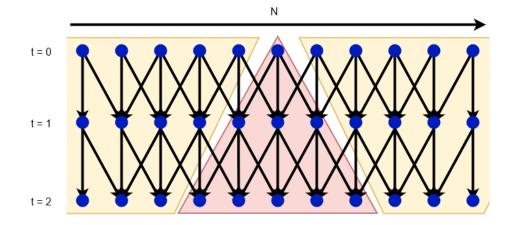

Figure 2.7: An example of rectangular tiling with stencil computations.

Figure 2.7 shows rectangular tiling for a one dimensional 3-point stencil computation. This stencil is the simplest variant of a stencil computation and is the one that this paper will focus on. A value at index i in time step t is calculated from the value at i in time step t - 1 as well as its two neighbouring values at i - 1 and i + 1. Therefore, these tiles cannot be executed concurrently, because there are many inter-tile dependencies.

Figure 2.8: An example of overlapped tiling with stencil computations.

A commonly used tiling strategy for a stencil is overlapped tiling, which is shown in figure 2.8. When visualized across the time dimension, these tiles resemble trapezoidal shapes. The core idea behind this approach is that each tile does not only compute some number of values in the final time step, but also all the values that are required from earlier time steps, which results in an overlap between the tiles. Although this introduces redundant computations, it also solves the dependency issues and thus all the tiles can be computed concurrently. These overlapping regions are also referred to as halo regions [11, 19, 26], ghost zones [8, 15] or shadow regions [9].

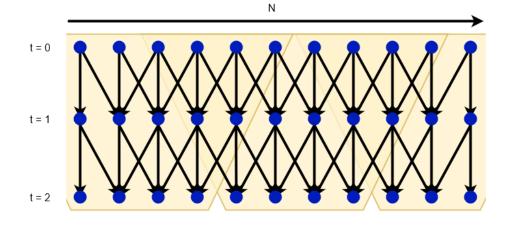

Figure 2.9: An example of split tiling with stencil computations.

An alternative, called split tiling, is shown in figure 2.9. This method does

not require redundant computations, but it does require more communication, because not all tiles are independent. The yellow trapezoidal tiles can be started concurrently, but the red triangle-shaped tile can only be computed when all the yellow tiles are finished (or at the very least the ones directly neighbouring the red tile). Note that the coverage of these tiles do not represent the memory foot-print, because the values that the red tile depends on still have to be in memory.

Furthermore, these tiling strategies are in GPUs usually applied at the thread block level and aim to improve performance by reducing global reads and kernel exits by utilizing the faster local memory shared between the threads in a block [10, 11, 15, 19]. However, the purpose of my research is different, because the goal is to be able to independently calculate much larger chunks of data. In turn, these independent chunks can then be streamed through the GPU to realize out-of-core execution.

Unfortunately, it is not trivial to determine which tiling approach would suit my use-case better and trying both is out of scope. For split tiling, there is no overhead from redundant computations, but the boundaries of each tile will need to be recomputed each loop. This again increases the amount of computation and leads to more control-flow divergence as pointed out by J. Meng, and K. Skadron [15]. However, the authors are considering strategies at the thread block level. Indeed, recomputing boundaries for each block of threads introduces a lot of extra computation. However, I only need to recompute the boundaries once for each stream per time step and this can be done by the host at each kernel launch.

Another concern is pointed out by P.S. Rawat et al.[19], being that split tiling leads to irregular shaped-tiles, which makes it more challenging to achieve high performance on a GPU. This is especially true at the chunk level, because the red triangles will be many orders smaller than the yellow trapezoids. However, the standard split tiling approach can be slightly altered to make the tiles regular, as I will show in chapter three.

Furthermore, the memory footprint of overlapped tiling is clearly larger, which is the main problem this research is trying to tackle. Additionally, while the computational overhead for 1D stencils can be kept relatively small, it becomes quite significant for 3D stencils [19]. Although I only consider a 1D 3-point stencil in my code generation schemes and experiments, it does not hurt to keep in mind how this would scale for possible future work.

### Chapter 3

# **Out-of-core code generation**

In this chapter, I present an approach to out-of-core code generation for both map-like operations and 3-point stencil computations, respectively, as they are defined in section 2.3.1 and 2.3.2.

For both algorithmic classes, this is be done by first defining an in-core specification in C++-like pseudo-code. After that, an in-core specification using CUDA streams is presented including rewriting rules and explanations. Based on these streamed blue prints, an out-of-core version is developed.

The in-core specification using CUDA streams serves as a solid checkpoint from both an explanatory and problem-solving perspective. Furthermore, it is also helps with investigating whether streaming a computation through the GPU is interesting regardless of whether the data fits in the memory or not.

#### 3.1 Map-like operations

#### 3.1.1 In-core

In figure 3.1, the in-core specification that I will use as a basis for the outof-core code generation of map-like operations is shown. The host memory is pinned on lines 1-2 as described in figure 2.5, because this will be a requirement for using CUDA streams later on. Next, two buffers,  $dev_a$  and  $dev_b$ , are allocated on the device (lines 4-5) to match the given buffers aand b on the host and, after that, the host memory is transferred to the device (h2d) on lines 7-8. Subsequently, n kernels are launched for a given ttime steps (lines 10-14). Although more than one time step does not occur as often as with stencil computations, it is still useful to consider and helpful for performance analysis. At the end, the resulting values in  $dev_a$  are copied to the host memory (d2h) on line 14.

```

1

a = cudaHostRegister(a, n);

\mathbf{2}

b = cudaHostRegister(b, n);

3

dev_a = cudaMalloc(dev_a, n);

4

\mathbf{5}

dev_b = cudaMalloc(dev_b, n);

\mathbf{6}

7

dev_a = cudaMemcpy(dev_a, a, n, h2d);

8

dev_b = cudaMemcpy(dev_b, b, n, h2d);

9

10

for (i = 1; i \le t; i++)

dev_a = kerne \ll n \gg (dev_a, dev_b, n);

11

12

}

13

14

a = cudaMemcpy(a, dev_a, n, d2h);

15

16

kernel(dev_a, dev_b, n)

17

{

tid = blockIdx.x * blockDim.x + threadIdx.x;

18

stride = blockDim.x * gridDim.x;

19

20

21

for(i = tid; tid < n; tid+=stride)</pre>

22

dev_a[i] = f (dev_a[i], dev_b[i]);

23

}

```

Figure 3.1: The in-core specification of a map-like operation.

The kernel code is shown on lines 16-23. First, the index of the value in  $dev_a$  that the executing thread has to calculate is determined and stored in variable *tid*. Next, the stride is calculated just in case the total amount of requested threads is smaller than the size of  $dev_a$  in the device's memory. Finally,  $dev_a[i]$  is calculated using the values at i in both  $dev_a$  and  $dev_b$  and applying generic function f to them  $(i \in [0..n - 1])$ . This procedure corresponds to the background of grid-stride-loops and map-like operations as described in sections 2.1.3 and 2.3.1, respectively.

#### 3.1.2 In-core streamed

In order to stream a map-like operation through the device, it is necessary to find a way to perform calculations on subsets of the data independently. Recall that a map-like operation is defined as applying a generic function findex-wise to both a value from vector a and vector b.

For example, the operation could be a[i] = a[i] + b[i], where  $i \in [0..n-1]$ and f := (+), which corresponds to vector addition. Since you only need the values at *i* from time step *j*, where  $j \in [0..t]$ , to calculate the value *i* at time step j + 1, it is straightforward to create chunks of data that can be calculated independently.

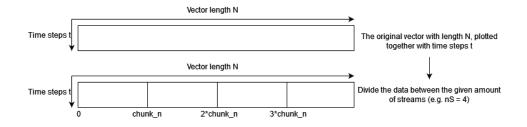

Figure 3.2: A visual representation of dividing a vector in independent chunks for map-like operations.

This process is illustrated in figure 3.2. Clearly, it is possible to calculate (n + nS - 1) / nS and store the result in variable  $chunk_n$ . Next to representing the chunk size,  $chunk_n$  can also be used to calculate the offset of each independent chunk in the host and the device buffer. However, do keep in mind that the right-most chunk is not always equal to  $chunk_n$ , so, a second variable,  $lchunk_n$ , is necessary, which is equal to  $n - nS * chunk_n$ .

```

1 kernel(dev_a, dev_b, n)

2 {

3 tid = blockIdx.x * blockDim.x + threadIdx.x;

4 stride = blockDim.x * gridDim.x;

5

6 for(i = tid; tid < n-1; tid+=stride)

7 dev_a[tid] = f (dev_a[i], dev_b[i]);

8 }

</pre>

```

$\rightarrow \rightarrow \rightarrow$

```

1 kernel(dev_a, dev_b, offset_l, offset_r)

2 {

3 tid = blockIdx.x * blockDim.x + threadIdx.x + offset_l;

4 stride = blockDim.x * gridDim.x;

5

6 for(i = tid; tid < offset_r; tid+=stride)

7 dev_a[tid] = f (dev_a[i], dev_b[i]);

8 }

</pre>

```

Figure 3.3: A rewriting schematic for rewriting in-core kernel code to in-core streamed kernel-code. The upper code block shows the original kernel code and the lower code block shows the resulting kernel code.

In order to ensure that each stream can only compute on its assigned data, it is necessary to introduce bounds in the kernel code, which is shown in figure 3.3. The changes are on lines 1, 3 and 6 in the lower code block. First, two new arguments,  $offset_l$  and  $offset_r$  are added to the kernel. The former represents the left bound of the executing threads in the current time step and the latter the right bound. Next,  $offset_l$  is added to *tid* on line 3 to make sure the threads access the correct region of the vectors. Finally,  $offset_r$  replaces n-1 on line 6 in order to prevent the threads from accessing data that the specific stream should not be operating on.

$1 | dev_a = cudaMemcpy(dev_a, a, n, h2d);$  $2 | dev_b = cudaMemcpy(dev_b, b, n, h2d);$

```

\rightarrow \rightarrow \rightarrow

```

```

1

stream [nS]:

2

for (i = 0; i < nS; i++)

3

cudaStreamCreate(stream[i]);

4

chunk_n = (n + nS - 1) / nS

5

6

lchunk_n = n - (nS-1)*chunk_n;

7

for (i = 0; i < nS-1; i++){

8

9

cudaMemcpyAsync(dev_a[i*chunk_n], a[i*chunk_n], chunk_n, h2d,

10

stream[i]);

cudaMemcpyAsync(dev_b[i*chunk_n], b[i*chunk_n], chunk_n, h2d,

11

12

stream[i]);

13

}

14

cudaMemcpyAsync(dev_a[(nS-1)*chunk_n], a[(nS-1)*chunk_n])

lchunk_n, h2d, stream [nS-1];

15

16

cudaMemcpyAsync(dev_b[(nS-1)*chunk_n], b[(nS-1)*chunk_n],

lchunk_n, h2d, stream [nS-1];

17

```

Figure 3.4: A rewriting schematic for rewriting in-core memory transfers to in-core streamed memory transfers (host to device). The upper code block shows the original synchronous memory transfers and the lower code block shows the rewritten code.

Since the map-like operation is now split between streams, each stream should copy their own portion of data. The necessary code transformation regarding the copying of data is shown in figure 3.4. First, the requested nS streams have to be explicitly created, which is done on lines 1-3. After that, variables *chunk\_n* and *lchunk\_n* are calculated as defined earlier on lines 5-6. The formula used ensures that *lchunk\_n* is equal to *chunk\_n* or smaller in case nS does not divide n. Finally, asynchronous memory transfers are introduced for each stream on lines 8-17.

The first nS-2 streams copy the same amount of data (*chunk\_n* values), following the exact same offset pattern (at  $i^*chunk_n$ ), so these transfers can be initiated in a loop. The last stream also follows the same offset pattern, but instead needs to transfer *lchunk\_n* values, so its transfers are declared separately.

#### $\rightarrow \rightarrow \rightarrow$

```

1

for (i = 1; i \le t; i++)

for (j = 0; j < nS-1; j++){

\mathbf{2}

3

kernek chunk_n, stream [j] >>> (dev_a, dev_b, j*chunk_n,

4

(j+1)*chunk_n);

5

kernek lchunk_n, stream [nS-1] >>> (dev_a, dev_b,

\mathbf{6}

7

(nS-1)*chunk_n,

8

(nS-1)*chunk_n+lchunk_n);

9

}

```

Figure 3.5: A rewriting schematic for rewriting in-core kernel launches to in-core streamed kernel launches. The upper code block shows the original kernel launches and the lower code block shows the rewritten code up-to and including the synchronization mid-point.

Similarly, instead of one kernel per time step, nS kernels per time step are now required. The rewriting scheme for this purpose is shown in figure 3.5. As with the memory transfers, the first nS-2 streams follow the same boundary pattern and use the same number of threads for their calculations. The left bound is  $j^*chunk_n$  and the right bound is  $(j+1)^*chunk_n$ . Their exact kernel launches are on lines 2-5.

Although on line 2 in the upper code block it is only necessary to specify the number of threads, on lines 3 and 6 in the lower code block the stream that will execute the specific kernel also has to be given. Furthermore, the last stream's kernel is declared separately on lines 6-9, because it uses less threads and the distance between its left and right bound is different from the other streams.

Notably, due to streams being asynchronous, the order of execution of these kernels cannot be guaranteed. It might seem like this could lead to synchronization issues, but it does not, because the data the different streams operate on is fully independent. The only thing that matters is that the time steps of each stream happen chronologically, which they will, because all kernels and transfers *within* a stream are synchronous.

The final necessary adjustment is shown in figure 3.6. Similar to h2d memory transfers, each stream copies their assigned data back to the host when it finishes its kernels. This is done by declaring an asynchronous memory transfer for each stream in the same manner as before, but now with the copy direction d2h. At the end, on line 8, the host is blocked till all streams are finished executing their tasks. This ensures that the entire map-like operation has finished before giving control back to the host.

1 | a = cudaMemcpy(dev\_a, a, n, d2h);

```

\rightarrow \rightarrow \rightarrow

```

Figure 3.6: A rewriting schematic for rewriting in-core memory transfers to in-core streamed memory transfers (device to host). The upper code block shows the synchronous memory transfer and the lower code block shows the rewritten asynchronous memory transfers.

#### 3.1.3 Out-of-core

Previously, out-of-core was defined as performing an algorithm on data that is too large to fit into the GPU's memory in one go. An important part of my strategy to accomplish this is to stream chunks of data through the device using CUDA. In section 3.1.2, I show how this can be done for in-core data in combination with map-like operations. Now, in this section I present my strategy for rewriting the in-core streamed version to out-of-core.

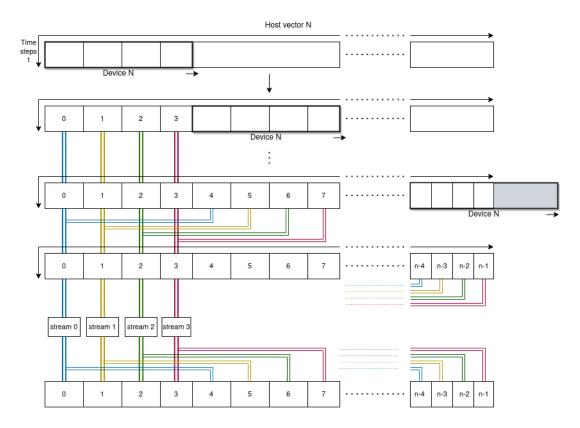

Figure 3.7: A visual representation of the device memory moving as a sliding window across the host memory.

Since it is already shown that the chunks can be calculated independently, the next step is to figure out a procedure for actually streaming the data through the GPU in an out-of-core manner. To accomplish this, I opt for an approach that is based on the idea of using the device's memory as a sliding window that can be moved over the host's memory from left to right, which is depicted in figure 3.7.

The algorithm starts off at index zero and divides the data that currently overlaps with the window in a predetermined number of independent chunks. Subsequently, these chunks can be streamed in similar fashion as in section 3.1.2.

However, after doing so, there is still data left on the host that has not been processed yet. Therefore, while the device starts copying memory and launching kernels, the sliding window is moved forward until it exclusively covers unprocessed data. Next, it is possible to already stream the next portion, which essentially creates several queues of chunks that are streamed concurrently through the GPU, which is illustrated in figure 3.8.

| Stream 0 | h2d<br>chunk 0 | t kernels<br>chunk 0 | d2h<br>chunk 0 | h2d<br>chunk 4 | t kernels<br>chunk 4 | d2h<br>chunk 4 | <br>h2d<br>chunk n-4 | t kernels<br>chunk n-4 | d2h<br>chunk n-4 |

|----------|----------------|----------------------|----------------|----------------|----------------------|----------------|----------------------|------------------------|------------------|

| Stream 1 | h2d<br>chunk 1 | t kernels<br>chunk 1 | d2h<br>chunk 1 | h2d<br>chunk 5 | t kernels<br>chunk 5 | d2h<br>chunk 5 | <br>h2d<br>chunk n-3 | t kernels<br>chunk n-3 | d2h<br>chunk n-3 |

| Stream 2 | h2d<br>chunk 2 | t kernels<br>chunk 2 | d2h<br>chunk 2 | h2d<br>chunk 6 | t kernels<br>chunk 6 | d2h<br>chunk 6 | <br>h2d<br>chunk n-2 | t kernels<br>chunk n-2 | d2h<br>chunk n-2 |

| Stream 3 | h2d<br>chunk 3 | t kernels<br>chunk 3 | d2h<br>chunk 3 | h2d<br>chunk 7 | t kernels<br>chunk 7 | d2h<br>chunk 7 | <br>h2d<br>chunk n-1 | t kernels<br>chunk n-1 | d2h<br>chunk n-1 |

Figure 3.8: A visual representation of the sequence of actions each stream takes based on figure 3.7.

There are two aspects interesting to note here. First of all, it is now necessary to execute t kernels before transferring results back to the host, because any occupied space on the device has to be reused for the next chunk. Clearly, it would be difficult to keep track of how many time steps remain for different chunks and it would also introduce additional unnecessary memory transfer.

Secondly, my method of out-of-core streaming can be seen as a greedy approach, because at any point, I try to fit as much data on the device as possible, without considering how well the available memory divides the data on the host. Consequently, choosing the right values for the different parameters involved is non-trivial, but establishing heuristics is out of scope for this research.

```

1 | dev_a = cudaMalloc(dev_a, n);

2 | dev_b = cudaMalloc(dev_b, n);

```

```

\rightarrow \rightarrow \rightarrow

```

```

1 free_mem = cudaMemGetInfo()

2 dev_n = free_mem * 95 / 100 / dtype_n / 2

3

4 dev_a = cudaMalloc(dev_a, dev_n)

5 dev_b = cudaMalloc(dev_b, dev_n)

```

Figure 3.9: A rewriting schematic that transforms the allocation of device buffers based on n, to allocation based on the available memory on the device.

Since allocating two buffers of size n on the device is no longer possible, the original buffer allocation needs to be changed, which is shown in figure 3.9. First, the amount of free memory on the device in bytes is queried on line 1 in the lower code block. Considering that it is often not possible to use all of the free memory, only 95 percent of the total available space is used, which is shown on line 2. The exact size one should choose here depends on the architecture, so to automate this in future, heuristics should be established.

Furthermore, the new value is divided by  $dtype_n$ , which refers to the size in bytes of the datatype that is used. Finally, the value is also divided by two, because this operation requires the allocation of two buffers. The result is stored in the variable  $dev_n$  and then used on lines 4-5 to allocate  $dev_a$  and  $dev_b$ .

Now that  $dev_n$  has been established, most of the rewritten code in section 3.1.2 needs to be altered. The start of this is shown in figure 3.10 and other parts of the new code are spread over multiple figures, which is also indicated with comments on lines 9-10 in the lower code block. Fortunately, the general structure of the code can be reused and thus a lot of the new code will look very familiar.

However, figure 3.10 mostly contains new variables and ideas. First, recall that the core idea is to divide the hosts data up in chunks that do fit on the device and can be independently processed, at the very least, one after each other. Therefore, it is necessary to introduce an approach that is based on the idea of having several rounds of memory transfers and computations.

As mentioned earlier, the number of rounds is calculated in a greedy manner by dividing n by  $dev_n$  and stored in the variable r, which is shown on line 1 in the lower code block. Next, the calculation of  $chunk_n$  and  $lchunk_n$  is slightly altered on lines 2-3 by exchanging n with  $dev_n$ .

Similar to the possible difference between  $chunk_n$  and  $lchunk_n$ , the last round is likely to be smaller than round 0 to n-2. Therefore, the size of the last round and the chunk sizes of the last round are calculated on lines 5-7. Their values are then stored in  $lr_n$ ,  $lr_chunk_n$  and  $lr_lchunk_n$ , respectively.

Finally, the actual code for the implementation of these rounds is split in to two separate figures. The code for rounds 0 to n-2 is shown in figure 3.11 and the code for the final round is shown in figure 3.12.

```

1

chunk_n = (n + nS - 1) / nS

\mathbf{2}

lchunk_n = n - (nS-1)*chunk_n;

3

for (i = 0; i < nS-1; i++)

4

cudaMemcpyAsync(dev_a[i*chunk_n], a[i*chunk_n], chunk_n, h2d,

5

6

stream[i]);

7

cudaMemcpyAsync(dev_b[i*chunk_n], b[i*chunk_n], chunk_n, h2d,

8

stream[i]);

9

}

10

cudaMemcpyAsync(dev_a[(nS-1)*chunk_n], a[(nS-1)*chunk_n])

lchunk_n, h2d, stream[nS-1];

11

12

cudaMemcpyAsync(dev_b[(nS-1)*chunk_n], b[(nS-1)*chunk_n],

13

lchunk_n, h2d, stream [nS-1];

14

15

for (i = 1; i \le t; i++)

16

for (j = 0; j < nS-1; j++)

kernek chunk_n, stream [j] >>>(dev_a, dev_b, j*chunk_n,

17

(j+1)*chunk_n);

18

19

kernek lchunk_n, stream [nS-1] >>> (dev_a, dev_b,

20

21

(nS-1)*chunk_n,

22

(nS-1)*chunk_n+lchunk_n);

23

}

24

25

for (i = 0; i < nS-1; i++)

26

cudaMemcpyAsync(a[i*chunk_n], dev_a[i*chunk_n],

27

chunk_n, d2h, stream[i];

28

}

\label{eq:cudaMemcpyAsync} \textbf{cudaMemcpyAsync} (\, a \left[\,(\, nS - 1 * chunk_n \, ] \,, \ dev_a \left[\,(\, nS - 1) * chunk_n \, \right] \,,

29

30

lchunk_n, d2h, stream [nS-1];

```

```

\rightarrow \rightarrow \rightarrow

```

```

1

r = (n + dev_n - 1) / dev_n;

2

chunk_n = (dev_n + nS - 1) / nS;

lchunk_n = dev_n - (nS-1) * chunk_n;

3

4

lr_n = n - (r-1) * dev_n;

5

6

lr_{chunk_n} = (lr_{n} + nS - 1) / nS;

lr_lchunk_n = lr_n - (nS-1) * lr_chunk_n;

7

8

9

// rounds 0 to n-2, see figure 3.11

10

// round n-1, see figure 3.12

```

Figure 3.10: A rewriting schematic that transforms the in-core streaming of map-like operations, to out-of-core.

```

1

for (i = 0; i < r-1; i++)

\mathbf{2}

for (j = 0; j < nS-1; j++){

cudaMemcpyAsync(dev_a[j*chunk_n], a[i*dev_n+j*chunk_n])

3

chunk_n, h2d, stream [j]);

4

\mathbf{5}

cudaMemcpyAsync(dev_b[j*chunk_n], b[i*dev_n+j*chunk_n])

\mathbf{6}

chunk_n, h2d, stream[j];

7

}

8

cudaMemcpyAsync(dev_a [(nS-1)*chunk_n])

9

a[i*dev_n+(nS-1)*chunk_n], lchunk_n, h2d,

10

stream [nS-1];

cudaMemcpyAsync(dev_b[(nS-1)*chunk_n])

11

12

b[i*dev_n+(nS-1)*chunk_n], lchunk_n, h2d,

13

stream [nS-1];

14

15

for (k = 1; k \le t; k++)

16

for (j = 0; j < nS-1; j++){

kernek chunk_n, stream[j] >>>(dev_a, dev_b, j*chunk_n,

17

18

(j+1)*chunk_n);

19

kernek kernek konk_n, stream [nS-1] >>> (dev_a, dev_b, dev_b)

20

21

(nS-1)*chunk_n,

22

(nS-1)*chunk_n+lchunk_n);

23

}

24

for (j = 0; i < nS-1; j++)

25

26

cudaMemcpyAsync(a[j*dev_n+j*chunk_n], dev_a[j*chunk_n],

27

\operatorname{chunk}_n, \operatorname{d2h}, \operatorname{stream}[j];

28

}

29

cudaMemcpyAsync(a[j*dev_n+(nS-1)*chunk_n]),

30

dev_a[(nS-1)*chunk_n], lchunk_n, d2h,

31

stream [nS-1];

32

}

```

Figure 3.11: The rewritten code of rounds 0 to r - 2 for performing map-like operations out-of-core.

As mentioned earlier, the structure of the code in figure 3.11 is similar to the code in the upper code block of figure 3.10. The h2d memory transfers are depicted on lines 2-13, the kernel calls on lines 15-23 and the d2h memory transfers on lines 25-31. The access patterns and number of threads are exactly the same for the first r-1 rounds, so the code can be executed in a loop r-1 times.

In order to access the correct chunk of data in the host, the indices for a and b are altered, which is shown on lines 3, 5, 9, 12, 26 and 29. First, the offset for the entire data assigned to the current round is calculated by  $i^{*}dev_{-}n$ . Next, it is possible to get the correct region of data to each stream j by adding  $j^{*}chunk_{-}n$ . Similar to the streamed version, the memory transfers and kernel calls for the last stream are declared separately, because it operates on  $lchunk_{-}n$  data instead of  $chunk_{-}n$ .

```

1

for (j = 0; j < nS-1; j++)

\mathbf{2}

cudaMemcpyAsync(dev_a[j*chunk_n],

a[(r-1)*dev_n+j*lr_chunk_n], lr_chunk_n,

3

h2d, stream [j]);

4

\mathbf{5}

cudaMemcpyAsync(dev_b[j*chunk_n],

\mathbf{6}

b[(r-1)*dev_n+j*lr_chunk_n], lr_chunk_n,

7

h2d, stream [j]);

8

9

cudaMemcpyAsync(dev_a[(nS-1)*chunk_n],

10

a[(r-1)*dev_n+(nS-1)*lr_chunk_n],

lr_lchunk_n, h2d, stream[nS-1];

11

12

cudaMemcpyAsync(dev_b[(nS-1)*chunk_n])

13

b[(r-1)*dev_n+(nS-1)*lr_chunk_n],

14

lr_lchunk_n, h2d, stream [nS-1];

15

16

for (k = 1; k \le t; k++)

for (j = 0; j < nS-1; j++) {

17

kernek lr_chunk_n, stream [j] >>>>(dev_a, dev_b, j*chunk_n

18

19

j*chunk_n+lr_chunk_n);

20

}

kernek lr_lchunk_n, stream [nS-1] >>> (dev_a, dev_b,

21

22

(nS-1)*chunk_n,

(nS-1)*chunk_n+lr_lchunk_n);

23

24

}

25

26

for (j = 0; j < nS-1; j++) {

27

cudaMemcpyAsync(a[(r-1)*dev_n+j*lr_chunk_n]),

28

dev_a[j*chunk_n], lr_chunk_n, d2h, stream[j]);

29

}

30

cudaMemcpyAsync(a[(r-1)*dev_n+(nS-1)*lr_chunk_n]),

31

dev_a[(nS-1)*chunk_n], lr_lchunk_n, d2h,

stream [nS-1];

32

```

Figure 3.12: The rewritten code for the kernel calls in round r - 1 for maplike operations out-of-core.

The final round of the out-of-core map-like operation looks similar to rounds 0 to n-2. However, the total round size and most of the chunk sizes are different. Additionally, each occurrence of i is replaced with r-1, because of the lack of a loop.

First, the h2d memory transfers are shown on lines 1-8 in figure 3.12. The access patterns to  $dev_a$  and  $dev_b$  remain the same, but all the other instances of  $chunk_n$  and  $lchunk_n$  are replaced with  $lr_chunk_n$  and  $lr_lchunk_n$ , respectively. Next, the kernel calls are shown on lines 16-24. Although the left bounds remain the same, the right bounds now depend on  $lr_chunk_n$ and  $lr_lchunk_n$ . Furthermore, the number of threads are also reduced to their respective sizes for the last round. Finally, the d2h memory transfers are shown on lines 26-32, which contain the same changes as for h2d.

#### **3.2 3-point stencil computations**

#### 3.2.1 In-core

```

in = cudaHostRegister(in, n);

1

\mathbf{2}

out = cudaHostRegister(out, n);

3

4

dev_{in} = cudaMalloc(in_dev, n);

5

dev_out = cudaMalloc(out_dev, n);

6

\overline{7}

dev_in = cudaMemcpy(dev_in, in, n, h2d);

dev_out = cudaMemcpy(dev_out, out, n, h2d);

8

9

10

for (i = 1; i \le t; i++)

11

dev_out = kerne \ll n \gg (dev_in, dev_out, n);

12

if( i != t )

13

dev_{in}, dev_{out} = swap(dev_{in}, dev_{out});

14

}

15

out = cudaMemcpy(dev_out, out, n, d2h);

16

17

kernel(dev_in, dev_out, n)

18

19

{

tid = blockIdx.x * blockDim.x + threadIdx.x;

20

21

stride = blockDim.x * gridDim.x;

22

23

for (i = tid; tid < n-1; tid += stride)

24

\operatorname{dev_out}[i] = f ( \operatorname{dev_in}[i-1], \operatorname{dev_in}[i],

25

\operatorname{dev}_{in}[i+1]);

26

}

```

Figure 3.13: The in core specification of a three-point stencil computation.

In figure 3.13, the in-core specification that I use as a basis for the out-ofcore code generation of 3-point stencil computations is shown. The pinning of the host memory (lines 1-2), the memory allocation on the device (lines 4-5) and the memory transfers (lines 7-8, 16) are identical to those in the in-core specification for map-like operations. On the other hand, some variables names, the kernel launches and the kernel code are slightly different.

First of all, the memory pointers a, b,  $dev_a$  and  $dev_b$  are replaced with *in*, *out*,  $dev_in$  and  $dev_out$ . I make this decision, because, with stencil computations, it is helpful to make a clear distinction between the in- and output buffer.

Secondly, after each time step, the pointers to  $dev_in$  and  $dev_out$  are swapped (line 13), but only if the last time step has not yet been made. The reason for this is that in a given time step i, where  $i \in [1..t-1]$ , the output buffer becomes the input buffer in time step i + 1.

Finally, the actual computation in the kernel code has to be adjusted to

a 3-point stencil. This is shown on lines 24-25, where  $dev_out[i]$  is calculated using the values at  $dev_in[i-1]$ ,  $dev_in[i]$  and  $dev_in[i+1]$  and applying generic function f to them  $(i \in [1..n-2])$ . This procedure corresponds to the background of a 3-point stencil computation as described in section 2.3.2.

#### 3.2.2 In-core streamed

Figure 3.14: A visual representation of dividing a vector in (partially) independent chunks for 3-point stencil computations.

In order to stream a stencil computation through the device, it is necessary to find a way to calculate subsets of the data independently. Unfortunately, this is not as straightforward as with map-like operations, because in order to calculate some value i in time step j, values i-1, i and i+1 in time step j - 1 have to be calculated first. Clearly, if value i-1 or i+1 happens to be part of a different stream, then value i cannot be calculated independently.

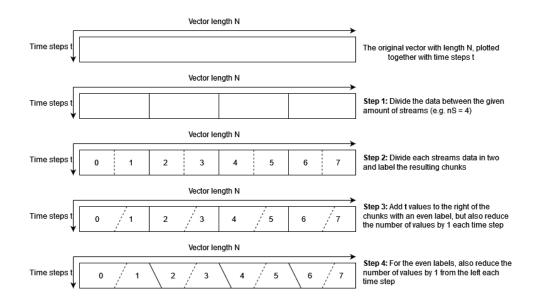

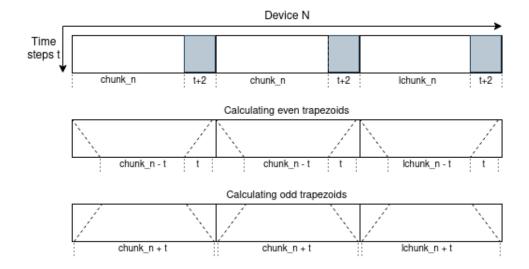

In figure 3.14, my strategy for calculating independent trapezoidal-shaped chunks over the time dimension is shown. For convenience, the trapezoids are numerically labeled from left to right starting at 0. Consequently, it is possible to distinguish between two types of trapezoids based on their label; even- and odd trapezoids.

First, step one divides the entire data over the number of streams that were given, which is four in this example. Now, it would be possible to immediately start launching t independent kernels on the streams. However, as hinted at earlier, the streams can only safely read the data they are assigned to, so each time step the number of values that can be calculated, reduces at the edges.

As one might expect, this would create pyramid-shaped gaps over the time dimension and these will still need to be calculated separately after all streams have finished their kernels. However, these gaps would, most of the time, contain a lot less data then the total data the streams originally started with. Therefore, in order to balance the workload, I divide the data of each stream in half before doing any calculations, as is illustrated in the second step of figure 3.14.

Next, the even chunks are given t extra values at t = 0, but the total amount of values is reduced each time step at the edges. This process will create equally sized trapezoidal-shaped chunks as is shown through step three and step four. Note that it is necessary to repeat this process several times if the individual chunk size is smaller than or equal to the number of time steps. However, this scenario will not be considered in the code further on.

Furthermore, these trapezoids cannot be calculated all at once, as pointed out in section 2.3.2. To solve this, each stream first has to calculate an even trapezoid, wait for the other streams to finish and then calculate an odd trapezoid.

```

kernel(dev_in, dev_out, n)

1

2

{

3

tid = blockIdx.x * blockDim.x + threadIdx.x;

4

stride = blockDim.x * gridDim.x;

5

\mathbf{6}

for (i = tid; tid < n-1; tid += stride)

7

dev_out[tid] = f ( dev_in[tid-1], dev_in[tid],

8

\operatorname{dev_in}[\operatorname{tid}+1]);

9

}

```

$\rightarrow \rightarrow \rightarrow$

```

kernel(dev_in, dev_out, offset_l, offset_r)

1

\mathbf{2}

{

3

tid = blockIdx.x * blockDim.x + threadIdx.x + offset_l;

4

stride = blockDim.x * gridDim.x;

5

\mathbf{6}

for(i = tid; tid < offset_r; tid+=stride)</pre>

7

\operatorname{dev_out}[\operatorname{tid}] = f (\operatorname{dev_in}[\operatorname{tid}-1], \operatorname{dev_in}[\operatorname{tid}],

8

\operatorname{dev_in}[\operatorname{tid}+1]);

9

}

```

Figure 3.15: A rewriting schematic for rewriting in-core kernel code to incore streamed kernel-code. The upper code block shows the original kernel code and the lower code block shows the resulting kernel code.

In practice, the trapezoids are computed by introducing boundaries in the

kernel code, which is shown in figure 3.15. The changes are on lines 1, 3 and 6 in the lower code block. First, two new arguments,  $offset_l$  and  $offset_r$ , are added to the kernel. The former represents the left bound of the executing threads in the current time step and the latter the right bound. Finally,  $offset_l$  is added to *tid* on line 3 and  $offset_r$  replaces n - 1 on line 6.

Each time step, these boundaries are reduced or increased on one or both sides by the host. This ensures that each stream only calculates the indices it is responsible for based on the trapezoid it is calculating. However, before diving into more details, it is necessary to understand in which order the trapezoids have to be calculated.

As mentioned before, each stream will calculate two trapezoids; one even and one odd. In general, this means that the first stream calculates trapezoids 0 and 1, the second calculates trapezoids 2 and 3, et cetera. More formally, when given n streams, then stream i, where  $i \in [0..n - 1]$ , calculates trapezoids 2i and 2i + 1.

Moreover, the even trapezoids can immediately be calculated and are fully independent. The non-trivial part is that the odd trapezoids cannot be calculated until the trapezoids they depend on have been calculated. This problem can be solved by introducing a synchronization point. Although there might be several approaches one can take, I have chosen to block the calculation of odd trapezoids until *all* streams have finished calculating their even trapezoid. Not only is this approach simple and concise, it also requires the least synchronization.

All things considered, we can sum up the following workflow for one stream:

- 1. Copy the data necessary to calculate the even trapezoid to the device.

- 2. Calculate the even trapezoid.

- 3. Copy the part of the result that is already final back to host memory.

- 4. Wait for all other streams to finish calculating their even trapezoid.

- 5. Copy the remaining data necessary to calculate the odd trapezoid.

- 6. Calculate the odd trapezoid.

- 7. Copy the the remainder of the final result to host memory.

1  $dev_in = cudaMemcpy(dev_in, in, n, h2d);$ 2

$dev_out = cudaMemcpy(dev_out, out, n, h2d);$

```

\rightarrow \rightarrow \rightarrow

```

```

1

stream [nS];

\mathbf{2}

for (i = 0; i < nS; i++)

3

cudaStreamCreate(stream[i]);

4

chunk_n = (n + 2*nS - 1) / 2*nS;

\mathbf{5}

lchunk_n = n - (2*nS-1)*chunk_n;

6

7

for (i = 0; i < nS; i++)

8

9

cudaMemcpyAsync(dev_in[i*2*chunk_n], in[i*2*chunk_n],

10

chunk_n + t, h2d, stream[i];

11

cudaMemcpyAsync(dev_out[i*2*chunk_n], out[i*2*chunk_n],

12

chunk_n + t, h2d, stream[i];

13

}

```

Figure 3.16: A rewriting schematic for rewriting in-core memory transfers to in-core streamed memory transfers (host to device). The upper code block shows the original synchronous memory transfers and the lower code block shows the rewritten code.

In order to realise part one of the workflow, it is necessary to rewrite the memory transfers from host to device. This is shown in figure 3.16. First, CUDA streams are created with given amount nS on lines 1-3.

Next, the size of each individual chunk, which is depicted in step 2 of figure 3.14, is calculated and stored in variable  $chunk_n$ . It is also necessary to keep into account that n may not be divisible by nS. Therefore, the variable  $lchunk_n$  is introduced to calculate the size of the right-most chunk.

Finally, asynchronous memory transfers are declared on lines 8-12. The number of each stream, i, and  $chunk_n$  are used to find the correct offset in host memory and device memory. In order to calculate the even trapezoids, each stream has to copy  $chunk_n + t$  values to the device (see the dotted lines in step 3 in figure 3.14).

1 for(i = 1; i <= t; i++){

2 kernel<<< n>>>(dev\_in, dev\_out, n);

3 if( i != t )

4 dev\_in, dev\_out = swap(dev\_in, dev\_out);

5 }

$\rightarrow \rightarrow \rightarrow$

```

1

for (i = 1; i \le t; i++)

2

kernek chunk_n+t-i, stream [0] >>>>(dev_in, dev_out, 1,

3

chunk_n+t-i);

4

for (j = 1; j < nS; j++){

5

kernek chunk_n+t-2*i, stream [j] >>> (dev_in, dev_out,

\mathbf{6}

j * 2 * chunk_n + i, (2 * j + 1) * chunk_n + t - i);

7

8

if(i != t)

9

dev_in, dev_out = swap(dev_in, dev_out);

10

}

11

12

cudaMemcpyAsync(out[0], dev_out[0], chunkSize, d2h, stream[0]);

13

14

for (i = 1; i < nS; i++)

15

cudaMemcpyAsync(out[i*2*chunk_n+t], dev_out[i*2*chunk_n+t]]

16

chunkSize-t, d2h, stream[i]);

17

}

18

19

cudaDeviceSynchronize();

```

Figure 3.17: A rewriting schematic for rewriting in-core kernel launches to in-core streamed kernel launches. The upper code block shows the original kernel launches and the lower code block shows the rewritten code up-to and including the synchronization mid-point.

In figure 3.17, a rewriting schematic is shown for rewriting the original kernel code in such a way that it matches steps 2-4 of the outlined workflow.

First, the single kernel call on line 2 in the upper code block has to be replaced by kernel calls for each individual stream. This is shown on lines 1-10 in the lower code block. The kernel call for stream 0 is called separately, because each time step only the right bound decreases. All the other kernels can be started in a for loop, because both boundaries shrink with the same pattern. Stream 0 calculates  $chunk_n + t - 1$  values in it's first time step and  $chunk_n$  values in its last. The rest of the streams calculate  $chunk_n + t - 2$  values in their first time step and  $chunk_n - t$  in their last. This is coherent with the approach shown in step 3 of figure 3.14.

Next, new code is introduced on lines 12-19 to implement step three and four of the workflow. Notably, only the values calculated in the last time step are final. Since stream 0 calculates more values in it's last time step than the other streams, its memory transfer back to the host is called separately on line 12. However, the other streams again follow the same pattern, so their memory transfers can be called in a for loop. Their left bounds in the final time step are moved t indices to the right and their right bounds are moved t indices to the left (see figure 3.14, step 3). Therefore, the source and destination offsets in the device and host memory are equal to  $i * 2 * chunk_n + t$ .

Finally, a synchronization call is made on line 19, which represents the fourth step in the work flow. It is important to note here that, technically, the streams don't actually wait, but the host is blocked till all streams on the device have finished their tasks.

```

if(t \% 2 = 0)

1

2

swap(dev_in, dev_out)

3

for (i = 0; i < nS-1; i++)

4

5

cudaMemcpyAsync(dev_in[(2*i+1)*chunk_n+t]),

6

in [(2*i+1)*chunk_n+t],

7

chunk_n-t, h2d, stream[i]);

8

cudaMemcpyAsync(dev_out[(2*i+1)*chunk_n+t]),

9

out[(2*i+1)*chunk_n+t]

10

chunk_n-t, h2d, stream[i]);

}

11

12

13

cudaMemcpyAsync(dev_in[(2*(nS-1)+1)*chunk_n+t]),

in[(2*(nS-1)+1)*chunk_n+t], lchunk_n-t, h2d,

14

\operatorname{stream}[nS-1]);

15

16

cudaMemcpyAsync(dev_out[(2*(nS-1)+1)*chunk_n+t]),

17

out \left[\left(2*(nS-1)+1\right)*chunk_n+t\right], lchunk_n-t, h2d,

18

stream [nS-1];

19

20

for (i = 1; i \le t; i++)

21

for (j = 0; j < nS-1; j++){

22

kernek chunk_n-t+2*i, stream [j] >>>>(dev_in, dev_out,

(2*j+1)*chunk_n+t-i

23

(2*j+2)*chunk_n+i);

24

25

kernel <<< lchunk_n-t+i, stream [nS-1] >> > (dev_in, dev_out,

26

27

(2*nS-1)*chunk_n+t-i, n-1)

28

if(i != t)

29

dev_{in}, dev_{out} = swap(dev_{in}, dev_{out});

30

}

```

Figure 3.18: Memory transfers and kernel calls for odd trapezoids, to be added directly after the rewritten code in figure 3.17, but before line 16 in the original in-core specification in figure 3.13.

In figure 3.18, code is shown for steps five and six of the workflow. This code will be generated right after the code in figure 3.17 and just before the code

on line 16 in the original specification. Before continuing the process, the program checks whether  $dev_in$  actually points to the original input vector (line 1-2). This means that if t is even,  $dev_in$  and  $dev_out$  need to be swapped.

After that, the remaining data is copied from the host to the device, which is shown on lines 4-16. Every stream but the last follow the same pattern for finding the correct offset on both the host and the device. The data for the even trapezoid of any stream *i* starts at  $2 * i * chunk_n$ , so the data for the odd trapezoid starts at  $(2*i + 1)*chunk_n$ . However, the first *t* values were already copied during the process of calculating the even trapezoid, so the offset becomes  $(2*i + 1)*chunk_n + t$ . Subsequently, the number values that need to be transferred then is  $chunk_n - t$ .

Similarly, the data transfer executed by the last stream, nS - 1, also has offset  $(2^{*}i + 1)$ . However, it is necessary to keep into account that the size of the last chunk may not be equal to  $chunk_n$ . Therefore, the number of values that are copied should be  $lchunk_n - t$ .

Finally, the code for calculating the odd trapezoids is shown on lines 18-28. The process of finding the left- and right bound for the kernel calls is similar to that of the even trapezoids, but now the bounds will be expanded each time step instead of decreased (see figure 3.14, step 3). This means that stream j, where  $j \in [0..nS - 2]$ , starts of with its left bound at  $(2^*j + 1)^*chunk_n + t - 1$  and its right bound at  $(2^*j + 2)^*chunk_n + 1$ . For the last stream, only the left bound increases and the right bound stays the same, which means the starting offsets are  $(2^*nS - 1)^*chunk_n + t - 1$  and n - 1, respectively. After t time steps, the last stream will calculate  $lchunk_n$  values and the others calculate  $chunk_n + t$  values.

1 out =  $cudaMemcpy(dev_out, out, n, d2h);$

```

\rightarrow \rightarrow \rightarrow

```

```

for (i = 0; i < nS-1; i++)

1

\mathbf{2}

cudaMemcpyAsync(out[(2*i+1)*chunk_n]),

dev_out[(2*i+1)*chunk_n], chunk_n+t, d2h,

3

4

stream[i]);

5

}

6

cudaMemcpyAsync(out[(2*(nS-1)+1)*chunk_n]),

7

dev_out[(2*(nS-1)+1)*chunk_n], lchunk_n, d2h,

8

stream [nS-1];

9

10

cudaDeviceSynchronize();

```

Figure 3.19: A rewriting schematic for rewriting the final in-core memory transfer to in-core streamed memory transfers. The upper code block shows the synchronous memory transfer and the lower code block shows the rewritten asynchronous memory transfers.

In order to implement the seventh and last step of the work flow, the final memory transfer of the in-core specification needs to be rewritten. This is shown in figure 3.19. At this point, each stream still has to copy back the results that were obtained by calculating the odd trapezoids.

The rewritten code for this is shown on lines 1-8. The offset in device and host memory is equal to  $(2^{*}i+1)^{*}chunk_{n}$ , which is the mid point of all the values stream *i* is responsible for (see the dotted lines in figure 3.14, step 2). The number of values that are copied from the device to the host is equal to  $chunk_{n} + t$  for all streams except for the last one, which is equal to  $lchunk_{n}$ .

Additionally, since all of these memory transfers are asynchronous, one more synchronization is necessary, which is shown on line 10. This ensures that the final result is correctly copied back to the host and that no unexpected behaviour will occur.

#### 3.2.3 Out-of-core

Figure 3.20: A visual representation of dividing the device memory into independent chunks for out-of-core 3-point stencils.

In this section, I present my out-of-core solution for 3-point stencil computations. Many of the core ideas for the out-of-core blueprints of map-like operations also apply here. However, due to the dependencies of the 3-point stencil, which were also discussed in sections 3.2.1 and 2.3.2, the implementation is a lot more challenging.

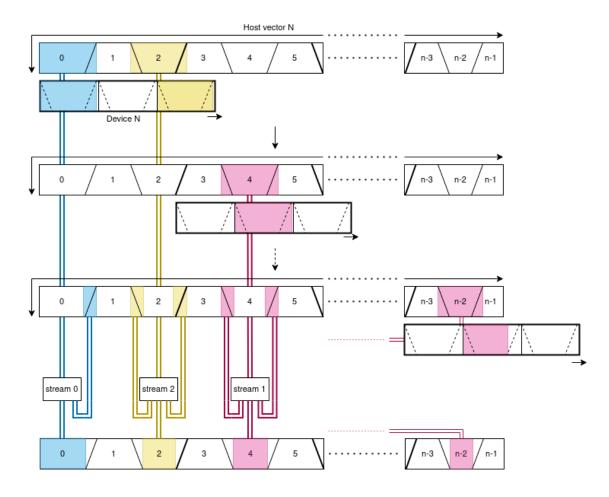

First of all, the allocation of device memory and the division of data between streams needs to be more carefully considered, which is shown in figure 3.20. Instead of directly dividing the memory, it is first necessary to reserve space for the number of time steps that will be done. After that, the remainder can be equally divided between the streams. Notably, it is necessary to reserve two extra values on top of the number of time steps (i.e. t + 2), because in the last time step of the odd trapezoids  $chunk_n+t$  values are calculated. Clearly, in case of a 3-point stencil computation, in order to compute  $chunk_n + t$  values,  $chunk_n + t + 2$  are needed.

Figure 3.21: A visual representation of the device moving as a sliding window over the host in order to stream the even trapezoids.

Next, figure 3.21 shows the processing of all the even trapezoids in the host vector, based on the division in figure 3.20. Similar to map-like operations, the device memory is used as a sliding window that moves across the host memory. However, it is necessary to more carefully consider which of the chunks that currently overlap with the window will be send to the GPU. Indeed, only the even trapezoids can be processed at this time, so they have to be precisely located. In case of an odd number of streams, the number

of chunks that should be considered in each round alternates.

Furthermore, after executing t kernels on the even chunks, the d2h memory transfers also have to be slightly adjusted. Although the final  $chunk_n$  - t values (see figure 3.20) are still copied back to the host's output buffer as before, the other  $2^{*t}t$  values that are not yet final are needed for the odd trapezoids later on. Before, when the entire host vector fitted in the device memory, these unfinished values could be left in place. However, during out-of-core execution, the space they occupy is required to compute the next chunk. Therefore, two additional d2h transfers that copy the  $2^{*t}t$  intermediate values to the host's input buffer have to be in introduced. Note that these intermediate values also have to be transferred to the host's output buffer, so the d2h transfer containing final results should transfer  $chunk_n + t$  values instead of  $chunk_n - t$ . It is essential that these memory transfers are done correctly, because, otherwise, the final output buffer will not be correct.

Figure 3.22: A visual representation of the device moving as a sliding window over the host in order to stream the odd trapezoids.

Finally, figure 3.22 shows the processing of all the odd trapezoids in the host vector. In this case, there are less changes required than for the even trapezoids, but it is still important to carefully locate the odd trapezoids on the host. As mentioned before (and shown in figure 3.20), it is also necessary to copy two additional values for each chunk from the host compared to the in-core streamed version. Namely, instead of  $chunk_n + t$  values,  $chunk_n + t + 2$  values are copied. When a stream finishes the computation of an odd trapezoid, it only has to copy the final  $chunk_n + t$  output values once to the host's output buffer.

Although allowing for any number of streams was not much of an issue up until now, doing so for the out-of-core 3-point stencil would result in convoluted code. The reason for this is that the patterns for locating chunks in the host buffer differ between an odd and even number of streams. Therefore, the transformations that are presented only consider odd amounts of streams.

1 dev\_in = cudaMalloc(dev\_in, n); 2 dev\_out = cudaMalloc(dev\_out, n);

$\rightarrow \rightarrow \rightarrow$

```

1 free_mem = cudaMemGetInfo()

2 dev_n = free_mem * 95 / 100 / dtype_n / 2

3

4 dev_in = cudaMalloc(dev_in, dev_n)

5 dev_out = cudaMalloc(dev_out, dev_n)

6

7 r_n = dev_n - nS * (t+2);

```

Figure 3.23: A rewriting schematic that transforms the allocation of device buffers based on n, to allocation based on the available memory on the device.

Similar to out-of-core map-like operations, allocating two buffers of size n on the device is no longer possible, so the original buffer allocation on the device needs to be changed, which is shown in figure 3.23.

The necessary transformation is almost completely the same for both types of out-of-core computations, except that part of  $dev_n$  needs to be reserved for the time steps of each chunk. Therefore, the variable  $r_n$  is introduced on line 7 in the lower code block. It is calculated by subtracting  $nS^*(t+2)$  from the available memory on the device  $(dev_n)$ .

Moreover, the out-of-core 3-point stencils have a similar round-based approach as out-of-core map-like operations, but both the code for the calculation of even trapezoids and odd trapezoids need their own r rounds instead. Note that the synchronization shown in the in-core streamed version between the computation of even and odd trapezoids is still required.

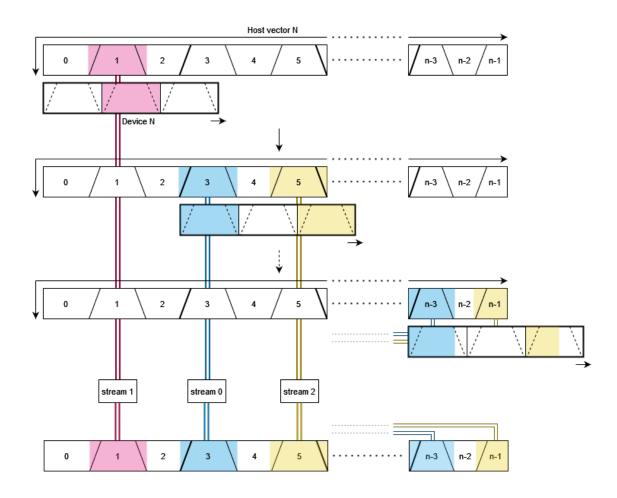

On top of that, it is necessary to be more selective of which streams are used in which round, as shown in figure 3.21 and 3.22. Accordingly, when calculating even trapezoids, code should only be executed for any stream j if it has the same parity as current round i, where  $j \in [0..nS - 1]$  and  $i \in [0..r - 1]$ . On the other hand, when calculating odd trapezoids, code should only be be executed for any stream j if it does *not* have the same parity as current round i. This is achieved by surrounding code for memory transfers and kernels with if-statements as shown in figure 3.24.

Figure 3.24: An example of using if-statements to select the correct streams j for transfers or kernel computations in a given round i.

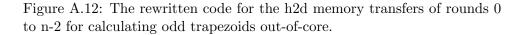

The rest of the code transformations that follow after figure 3.24 are largely the same as for the in-core streamed version, but combined with the changes introduced for out-of-core map-like operations and the usage of if-statements as shown in figure 3.24. Therefore, and also to improve readability, all the rewriting schemes for calculating even trapezoids can be looked at in detail in part A.1 of the appendix. Similarly, all the transformations for odd trapezoids are present in part A.2 of the appendix.

## Chapter 4

## **Performance** evaluation

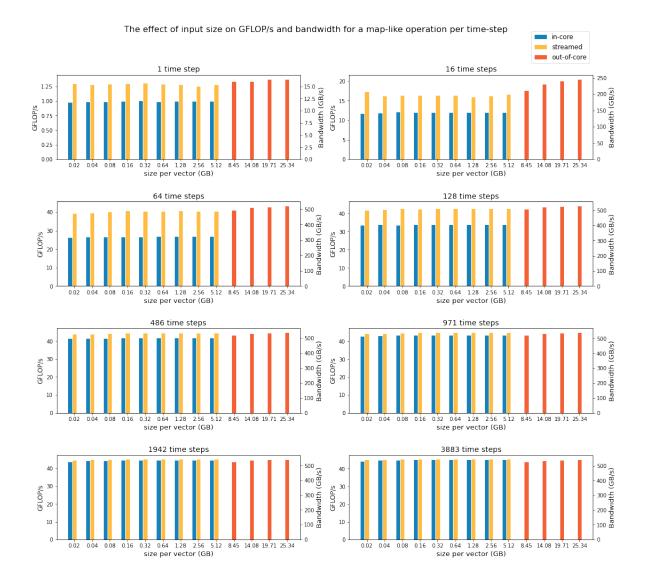

In this chapter, a performance analysis of the in-core, in-core streamed, and out-of-core versions is presented for both algorithmic classes.

#### 4.1 Experimental setup

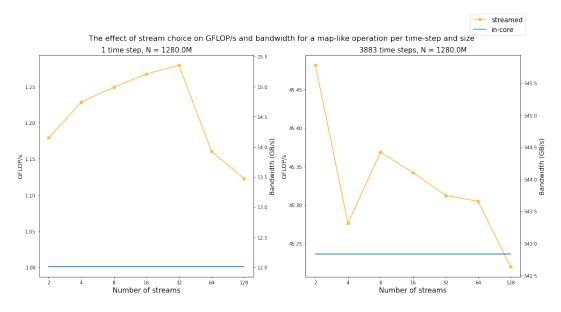

There are two aspects of interest regarding the rewritten code. Namely, the impact in-core streaming has on the overall performance and whether it is possible to achieve the same performance out-of-core compared to when the data fits on the device. In order to answer these questions, the in-core, in-core streamed and out-of-core blueprints are implemented in  $C++^1$ .