## RADBOUD UNIVERSITY NIJMEGEN

## MASTER THESIS COMPUTER SCIENCE

## Side-channel attacks on the IRMA card

April 1, 2014

Author: C.W.T.P. Thijssen, BSc. christiaanthijssen@gmail.com Supervisors:

Prof. dr. B.P.F. Jacobs

ir. P. Vullers

B. Ege, MSc

# Contents

| 1        | Intr | roduction                                                            |

|----------|------|----------------------------------------------------------------------|

|          | 1.1  | Problem statement                                                    |

|          | 1.2  | Organization of thesis                                               |

|          | 1.3  | I Reveal My Attributes (IRMA) Concept                                |

|          |      | 1.3.1 Privacy and security shortcomings of the current identity card |

|          |      | 1.3.2 Universal platform                                             |

|          |      | 1.3.3 New law proposals and IRMA                                     |

|          | 1.4  | Power analysis attacks                                               |

|          |      | 1.4.1 Example SPA attack                                             |

|          |      | 1.4.2 Example DPA attack                                             |

|          | 1.5  | Active attacks                                                       |

| <b>2</b> | IRN  | MA system                                                            |

|          | 2.1  | Stakeholders                                                         |

|          | 2.2  | Idemix or U-Prove                                                    |

|          | 2.3  | IRMA Configuration                                                   |

|          |      | 2.3.1 IRMA Protocol overview                                         |

|          |      | 2.3.2 Commitment Scheme                                              |

|          |      | 2.3.3 Zero-knowledge proof                                           |

|          |      | 2.3.4 Camenisch Lysyanskaya signatures                               |

|          |      | 2.3.5 Fiat-Shamir Heuristic                                          |

|          | 2.4  | Current IRMA implementation                                          |

|          |      | 2.4.1 Small scale usability experiment                               |

|          |      | 2.4.2 No authentication for public keys                              |

|          | 2.5  | IRMA hardware                                                        |

|          |      | 2.5.1 Infineon SLE-66                                                |

|          |      | 2.5.2 Infineon SLE-78                                                |

|          | 2.6  | Hardware countermeasures of IRMA cards                               |

|          |      | 2.6.1 Active Shield or Mesh                                          |

|          |      | 2.6.2 Optical sensors between critical chip parts                    |

|          |      | 2.6.3 Clock Jitter                                                   |

|          |      | 2.6.4 Power glitch detectors                                         |

|          |      | 2.6.5 Fault injection detection (Dual CPU)                           |

|          | 2.7  | Card certificates                                                    |

|          | 2.8  | IRMA software                                                        |

|          |      | 2.8.1 MILTOS                                                         |

|   | 2.9 | Possib   | le vulnerable operations                                        |    |            |  |   |   |   | 29 |

|---|-----|----------|-----------------------------------------------------------------|----|------------|--|---|---|---|----|

|   |     | 2.9.1    | Multiplication with the secret key                              |    |            |  |   |   |   | 29 |

|   |     | 2.9.2    | Modular exponentiation with the secret key as expo              | ne | $_{ m nt}$ |  |   |   |   | 29 |

|   |     |          |                                                                 |    |            |  |   |   |   |    |

| 3 |     | ack me   |                                                                 |    |            |  |   |   |   | 31 |

|   | 3.1 | Used E   | Equipment                                                       |    |            |  |   |   |   | 31 |

|   |     | 3.1.1    | Used PC                                                         |    |            |  |   |   |   | 31 |

|   |     | 3.1.2    | PicoScope 5203                                                  |    |            |  |   |   |   | 32 |

|   |     | 3.1.3    | Riscure Power tracer                                            |    |            |  |   |   |   | 32 |

|   |     | 3.1.4    | Riscure Inspector                                               |    |            |  |   |   |   | 33 |

|   | 3.2 | Contac   | ct and contact-less communication                               |    |            |  |   |   |   | 33 |

|   | ъ.  |          | 1.1                                                             |    |            |  |   |   |   | ۰. |

| 4 |     | cure m   |                                                                 |    |            |  |   |   |   | 35 |

|   | 4.1 | Acquis   |                                                                 |    |            |  |   |   |   | 35 |

|   | 4.2 | _        | Processing                                                      |    |            |  |   |   |   | 36 |

|   |     | 4.2.1    | ABS                                                             |    |            |  |   |   |   | 36 |

|   |     | 4.2.2    | Average                                                         |    |            |  |   |   |   | 37 |

|   |     | 4.2.3    | Binary                                                          |    |            |  |   |   |   | 37 |

|   |     | 4.2.4    | Binary with peak count                                          |    |            |  |   |   |   | 37 |

|   | 4.3 | Alignn   | nent                                                            |    |            |  |   |   |   | 37 |

|   |     | 4.3.1    | Static Alignment                                                |    |            |  |   |   |   | 38 |

|   |     | 4.3.2    | Round Alignment                                                 |    |            |  |   |   |   | 38 |

|   |     | 4.3.3    | Elastic Alignment                                               |    |            |  |   |   |   | 38 |

|   |     | 4.3.4    | Aligning based on Low Pass Result                               |    |            |  |   |   |   | 38 |

|   | 4.4 | Filterin | ng                                                              |    |            |  |   |   |   | 39 |

|   |     | 4.4.1    | Harmonics                                                       |    |            |  |   |   |   | 39 |

|   |     | 4.4.2    | Low Pass                                                        |    |            |  |   |   |   | 39 |

|   |     | 4.4.3    | Re-sample                                                       |    |            |  |   |   |   | 39 |

|   |     | 4.4.4    | Sync Re-sample                                                  |    |            |  |   |   |   | 40 |

|   |     | 4.4.5    | Spectrum                                                        |    |            |  |   |   |   | 40 |

|   |     | 4.4.6    | Spectrogram                                                     |    |            |  |   |   |   | 40 |

|   |     | 4.4.7    | Pattern Match                                                   |    |            |  |   |   |   | 41 |

|   |     | 4.4.8    | Pattern Extract                                                 |    |            |  |   |   |   | 41 |

|   |     | 4.4.9    | Data correlation                                                |    |            |  |   |   |   | 41 |

|   |     | 4.4.10   | AutoCorrelation                                                 |    |            |  |   |   |   | 41 |

|   |     | _        | Chain                                                           |    |            |  |   |   |   | 41 |

|   |     | 1,1,1    |                                                                 | •  |            |  | · | · | • |    |

| 5 | Att | acking   | the multiplication                                              |    |            |  |   |   |   | 43 |

|   | 5.1 |          | ter model                                                       |    |            |  |   |   |   | 43 |

|   | 5.2 | -        | red smart card                                                  |    |            |  |   |   |   | 43 |

|   | 5.3 | Differe  | ent implementations of the multiplication instruction           |    |            |  |   |   |   | 45 |

|   |     | 5.3.1    | Grade school algorithm                                          |    |            |  |   |   |   | 45 |

|   |     | 5.3.2    | Karatsuba                                                       |    |            |  |   |   |   | 47 |

|   |     | 5.3.3    | Double-and-add                                                  |    |            |  |   |   |   | 47 |

|   | 5.4 | Overvi   | iew power trace                                                 |    |            |  |   |   |   | 49 |

|   | 5.5 |          | ation with input $(c)$ and output $(\hat{s}) \dots \dots \dots$ |    |            |  |   |   |   | 50 |

|   |      | 5.5.1   | Correlation when zooming in on first peak   | 51        |

|---|------|---------|---------------------------------------------|-----------|

|   |      | 5.5.2   | Removing the blinding factor                | 53        |

|   | 5.6  | Perfor  | med attack on the multiplication part       | 53        |

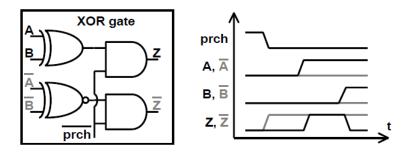

| 6 | Dua  | ıl Rail | chip design                                 | <b>56</b> |

|   | 6.1  | Varian  | nts of Dual Rail design                     | 56        |

|   | 6.2  | Simple  | e Dynamic Differential Logic (SDDL)         | 57        |

|   | 6.3  | Wave    | Dynamic Differential Logic (WDDL)           | 58        |

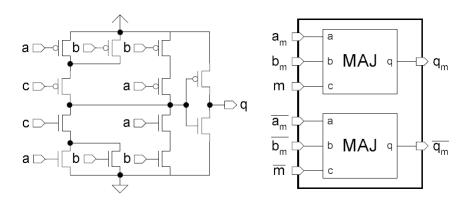

|   | 6.4  | Maske   | ed Dual-rail Pre-charge Logic (MDPL)        | 58        |

|   | 6.5  | Drawb   | oacks                                       | 59        |

|   |      | 6.5.1   | Vulnerabilities of MDPL                     | 59        |

|   |      | 6.5.2   | Effects on silicon area                     | 60        |

|   | 6.6  | Closed  | l source hardware implementation            | 60        |

| 7 | Atta | acking  | the exponentiation                          | 61        |

|   | 7.1  | Attack  | xer model                                   | 61        |

|   |      | 7.1.1   | Three techniques                            | 61        |

|   |      | 7.1.2   | ZEMD attack with the current implementation | 62        |

|   |      | 7.1.3   | MESD attack                                 | 63        |

|   |      | 7.1.4   | SPA attack before DPA approach              | 64        |

|   | 7.2  | Differe | ent implementations of the exponentiation   | 64        |

|   |      | 7.2.1   | Memory-efficient method                     | 64        |

|   |      | 7.2.2   | Square and multiply                         | 64        |

|   |      | 7.2.3   | Montgomery modular exponentiation           | 65        |

|   | 7.3  | Prepar  | red smart card                              | 66        |

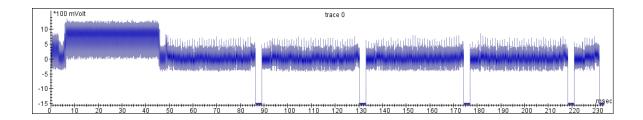

|   | 7.4  | Overv   | iew power trace                             | 66        |

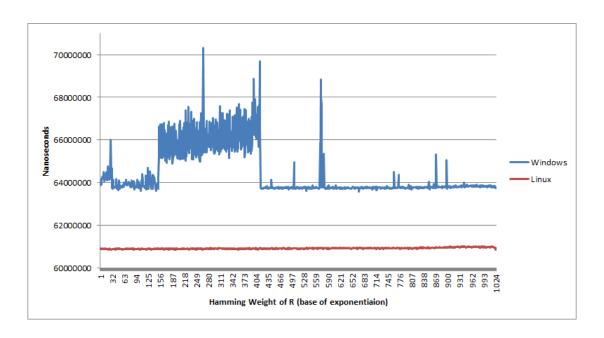

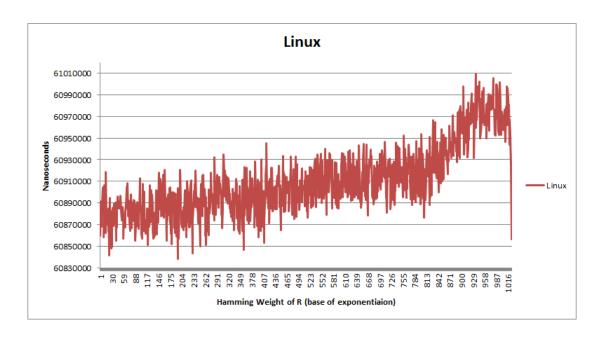

|   | 7.5  | Timin   | g differences                               | 67        |

|   |      | 7.5.1   | Influence of the base value                 | 68        |

|   |      | 7.5.2   | Influence of the exponent value             | 69        |

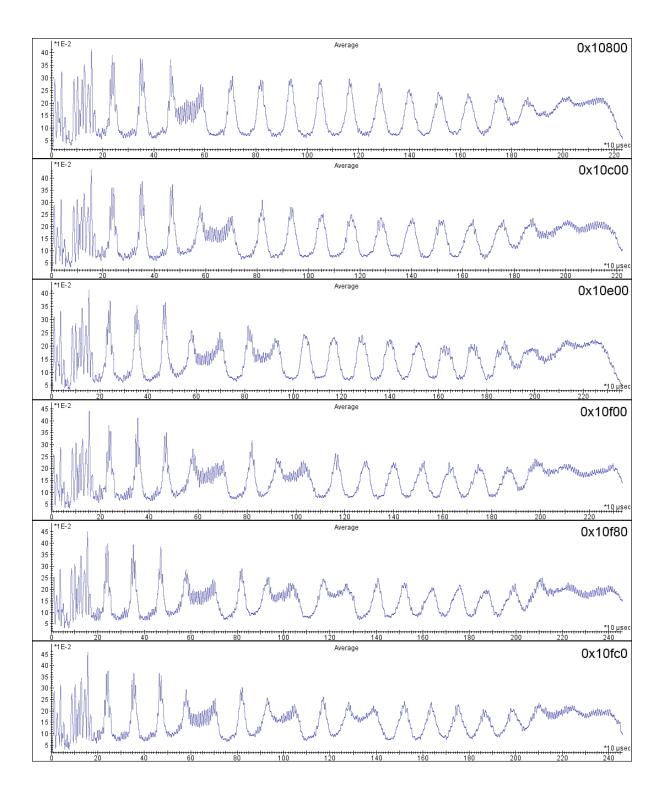

|   |      | 7.5.3   | Random instruction intervals                | 70        |

|   | 7.6  | Filteri | ng the signal                               | 72        |

|   |      | 7.6.1   | Changing the supply voltage of the card     | 72        |

|   |      | 7.6.2   | Usage of lower hardware Low Pass Filter     | 73        |

|   | 7.7  | Appro   | aches for extracting the operations         | 73        |

|   |      | 7.7.1   | Visual inspection method                    | 74        |

|   |      | 7.7.2   | Pattern matching method                     | 75        |

|   | 7.8  | SPA A   | Attack on the exponentiation                | 78        |

|   |      | 7.8.1   | One bit moving in secret key                | 78        |

|   |      | 7.8.2   | Adding bits to the right                    | 81        |

|   |      | 7.8.3   | Larger secret keys                          | 83        |

|   |      | 7.8.4   | Used Algorithm                              | 83        |

|   |      | 7.8.5   | Effect on the IRMA system                   | 84        |

|   |      | 7.8.6   | Software countermeasures                    | 85        |

| 8            | 3 Conclusions           |                       |            |        |        |      | 87  |

|--------------|-------------------------|-----------------------|------------|--------|--------|------|-----|

|              | 8.1 Multiplication      |                       |            |        |        | <br> | 87  |

|              | 8.2 Exponentiation .    |                       |            |        |        | <br> | 87  |

| 9            | Future research         |                       |            |        |        |      | 89  |

|              | 9.1 Supply voltage ou   | t of range            |            |        |        | <br> | 89  |

|              | 9.2 Effect of operation | n temperature         |            |        |        | <br> | 89  |

|              | 9.3 The attack on the   | Infineon SLE-78       |            |        |        | <br> | 90  |

|              | 9.4 What Dual-rail in   | plementation is used? | ?          |        |        | <br> | 90  |

| Aı           | Appendices              |                       |            |        |        |      | 91  |

| $\mathbf{A}$ | A Smart card code of i  | solated functions     |            |        |        |      | 92  |

| В            | B Riscure Inspector A   | cquisition class for  | the isolat | ed fun | ctions |      | 96  |

| $\mathbf{C}$ | C Code for performing   | timing test           |            |        |        |      | 100 |

| D            | O Generate possible ke  | eys for pattern and   | pattern f  | or key |        |      | 104 |

#### Abstract

When we need to prove our age, name or nationality, we need to show our identity card or passport. The person that needs to verify these properties can then view all our personal information and often makes a photo copy of this document. This violates our privacy and the IRMA card provides an answer to this problem. The IRMA card can be used to digitally prove properties about oneself by making use of selective disclosure of attributes. Only the attributes that need to be verified are shared with the verifier. The IRMA system is currently still under development but the basic protocol is already fully functional. This thesis presents the results of the conducted research on the possibilities of performing side-channel analysis attacks on the new IRMA card. The issued attributes are namely cryptographically bound to a master secret that should not be extracted from the IRMA card in any way. Through the protocol, computations with the secret key that is stored on the IRMA card have to be performed. These operations could leak secret key information through their power consumption. We found both a multiplication and an modular exponentiation which uses the secret key as operand. We isolated those operations and researched if a power analysis attack on these operations is possible. It turns out that for the Infineon SLE-66 smart card attacking the multiplication is difficult and no secret key information could be retrieved. For the modular exponentiation operation, a significant amount of information regarding the secret key could be retrieved by using Simple Power Analysis.

## Acknowledgements

I would like to thank Baris Ege for helping me with the practical part of this thesis and explaining me how to work with the Riscure Inspector. I would like to thank Pim Vullers for suggesting the topic for my thesis and providing me with background information regarding the workings of the IRMA system. I thank Kevin Reintjes, Willem Burgers, Petra Thijssen, Baris Ege and Pim Vullers for taking the time to review the draft version of this thesis. I would also like to extend my thanks to the people of Riscure for providing the Radboud University with the software and hardware for the side Channel Analysis.

## Chapter 1

## Introduction

In the Netherlands, the identity card that is issued by the Dutch government is used to prove several characteristics of ourselves. For example, proving your age to get reduction in museums or proving your age to be able to buy alcohol or tobacco is a common act. In most cases, the merchant will look at the picture to see if the identity card belongs to you and checks your age based on the date of birth that is printed on the card. In the situation of booking a hotel room, the receptionist wants to see proof of your full name. To have some proof that you were a guest at that hotel, the receptionist will often photo copy your identity card. From a security perspective, showing all data on the card when only one or two items are needed for the proof, is leakage of sensitive data.

This is not only a privacy concern, it also increases the risk of being a victim of identity fraud. To overcome this problem of revealing too much information for a specific proof, research on attribute-based credentials has been conducted at the Radboud University in Nijmegen. As a result of this research, the *I reveal My Attributes (IRMA)* card is developed. The basic idea of this new IRMA card is that the information can only be read digitally from the card and that the card holder needs to give read permission for reading a clearly specified set of properties (age, length, name, etc). This prevents the information leakage mentioned earlier. These properties of a person are called attributes.

At this time, the IRMA card and reader software is almost fully implemented and a small scale usage test with a few dozen students is performed at the Radboud University since november 2013<sup>1</sup>. Because the IRMA card has a secret key which is used to bind the attributes to this specific person (or actually this specific card, that belongs to a specific person), this secret key becomes valuable. When this key leaks, the non-transferability property of the attributes is broken meaning that people could copy attributes from one IRMA card to another. If this happens, the IRMA system is broken since it cannot be trusted any longer.

When the IRMA card is used in our daily lives, it will fulfil the purpose of an identity card. It will be used as the proof for attributes about ourself. The most important attributes are the attributes concerning your identity. They will be used to prove your identity if this is needed. If the IRMA card is broken, nobody is able to prove something about himself any more. If the secret key can be captured from the IRMA card, the attributes can be interchanged. The proof of your identity can possibly be forged and

$<sup>^1{\</sup>rm The~pilot~presentation~can~be~found~at~https://www.irmacard.org/wp-content/uploads/2013/11/The-IRMA-pilot-18-11-2013.pdf$

nobody is able to accept the IRMA card as a proof of your identity. This could disrupt the society and therefore it is of great importance to evaluate the security of the IRMA card in every imaginable way before we start using it.

In theory, it is possible to guess the secret key, and compare a simulation of the IRMA card algorithm with messages that the real IRMA card communicated with the terminal. If the result is the same for the simulation and the real card output, the correct secret key is found. If this comparison is done for a large set of possible secret keys, this is called a brute-force attack. Because of the length of the secret key of 256 bits, this would mean that you will need to try on average  $5.7896045*10^{76}$  possible values for the secret key. Performing this attack is infeasible because there are too many possible combinations. Though, all the information that we can learn about the secret key will limit the set of possible keys and make it easier to perform this brute-force attack.

One powerful way of gathering information about the inner workings of a smart card and the stored data on a smart card is by using side-channel attacks. Side-channel attacks analyse the information that is leaking from the smart card unintentionally. This can be in terms of sound, radiation, temperature or the power consumption of the card.

For example when you measure the power consumption of the smart card in great detail, the different power consumption patterns will leak information about the instructions that are being executed on the card. If the card performs actions with the secret key, some information about this key could leak through the power consumption. The IRMA smart card includes measures to prevent side-channel attacks, but the authors of the source code of the prototypes<sup>2</sup> are not quite sure that the card does not leak key information. In this document, we will look at the side-channel attacks that are possible with the current implementation of the IRMA card<sup>3</sup>.

## 1.1 Problem statement

In this thesis, we will look into possible weak points that we could attack using passive power analysis methods. The problem statement that is formulated is as follows:

Is the current implementation of the IRMA card susceptible to passive power analysis attacks?

The IRMA card is still under development. New functions are still added to the IRMA system to make it interesting for more and more use cases. Though, the mathematical constructions of the IRMA protocol for issuing and validating credentials will probably not change any more. Therefore, the IRMA protocol itself can already be analysed for possible leakages.

The smart card that will be used in the final IRMA card system is still something that could change. In earlier stages of the development of the IRMA card, the Infineon SLE-66 was used. Later on, due to higher memory constraints, the developers switched to the Infineon SLE-78. The Infineon SLE-78 will probably be powerful enough for the final IRMA system.

<sup>&</sup>lt;sup>2</sup>The still growing list of participants can be found at https://www.irmacard.org/people/

<sup>&</sup>lt;sup>3</sup>The repository with the current state of the IRMA card code can be found at https://github.com/credentials

In this thesis, we will focus on the Infineon SLE-66. The original plan was to look at both the Infineon SLE-66 and the Infineon SLE-78 card. Unfortunately, attacking the Infineon SLE-66 turned out to be a lot harder than expected. Due to time constraints, we were not able to conduct research into the Infineon SLE-78card9.3.

We will focus on passive power analysis attacks during this research. This *passive* means that we will not damage the IRMA card in any way. We will only try to gather information about the card using recordings of the power consumption of the card. This is something that cannot be detected by the card and could be performed by anyone with a reasonably small budget. Next to the category of the *passive* attacks, we have the *active* attacks. We will introduce these attacks shortly in section 1.5.

## 1.2 Organization of thesis

We will continue this chapter with some background information of the IRMA system and an introduction into power analysis attacks. In the next chapter, chapter 2, more details about the implementation of the IRMA protocol and the IRMA system are given.

At the end of chapter 2, two possible vulnerable operations of the IRMA card are identified. One is a multiplication operation with the secret key as a operand and the other is an exponentiation with the secret key as the exponent. After visiting the used attack method in chapter 3 and the used modules of the Riscure Inspector software in chapter 4, the results of attacking either the multiplication (Chapter 5) and the exponentiation (Chapter 7) are presented.

After that, we will look at the conclusions (Chapter 8) that we can formulate based on our research and we will wrap up with possible future research in chapter 9.

## 1.3 I Reveal My Attributes (IRMA) Concept

The aim of the IRMA project is that the IRMA card would serve as an alternative for the current identity card[Jac12, Jac]. The only information that is printed on the IRMA card is a picture of the owner and a (semi-secret) serial number that could be used to look up the owner of the card in case the IRMA card was lost. Note that this serial number is not stored on the card itself and can therefore not be used to link different proofs of the same card. The picture is printed on the card such that it can be verified in offline, face to face use cases, that the person using the IRMA card is really the person to which the card belongs to. You can see the design of the card in Figure 1.1. When the card holder needs to prove certain properties about oneself, he or she will show the outside of the IRMA card to the verifying party only to prove that the card really belongs to him. Other properties are verified using a digital proof.

For a high privacy value property, for example your social security number, the proof could also require a PIN code of the card holder. This "digital verification" of the property is not just reading out the information that is stored on the card in plain-text: the IRMA card focuses on enhancing the privacy of the card holder by implementing the functionality of only revealing one or a couple of attributes. For every transaction, a specific set of attributes is needed to be proven in order to complete this transaction. More importantly, with each transaction, there is often an even bigger set of attributes

Figure 1.1: Design of the front (left) and the back (right) of the IRMA card. Note that only the picture of the card holder is printed on the card.

that is not relevant to the verifier. These irrelevant attributes will not be revealed to the verifier during the proof.

# 1.3.1 Privacy and security shortcomings of the current identity card

It could be thought that using electrical equipment to prove certain properties about oneself is a bit of a hassle. Some people will even think that it will be an unnecessary time consuming process because the information that is printed on the current identity card is not really secret to them. They do not mind that the cashier of the liquor store is greeting them by their full name after they had to show their printed identity card to prove that they are old enough to buy liquor. They do not mind that their identity card is scanned when they check in at a hotel, because the hotel can be trusted. But you do not know for sure that they can be trusted and furthermore, in the case of the hotel, the scan of the identity card may be stored on a computer that is under control of a malicious attacker. This attacker could steal these scanned images and use them to commit identity fraud.

## 1.3.2 Universal platform

The IRMA card should become a universal platform for storing attributes on a personal card and revealing only those attributes that are required for the specific situation. A big privacy advantage of this approach, is that you do not show attributes that could uniquely identify you (for example your social security number) when the situation does not require these attributes. The card holder has more control over which attributes are shared with which party in which situation. Not only attributes concerning your identity could be stored on this card, it will also be possible to store attributes on the card that prove for example that you are allowed to access your office building, to board a specific plane or that you have bought a ticket for a festival. In the cases that there is no need to reveal a unique identifying attribute, this attribute-based method prevents linking of different proofs and implicit profiling.

## 1.3.3 New law proposals and IRMA

This concept of revealing only a selection of ones properties fits perfectly in the principles of privacy by data minimization and privacy by default. Currently, there is a European Directive concerning Data Protection (GDPR [gdp12]) proposed which will enforce these principles more strictly. It states that personal data is only to be collected for specified and explicit purposes and that it is always limited to the minimum necessary (Art. 5bc). Also, the person has to give explicit consent for the processing (in this case, the verification) (Art. 6a).

The IRMA card ensures that these principles are obeyed by the verifier. The verifier has to be explicit about which set of attributes are needed in order to complete the transaction. The verifier has to ask the card holder if he or she wants to use their IRMA card to prove that a certain attribute is present on the card. By cooperating in the IRMA procedure of proving that the attributes are on the card, the card holder is giving explicit consent to share this personal data. This is even a stronger notion in case a PIN code is entered for the transaction. The verifier will be forced to only ask the minimum of personal data that is needed for the transaction, because if the verifier demands to reveal unnecessary attributes to complete the transaction, the card holder will hopefully refrain from the transaction. The usage of a smart card with a PIN code should bring people in a natural way in a state of high alertness when deciding about these transactions. Also, the IRMA card uses ranges as much as possible instead of the exact value (for example the age), which also minimizes the personal information that is being processed.

## 1.4 Power analysis attacks

Power analysis attacks [MDSM02, MOP07, MDS<sup>+</sup>99a] are attacks that focus on the power consumption of a device. Most modern day chips are built using CMOS cells which have a dynamic power consumption. The power consumption during an operation depends on the type of operation and the input data. There is a noticeable difference between the transition  $0 \to 1$  and the transitions  $0 \to 0$ ,  $1 \to 1$  and  $1 \to 0$ . Based on the detection of the transitions  $0 \to 1$ , information about the input of the cell can be gathered.

This power is drawn from the power supply of the processor, which in the case of smart cards, is the external power supply of the terminal which communicates to the smart card. Because this power supply is outside the smart card, it can be controlled by the attacker. The power supply should be regarded as untrusted. Any information that is leaked through the power consumption rates of the smart card, can be used by an attacker to get a better understanding of the algorithms that are being executed on the card and which data is being processed.

When an attacker records the power consumption of the smart card in great detail, for example by using an oscilloscope, the attacker could get information that is processed by the card. This also means that secret keys that are used by the smart card during the algorithm could also be found based on these power traces. Which amount of data is leaked to the power source depends on several aspects. The smart card often has countermeasures built-in against this power channel leakage. These can be in the form of hardware countermeasures, but there are also several programming techniques that can prevent leakage to the power source. A programmer should therefore always keep

side-channel leakage in mind when working with sensitive data.

One passive attack that is more powerful than power analysis makes use of the ElectroMagnetic (EM) emanations of a chip. With power analysis, there is only one signal, captured from the line between the chip and the power supply. EM emanations are generated by all subparts of the chip. This means that the attacker has the physical location of the information leakage through the EM side-channel as extra information. If the attacker has knowledge of the design of the chip, he will be able to focus on the most interesting part of the chip to attack which improves the signal to noise ratio. This means that the useful signal is stronger than the noise signals and therefore more visible in the traces. This increases the likelihood that the attacker captures something which can be used to recover the secret key.

Power analysis attacks can be divided in three subclasses:

## • Simple Power Analysis (SPA) attacks Simple Power Analysis (MS00, MOP07)

Simple Power Analysis [MS00, MOP07] attacks focus on the fact that power consumption of a device is dependent on the instructions that it performs during the execution of the algorithm. SPA attacks are successful if the execution path of the algorithm is decided by the secret component. The SPA attacks are very simple to perform based on visual inspection of a single trace. If the instructions that are executed are dependent on the secret component, the attacker will be able to see which steps are taken in the execution path and determine which secret component fits for the execution path that is visible in the power trace. It is fairly easy to protect the algorithm against SPA attacks. Simply by ensuring that the execution path of the algorithms does not depend on the secret data that is being processed.

## • Differential Power Analysis (DPA) attacks

Differential Power Analysis [KJJR11, MOP07] attacks focus on the fact that the power traces are dependent on the data that is being processed. If the secret data component does not affect the execution path of the algorithm directly, it will not be directly visible in the power traces, but it could still be possible that there is a very small amount of secret information leaked to the power source. It is possible to extract this information with the help of statistics and error correction. By analysing the bias of the signal in a large set of power traces, the secret component can be found. Because the secret key is a static component in the computation, it will always consume the same amount of power with every computation. The other data values that are used in the computation are changing for every different computation and the power consumption will also be different for every value. By comparing these traces of different computations, the bias information will leak information about the secret key.

#### • Correlation Power Analysis (CPA) attacks

Correlation Power Analysis [BCO04] attacks are actually a subclass of DPA attacks and the term DPA is nowadays often used for attacks that are actually correlation based attacks. Correlation Power Analysis uses power consumption models to create hypothetical power traces for different secret key guesses. Based on calculating the correlation between these hypothetical power trace models and the real power traces, the key guess that matches the real traces the most will most probably be

the correct key. Because many operations on the chip will not be performed in one step but in multiple steps, which each have intermediate results, this correlation attack can be performed on a different intermediate result, splitting the problem in smaller problems with less complexity. Therefore, the key guesses can often focus on a particular part of the key, making the search space a lot more manageable.

In the rest of this document, we will not make the distinction between DPA and CPA. A successful attack on a smart card which is running a specific algorithm is often a combination of SPA, DPA or CPA. In most cases, the attacker uses SPA to determine which parts of the power traces are influenced by the actual algorithm steps that are using the secret component the attacker is looking for. After this, DPA is often used to extract (parts of) the secret that are hidden in the traces of this execution step.

## 1.4.1 Example SPA attack

**Algorithm 1.4.1:** SquareAndMultiply(x, b)

```

comment: Compute x^b

z \leftarrow 1

while b > 0

do \begin{cases} z \leftarrow z^2 \\ \text{if MSB}(b) \text{ is odd} \\ \text{then } z \leftarrow z \cdot x \\ b \leftarrow \text{SHIFTLEFT}(b) \end{cases}

return (z)

```

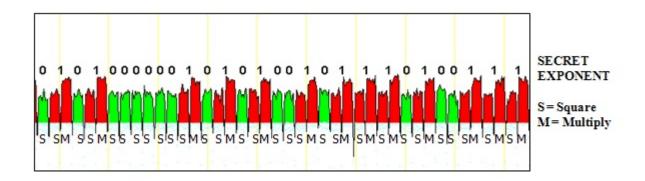

A clear example of an SPA attack is the attack on the Square-and-Multiply algorithm which could be used to perform exponentiation. This algorithm loops through (the bitwise presentation of) the exponent from the most significant bit to the least significant bit. For every next bit of the exponent, the intermediate result will be squared but it will also be multiplied with the base of the exponentiation if the bit is one. Because this extra multiplication step in the algorithm is an extra processor instruction, it can already be determined from a single power trace by visual inspection if the Square-and-Multiply round included an multiplication or not. If the exponent of this exponentiation is a secret key, for example with RSA<sup>4</sup>, The secret key could be easily discovered based on a single trace. The main reason for this is that the secret key data influences the execution path of the algorithm (modus operandi). So called Horizontal power analysis attacks could be applied in this case[BJPW13].

An example of such traces can be found in Figure 1.2. The parts of the trace which only consist of a low part indicate a zero in the exponent. The parts of the trace which consist of a low and a high part indicate a one in the exponent. The exponent of this calculation could therefore be read from the trace from left to right. This also holds for weak implementations for *Double-and-Add*, which is an algorithm for performing multiplication. Here, one of the two parameters will determine if the other parameter is added to the

<sup>&</sup>lt;sup>4</sup>The use of a modular reduction during the *Square-and-Multiply* will not affect the power channel leakage of this algorithm.

Figure 1.2: Example trace of an unprotected Square-and-Multiply algorithm execution where the exponent can be found by visual inspection [Roh10]

intermediate result after it is doubled in every round, in a similar way as with *Square-and-Multiply*. If this parameter is the secret key, it will also be visible in the power traces.

## 1.4.2 Example DPA attack

When attacking the AES block cipher, an SPA attack will probably not suffice. With this cipher, the secret key does not influence the execution path of the algorithm as much as with the SPA attack example. With this block cipher, there are multiple rounds which alter the plain text block based on the value for the secret key. After each of these rounds, there is an intermediate result that can be attacked with DPA. Often, when a visual inspection of the traces is performed, the different rounds of the AES algorithm can be discovered.

We will now assume that we have a reasonably large trace set of AES calculations using the same secret key and that we know the plain text used for every trace. Also the traces have to be nicely aligned such that the calculation of the different rounds are starting at the same time for every trace that is used for the attack. For performing a DPA attack any intermediate result which is a function between the plain text or the cipher text and the secret could be used. It is advisable to focus on an operation in the algorithm that has the least of a linear character. For AES, the most interesting operation to attack is the S-Box lookup, which is a lookup and substitution function based on a matrix of stored values. The attack is performed on a small part of the key at once, the first byte of the output of the first round of the S-box look-up. For this key part, all the possible values are calculated, called the key candidates. Only one of those key candidates is correct. In the case of attacking one byte, this will give 256 possible values. For all these possible key parts, the intermediate result is calculated based on the knowledge of the S-box of round 1 of the AES algorithm with the plain text for every trace as input. When we have an intermediate result for every trace, this intermediate result has to be converted into an estimation of the power consumption of this calculation. This is called the power model. There are different power models which simulate different processor designs. Which power model has the best effect strongly depends on the target. One of the power models that is often used is the Hamming Weight model, which represents the number of 1 in the bitwise representation of the intermediate result. When choosing the power model, you should try to be as specific as possible with modelling the device. A more precise model will require fewer traces for performing the attack.

If the traces are now compared with the power consumption estimates for each of the intermediate results, which are calculated based on the chosen power model, the key part that actually matches with the secret key will become visible. The estimate power consumption will clearly have a higher correlation in comparison with the power model estimates of the other key guesses. This difference in correlation is caused by the fact that the correlation graph of a lot of traces are averaged. Correlation values of power consumption estimates of the key guesses that are not correct will be random and cancel each other out during averaging of those correlation values. Therefore, the correct value for the key part will be found as a peak in the correlation graph.

### 1.5 Active attacks

The above mentioned power analysis attacks are all passive. This means that the attacker did not interfere with the normal execution path of the chip. With passive attacks, the attacker is limited to running the (by the manufacturer) intended operations on the card with different input values and analysing what the effect of these different values will be on the output and the side-channel leakage. Though, attacks could often be faster or more effective when the attacker is able to change small parts of the intermediate values on which the chip is working. Because this change of values inflicted by the attacker is unwanted behaviour of the chip, it is called fault injection.

Security algorithms that are running on the chip often have multiple rounds where some operation based on the cards secret is applied multiple times on some intermediate value. If in one of the first rounds an error of only one bit flip is injected, this error will propagate through the other rounds and eventually could have a total different output result than the normal execution of the chip would give. Based on knowing where the bit is flipped during the execution by timing the fault injection very precisely and analysing the differences between the correct output and the faulty output, the cards constant secret could be revealed. People nowadays have a lot of ways in which they can inject a fault into a chip.

Because the chip gets smaller and smaller and the current that the chip may consume for the calculations is increasingly limited, only a relatively small external influence could already cause a bit flip to occur. this could for example be achieved by means of dropping or spiking the current supply, applying a laser beam, changing the operating temperature, etc. [BBKN12]. To detect these environment fluctuations, the high security smart cards are fitted with a large set of sensors. We will have a look at the different sensors in section 2.6.

We will not focus on this kind of attacks because it requires more specialized equipment and a lot of IRMA cards. Performing active attacks on smart cards will possibly damage the card irreversibly. An average attacker will probably not be able to acquire a large set of IRMA cards without raising suspicion by the card issuer.

## Chapter 2

## IRMA system

## 2.1 Stakeholders

To get a better understanding at which point the IRMA system is possibly vulnerable to Side-Channel Analysis attacks, we need to have a look at the different parties in the system and which algorithms are used for the different protocol steps. There are four different types of stakeholders in the system [AJ13]:

#### • Card Holder (the user)

The Card Holders are the people who use the IRMA smart card to prove to the credential verifiers that they possess a certain property at a certain moment. The card holder will need to do this because the card verifier will require him to do so in order to complete the transaction that the card holder has initiated.

#### • Credential Issuer

The credential issuers compose the attribute containers, called credentials, which include certain attributes which represent the properties of the card holder at a certain moment or for a certain timespan. The credential issuer makes sure that the attributes that are included in the credential are valid for the current card holder and signs the credential. This signature proves that the attributes that are stored in the container are valid until the expiry date, that is also a part of the credential. It can also be that the issuer is at the same time a credential verifier. To make sure that the current card holder is the person for which the new credential is destined, other credentials could be consulted. In this case, the issuance of the credential will have multiple steps.

#### • Credential Verifier

The credential verifier is the party that requires proof for a certain property of a person to complete a transaction with that person. These properties are stored in the form of attributes in a credential on the IRMA card. During verification, the credential verifier has a set of attributes that need to be present (the disclosure selection  $\mathcal{D}$ ) and sends this to the IRMA card of the holder. The answer of the card is a proof of the credential which contains the disclosed attributes accompanied with a signature of the issuer that has issued these attributes. The verifier can

now check the validity of the proof and can check if the issuer which has signed the credential can be trusted.

#### • Scheme Manager

The scheme manager is the highest authority in the system. The scheme manager determines the rules for the other stakeholders in the system, for example which parties may issue which kind of credentials and the dependencies among the different kind of credentials. The scheme manager also initializes the smart cards that are going to be used for the IRMA system. These tasks could be split up into different organizations when the system is being used on full scale.

## 2.2 Idemix or U-Prove

For the selective disclosure of attributes on smart cards, two different technologies are currently available. Jan Camenisch and Anna Lysyanskaya at IBM Research Zürich developed the Identity Mixer (Idemix) in 2002 [CVH02, CL03] and Microsoft has introduced the U-Prove technology in 2011 [Paq11] (originally developed by Stefan Brands [Bra00]). Both technologies are based on so called credentials. These credentials are containers of a number of attributes that is signed by the issuer of these credentials. For example, a credential that could be issued by the government could hold the attributes: "Dutch citizen", "Male", "Over 18 years old" and "Born in Nijmegen". Selective disclosure is a verification technique, which makes it possible to reveal only a subset of the attributes in this credential to the verifier.

The cryptography behind the credential-as-container concept ensures the following aspects:

#### • Authenticity

Because the credentials are signed by the issuer, the origin of the credential can be checked. The issuer of the credential guarantees that it only issues credentials with attributes that hold for the receiving person.

#### • Integrity

Based on the issuer signature on the credential, it can be checked if the contents of the credential are the same as it were at the time that the credential was issued.

#### • Non-transferable

During the issuance, the credentials are bound to the person that is receiving the credential based on the secret key of that person. Because of this, the credentials are not transferable if we can assume that the secret key is safe in all times. This is the property that could be broken if we could extract the secret key from the IRMA card through side-channel attacks.

#### • Hiding

The credential hides all the attributes that are not disclosed to the verifier.

#### • Issuer unlinkability

No information that is shared with the issuer can be used by the the issuer or

verifiers to trace the credentials back to the issuance of that credential. This is even the case if the issuer cooperates with all the verifiers. This is beneficial for the privacy of the owner of the credential because otherwise, the verifier could use this information to roughly identify the owner based on the issuer of the card (without the explicit permission of the owner).

#### • Multi-show unlinkability

If attributes of the same credential are being revealed to the verifiers multiple times, the verifier should not be able to link these two reveal sessions together. Even if all the verifiers cooperate, they should not be able to determine in which sessions the same credential is used. This is beneficial for the privacy of the owner of the credential because, otherwise, tracking and profiling of the owner is possible.

With both U-Prove and Idemix, a selective disclosure protocol implementation, that has all the properties mentioned above, could be created. Wojciech Mostowski, Pim Vullers and Gergely Alpár have conducted research into these two approaches [VA13, MV12]. Both protocols can be seen as signed commitments.

There are some important differences between U-Prove and Idemix. The most important difference, is that with U-Prove, the full credential is revealed with every verification. When this credential does not change, the verifier will be able to link verification sessions together based on this credential. If we want to accomplish the multi-show unlinkability property with U-Prove, for every verification in the future, a new (randomized) credential should be created and stored on the smart card on issuance. Also, for U-Prove, there should be one secret key stored on the card per credential.

This is not the case for Idemix. Because Idemix makes use of randomisable credentials, the credentials shown to the verifier could be randomized with blinding factors. Therefore only one credential has to be stored on the card and this can be verified multiple times without breaking the multi-show unlinkability. Also, the Idemix credentials can all use the same secret key for the binding of the credential to the card. This means that the smart card only contains one master key that is used for all the credentials. The U-Prove implementation was more efficient than the Idemix implementation in terms of speed. The speed of the transaction is also important for the IRMA card because the card can only be a success when it is user friendly. If the transactions take too long, the user could become impatient and disrupt the connection between the terminal and the card. This will result in many retries before the transaction completes and this will dissatisfy the user. When the verification of attributes takes too long, the IRMA card will probably not be accepted by the public for daily use. Though, because of the importance of the multi-show unlinkability and the limited availability of memory on smart cards, Idemix has been chosen for the IRMA card project.

## 2.3 IRMA Configuration

#### 2.3.1 IRMA Protocol overview

The operation of the IRMA system can be divided in different phases. Each phase in the IRMA system is an interaction between two parties of the system. The algorithms that are used for the different protocol steps can be found in the technical documentation of the IRMA system [Vul12]. The algorithm numbers in this section are references to the algorithm description in this technical documentation. In this section, we will give a bird's-eye view of the different steps in the protocol and focus on the points in the protocol where the secret key is used. For full algorithm descriptions the technical documentation can be consulted.

Depending on the parties that are interacting, the algorithm is implemented on the client (a terminal device or an online service) or on the IRMA card. We will now look at an overview of these phases with for each phase the algorithm steps that are being taken:

#### • Production of the IRMA smart card

The IRMA application has to be loaded on the smart card. This is done by the Scheme Manager. The operating system of choice for the IRMA card is Multos (We will look into Multos further in section 2.8.1). The change of Multos applications is protected by the Multos secure smart card deployment and management mechanism. This mechanism is based on a public key infrastructure which ensures that the applications on the card cannot be changed by anyone else than the scheme manager.

#### • Issuing the IRMA card

The issuance of the IRMA card is technically not that different from issuing a credential. Because the card has to be bound to the new owner of the card, a basic credential will be issued with the most important personal information of the owner. The IRMA card is issued when the first credential is placed on the card. The only part where the issuance of this first credential is different from credentials by other issuers is that the master secret needs to be generated on the card. This master secret is a 256 bit random key. In the Idemix set-up, this master secret will be used for all the credentials on the card.

#### • Issuing a credential

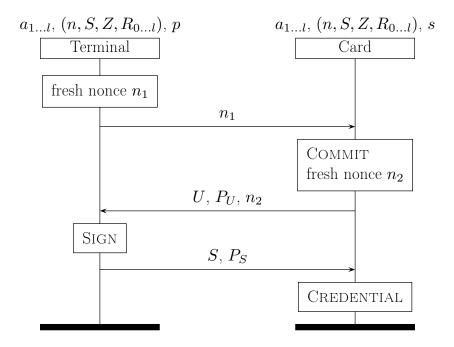

Before the credential has to be created, some verification of both parties has to be performed. An overview of the protocol steps can be found in Figure 2.1. The new credential has to be bound to a specific card and to this specific card only. The issuer wants to have proof that the new credential that is being created can only be used by this particular card. Therefore, the issuance protocol can be divided in a number of steps:

#### - Nonce generation

Because the issuer also needs to make sure that the issuer is really communicating to the correct IRMA card and not receiving copied responses from another session (replay attack), a random number only used once (nonce)  $n_{n1}$  is generated and communicated to the card.

#### - Card commitment

To bind the new credential to the IRMA card, a derivative of the secret key has to be included in the credential. This is done such that the credential cannot be transferred to any other IRMA card. The new credential has to be bound to the secret key of the current IRMA card. This cannot be done

by just sending over the secret key (because the secret key may never leave the card in any way) and therefore is done with a commitment scheme. The derivative is computed by generating a random value v' and calculating the following:

$$U \leftarrow S^{v'} \cdot R_0^s \bmod n \tag{2.1}$$

Here s is the secret key of the smart card,  $R_0$ , n and S are part of the public key of the issuer and therefore known to the terminal and the IRMA card. Without the secret key of the card, the issuer is not able to verify the correctness of this commitment U. The issuer does not have the secret key and, therefore, a non-interactive proof of correctness  $(P_U)$  is also computed (Algorithm 3). During the generation of this  $P_U$ , another derivative of the secret key is calculated by computing:

$$\hat{s} \leftarrow \tilde{s} + c \cdot s \tag{2.2}$$

The c in this computation is a hash over contextual information of the current commitment. The s is the master secret key of the IRMA card and  $\tilde{s}$  is an extra blinding factor which is randomly chosen. The resulting  $\hat{s}$  is part of  $P_U$ , together with c and shared with the issuer. With this  $P_U$  and U, the issuer is able to verify if the commitment U is valid (Algorithm 5). This is done by constructing the expected hash over the contextual information of the commitment and comparing this value with the c which is included in the proof  $(P_U)$ . After this step, the issuer has a correct set of derivatives of the secret key of the IRMA card which can be used for the creation of the credential.

#### - Issuers signature

Before the IRMA card can accept the credential, the card has to make sure that the issuer is valid. The issuer now needs to sign the commitment that is established in the previous step (Algorithm 6). To make sure this signature is fresh, the card has generated a nonce  $n_2$ . The scheme that is used for this signature is the Camenisch Lysyanskaya (CL) signature scheme [CVH02]. This means that the signature (S) also has to be accompanied with a signature proof  $(P_S)$  in order to be able to validate the signature (Algorithm 7). The card can validate the signature that is generated by the issuer (Algorithm 9) based on signature proof  $(P_S)$  and the public key information that is stored on the card by the scheme manager during the production of the card.

#### - Credential construction

If the signature of the issuer is validated, the actual credential is constructed. This credential also needs a signature which is constructed based on the signature on the commitment of both the card and the issuer (Algorithm 10). After this step, the credential is being verified once again by the card (Algorithm 11). If this verification succeeds, the credential is valid and stored in the non-volatile memory of the IRMA card.

Figure 2.1: Schematic view of the protocol steps during credential issuance [Vul12].

#### • Selective disclosure of (an) attribute(s)

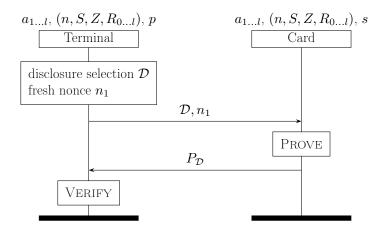

When a verifier wants to make sure that a particular set of attributes apply for a certain IRMA card owner, the procedure of selective disclosure is started. An overview of the protocol steps during this procedure can be found in Figure 2.2. The procedure can be divided in three steps:

- Establishing the set of selected attributes Based on a known set of possible attributes, the verifier establishes a set of attributes that it needs to verify. This set is called the Disclosure Selection ( $\mathcal{D}$ ). This set is sent to the IRMA card, together with a nonce. This nonce  $n_1$ ensures that the proof that is requested from the card is fresh.

- Generating proof for the selected attributes

In this step, the IRMA card is constructing a proof that the requested attributes (D) are in the credential that is stored on the card (Algorithm 12).

The card will not simply provide the credential, because there will also be attributes in this container which do not need to be communicated with the verifier. The card will also return a proof if the credentials are not on the card. That the requirements are not met will be clear to the verifier if the proof is verified in the next step. During the generation of this proof, the same multiplication with the card's master secret is performed as during the card issuance procedure 2.2.

- Verifying the proof for the selected attributes Based on the proof  $P_{\mathcal{D}}$  that is retrieved from the card for a Disclosure Selection  $(\mathcal{D})$ , the proof is validated by the verifier (Algorithm 13). If the result is invalid, it will only be clear to the verifier that the requirements are not met, not which attribute is not present.

Figure 2.2: Schematic view of the protocol steps during selective disclosure of attributes [Vul12].

#### 2.3.2 Commitment Scheme

A commitment scheme [Sch12] is used in a situation where two parties (A and B) want to agree on a certain value without the actual value being clear to the other party directly. When the value is communicated to the other party directly, it could influence the choice of the other party. Because of this possible advantage, the order of communicating the value could influence the result (who is showing their value first?). A commitment scheme splits this process into two parts. One is called the commitment phase and the other is the reveal phase.

#### • Commitment phase

Both parties choose a value and apply a commitment function to this value, in combination with a random number. The resulting commitment is sent to the other party. After this step, the chosen value of both parties cannot be altered.

#### • Reveal phase

In this step, both parties send the actual chosen value (and the random numbers used for the commitment function) to the other party. The chosen value cannot be derived from the commitment but the commitment can be used to validate if the value received was not changed after the calculation of the commitment.

The commitment function that is used here should not be just any function. The function should be binding and hiding. Binding means that there is no possible way for A to come up with another value that results in the same commitment that was already sent to B. If the commitment fits the value that is received in the reveal phase, then the revealed value was really the value that A chose initially. Hiding means that if A commits to a certain value and sends the commitment to B, then there is no way for B to gather information on which value was chosen by A until B receives the actual value.

In the IRMA system, a commitment scheme is also used but in a different form. In the IRMA protocol, there is not a real reveal phase. The IRMA Card and the issuer both need to pick a certain derivative of their secret keys. They will never reveal these secret keys but instead, they will prove that those commitments are derivatives of their secret keys. Though, from the moments that they have chosen the commitments (the

$$\begin{array}{c} \text{Prover} & \text{Verifier} \\ (x = \log_g h) \\ u_1, u_2 \in_R \mathbb{Z}_n \\ a_1 \leftarrow g^{u_1} \\ a_2 \leftarrow g^{u_2} & \xrightarrow{a_1, a_2} \\ & \leftarrow \\ r_1 \leftarrow_n u_1 + c_1 x \\ r_2 \leftarrow_n u_2 + c_2 x & \xrightarrow{r_1, r_2} \\ & & g^{r_1} \stackrel{?}{=} a_1 h^{c_1} \\ & & g^{r_2} \stackrel{?}{=} a_2 h^{c_2} \end{array}$$

Figure 2.3: Schnorr's protocol in parallel composition.

derivatives of the secret key), it is not possible for both parties to use another value of the commitment in any of the following steps in the protocol. The proof to the other party that the signature is really made with knowledge of the secret key is done by making use of zero-knowledge proofs.

## 2.3.3 Zero-knowledge proof

For both the signature of the issuer U as well as the signature of the smart card S, a proof is provided. For the issuer, this proof is called  $P_U$  and for the smart card  $P_S$ . These proofs are zero-knowledge proofs. Zero-knowledge proofs are proofs where both the prover and the verifier do not give away any other information, other than if a statement is valid or not. These statements do not concern the secret directly, but are statements about the prover having knowledge about the secret key. The challenge of zero-knowledge proofs is being able to prove that you have knowledge about a secret without revealing (parts of) the secret itself.

When such a proof is used for validating knowledge of a certain secret, there is no risk that an attacker could learn something about the secret by pretending to be the verifier because no information about the secret is shared during the proof.

A protocol that is based on a zero-knowledge proof is called a zero-knowledge protocol. The most popular variant of a zero-knowledge protocol is the Schnorr protocol. In this protocol, the prover has to prove to the verifier that it has knowledge about a discrete logarithm x. The computation of a discrete algorithm for h within a group g is a hard problem. This is defined as the Discrete Logarithm (DL) assumption:

The Discrete Logarithm (DL) assumption for group  $G = \langle g \rangle$  states that it is hard to compute x given generator g and random group element  $g^x$ .

An example of a Schnorr protocol is the Schnorr protocol in parallel composition [Sch12] which can be found in Figure 2.3. The Schnorr protocol makes use of this DL assumption and proves that it has knowledge about a certain x by calculating two chosen

derivatives  $(r_1 \text{ and } r_2)$  based on two random values  $(c_1 \text{ and } c_2)$  which are chosen by the verifier. The verifier can validate that the prover has knowledge of x because it can validate  $g^{r_1} \stackrel{?}{=} a_1 h^{c_1}$  and  $g^{r_2} \stackrel{?}{=} a_2 h^{c_2}$ . If the prover was able to compute these  $r_1$  and  $r_2$  correctly, then the prover must know the x. Otherwise, according to the DL assumption, the prover will not be able to compute these values. He does not give away any information about the x value because with knowing the values for  $r_1$  and  $r_2$ , the problem of solving  $x = log_q h$  is not made easier.

The IRMA system does not use the Schnorr protocol in combination with the DL assumption for the zero-knowledge proof but it uses the Strong RSA assumption where the order of the group is unknown. More about this assumption can be found in the next section.

## 2.3.4 Camenisch Lysyanskaya signatures

The Camenisch Lysyanskaya (CL) signature scheme [CVH02] is a signature scheme for Public key cryptography based on RSA [RSA78]. With public key cryptography, users in the system have a private key and a public key. This public key is published and everybody is able to validate a signature from this user. To generate a signature, the private key is needed. Because it is assumed that the private key is only known to the corresponding user, it can be assumed that the user really signed a document when the signature validates correctly with use of the user's public key.

The CL scheme works as follows:

#### • Key generation

Two large prime numbers p and q are chosen such that they have a length of  $\frac{l_n}{2}$  and such that  $\frac{p-1}{2}$  and  $\frac{q-1}{2}$  are also prime. The RSA modulus can then be computed by  $n=p\cdot q$  which will have the length  $l_n$ . The value for p will be the secret key, the other numbers can be recalculated when they are needed. The public key (PK) can be generated by choosing three values (a,b,c) uniformly at random from the set of quadratic residues modulo n ( $\mathcal{QR}_n$ ). So S=p and PK=(n,a,b,c) where  $a,b,c\in\mathcal{QR}_n$ .

#### • Generating signature

When a message m of length  $l_m$  has to be signed, a prime number e of length  $l_e \ge l_m + 2$  is chosen. Also a random number s is established with length  $l_s = l_n + l_m + l$  where l is a security parameter. The signature is then computed with the following equation:

$$v^e \equiv a^m \cdot b^s \cdot c \bmod n \tag{2.3}$$

The signature that is generated for a message will be a tuple (e,s,v).

#### • Validating signature

When a signature (e,s,v) needs to be checked for validity for a message m, the same equation as used for the generation of the signature could be used. Another thing that has to be validated is that  $2^{l_e} > e > 2^{l_e-1}$ .

This CL signature scheme is based on the strong RSA assumption. Finding a value for v and e in the left side of the equivalence 2.3 that fits the result of the right side of

the equivalence is hard. When a user knows the secret key p, it becomes a lot easier to generate this v and e value.

The strong RSA assumption is formulated as follows [CVH02]:

The strong RSA assumption states that it is hard, on input an RSA modulus n and an element  $u \in \mathbb{Z}_n^*$  to compute values e > 1 and v such that  $v^e \equiv u \mod n$ .

#### 2.3.5 Fiat-Shamir Heuristic

The Fiat-Shamir Heuristic is a way of using an interactive zero-knowledge protocol as a non-interactive zero-knowledge proof [Vul14, FS87]. This non-interactive zero-knowledge proof can be used as a signature.

During a standard interactive zero-knowledge proof, the prover and verifier have to communicate (interactive) the challenge c. Fiat and Shamir published a method where both the prover and the verifier could calculate a challenge based on hashing information that they already know. This means that there is no extra communication step necessary where the verifier shares the challenge with the prover. This speeds up the protocol significantly, because communication between the smart card and the terminal of the verifier is relatively slow. Any speed gain of the IRMA protocol is therefore beneficial for the usability of the IRMA system. The challenge is included in the final proof, so it could be validated by the verifier that the expected challenge was used for the proof.

## 2.4 Current IRMA implementation

The current implementation if the IRMA card can be found at the Github page https://github.com/credentials. We will now look at some developments of the current state of the IRMA system.

## 2.4.1 Small scale usability experiment

As mentioned earlier, the Radboud University started a test with the current implementation of the IRMA card in November 2013. A few dozen students are testing the IRMA card with online and offline services. Offline, they are able to use an IRMA card for discounts on coffee at the Radboud University and at the University of Twente. Also, the students that have the IRMA card can benefit from free printing using the IRMA enabled printer at the Radboud University.

To test the online verification service of the IRMA card attributes, the developers of the IRMA system have set up a wiki page<sup>1</sup> with information about the developments in the IRMA project. Only students with the required Wiki access attribute loaded on their card can get access to this wiki.

The main focus of this project is to test the reliability, usability and human perception of the IRMA card.

For the online services, an NFC reader is needed to communicate with the card. Luckily, current smart phones are equipped with an NFC reader, a camera and an internet

http://wiki.pilot.irmacard.org/

connection. To use this reader, the IRMA team created an Android app<sup>2</sup>. When an attribute needs to be verified by a website, the session information is transferred to the android phone by scanning a QR code from the computer screen. Based on this session information, the phone connects to the website's IRMA service and the validation process is started on the android phone. By reading the IRMA card with the phone, the presence of the attribute is verified. To make sure the right person is using the right IRMA card, the IRMA card PIN could be requested by the phone. The android phone only acts as remote hardware here, the verification of the information communicated by the IRMA card will still be done by the website's IRMA service.

## 2.4.2 No authentication for public keys

For validating the signatures, the IRMA card needs to have public keys of the issuers. These public keys are attribute dependent. Every possible attribute needs to be included in the attribute set which comes with the public key. The set of possible attributes for the IRMA card is not fixed, the IRMA system should provide the flexibility for the issuers to issue their own attributes (for example festival tickets). Because this set of possible attributes and the set of issuers cannot be known before the IRMA card is issued, the public keys cannot be stored on the card by the scheme manager during the installation of the IRMA system smart card application. The public keys need to be updated when the IRMA card is in the field.

For the current implementation, there is no authentication for accepting the public keys yet. The IRMA card will accept all the public keys that are sent to it. This will result in extra attack possibilities, which we will elaborate some more in the sections 2.9.2 and 7.1. The developers of the IRMA card are planning to implement authentication for uploading the public keys to the IRMA card before the final system is launched, but they want to focus on the performance and security of the main protocol first.

## 2.5 IRMA hardware

#### 2.5.1 Infineon SLE-66

#### Technical specifications and built-in attack prevention measures

We will now give a list of the technical specifications of the Infineon SLE-66 that are the most interesting for our research.

- Intel 8051 instruction set compatible

- Dual-interface controller for contact based and contact-less applications

- 8/16-bit CPU

16-bit processor with 8 bus lines.

- Frequency Range up to 30 MHz

Internal clock can be set by the card issuer, frequencies possible up to 30 MHz.

<sup>&</sup>lt;sup>2</sup>Available for download at: http://wiki.pilot.irmacard.org/Android\_Applications

- -25 to 85° C operation temperatures.

- Voltage range 1.62 V to 5.5 V

The card will work with a voltage supply between 1.62 and 5.5 Volts.

- Enhanced instructions for the addressing of memory >64KB

- 1100-Bit Advanced Crypto engine Supporting RSA and Elliptic Curve GF(p), certified RSA 2048-bit library available.

- 112-Bit Dual Key DES accelerator supporting DES and 3DES Algorithms.

#### Known vulnerabilities

At the Black Hat conference in Washington D.C. of 2010, Christopher Tarnovsky presented his work of successfully performing an active and invasive attack creating connections to the bus lines of the Infineon SLE-66 CL PE chip [Tar10, Ken10]. By changing the instructions that the chip performs, Tarnovsky was eventually able to read out the full memory of the chip, including the secret information that the chip stores. However, his attack required a significant amount of effort. He worked approximately nine months on the attack and for his attack he was able to use a Focused Ion-Beam workstation. This workstation costs \$350,- an hour to operate.

Most time was spent on bypassing the circuit mesh that is added to one of the top layers of the chip (Infineon calls this the Active Shield in their chip specifications). This mesh consists of five zones which each have four active circuits. If a line of this mesh is broken or makes contact with another conductor, the chip would stop working. During the attack, Tarnovsky had to drill through the mesh to reach the bus lines, but before he could do this, he had to bypass the mesh lines to trick the chip into believing that the mesh was not damaged.

#### 2.5.2 Infineon SLE-78

#### Technical specifications and built-in attack prevention measures

We will now give a list of the technical specifications of the Infineon SLE-78 that are the most interesting for our research[AG10].

- Intel 8051 instruction set compatible

- Dual-interface controller for contact based and contact-less applications

- Dual encrypted-calculation 16-bit CPU

- Frequency Range up to 33 MHz

- Crypto @2304T Crypto Processor

RSA up to 4096 bit, ECC up to 521 bit. DPA/SPA and DEMA/SEMA (Electro Magnetic radiation analysis) countermeasures.

- Symmetric Crypto Processor (SCP) for 3DES and AES 256 acceleration

- -25 to 85°C operation temperatures.

- Integrity Guard Security System [inc12]

- Memory Management Unit with level concept, True Random Number Generator

## 2.6 Hardware countermeasures of IRMA cards

The smart cards that are being used for the IRMA project are so called high security smart cards. These smart cards have chips that are full of sensors with the purpose to detect invasive attacks. Besides these sensors being added to the chip layout, the sensors are also checked with a live test function. If a sensor is damaged or removed, which could be part of an attack process, the chip will not function again.

#### 2.6.1 Active Shield or Mesh

The smart card chips are shielded by means of a so called Mesh (or active shield). This mesh acts as a very dense network of conducting lines. It should make drilling into the surface of the chip to eavesdrop into the internal communication (by connecting tiny wires) very hard. If only one line breaks or makes contact with one of the other lines, the intrusion procedure will start. This is mainly added to protect the bus of the chip. Through this bus, information is moved from processor cache to RAM or EEPROM memory and other peripheral devices that are also on the chip. The secret information will therefore also pass through this bus and when an attacker connects to these bus lines he is able to dump all the memory, including the secret keys.

## 2.6.2 Optical sensors between critical chip parts

Key information can also be extracted by applying fault injection as we have already addressed shortly. One way to introduce these errors during the operation time of the chip is by applying a strong laser beam to it. The energy of the photons in that laser beam is capable of charging a transistor and thereby applying a (for the processor unwanted) bit flip. As we have stated earlier, a single bit flip could propagate through to the output and could give away a lot of key information to the attacker. To make sure that this propagation stops before the output is given, optical sensors are added to the chip design. When these optical sensors sense light, it could probably indicate an attack. Normal daylight would not penetrate through the chip's upper layer. When the sensor is triggered, the chip will immediately stop working.

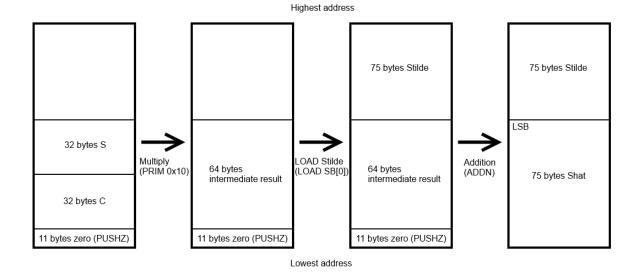

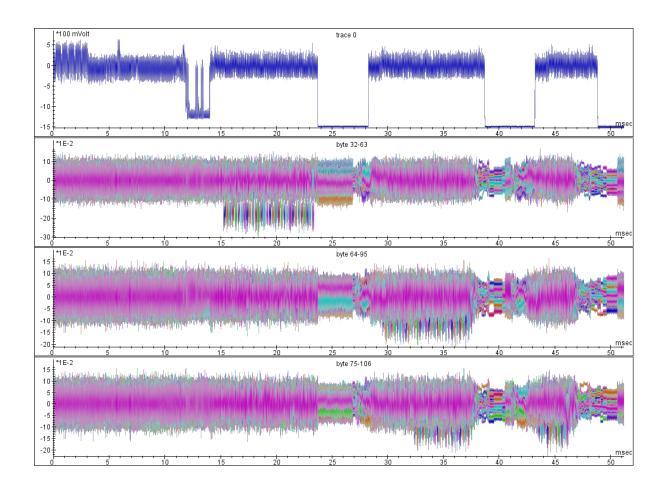

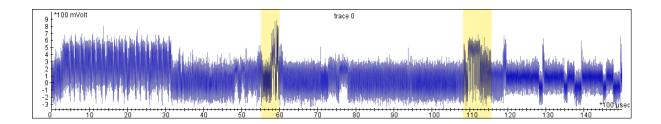

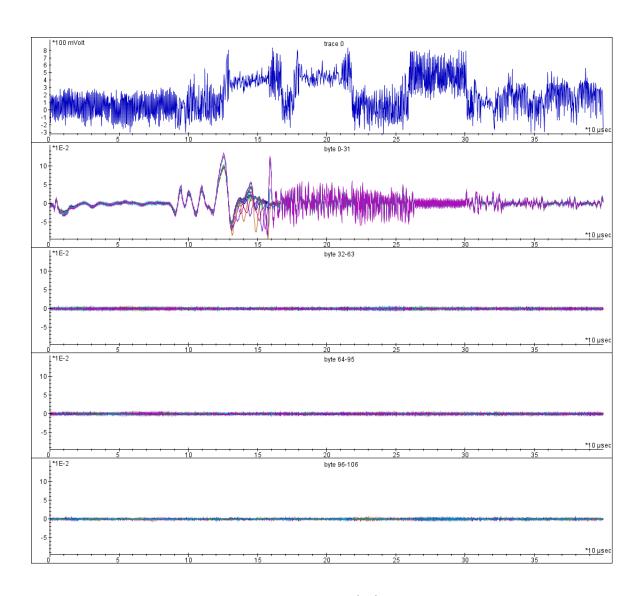

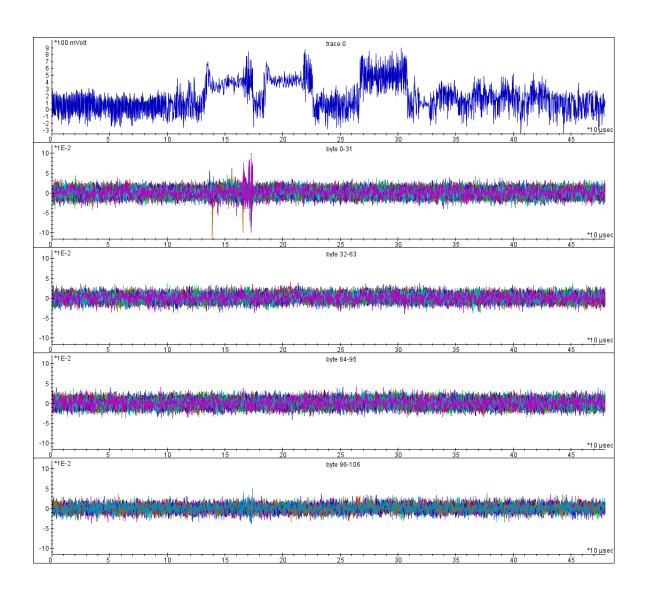

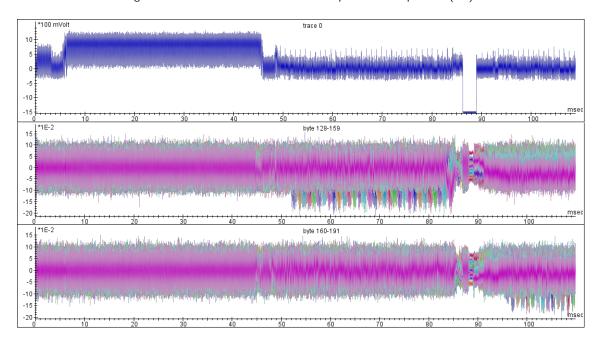

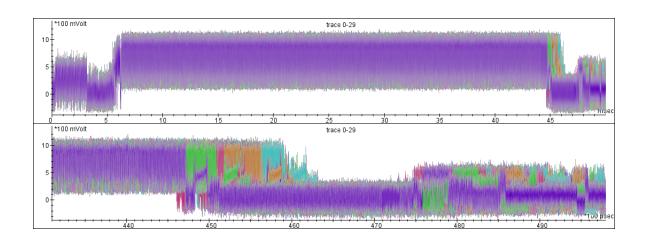

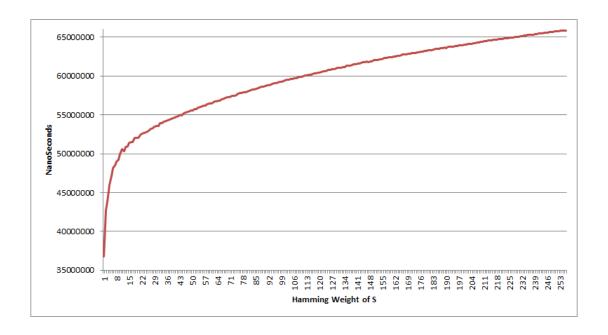

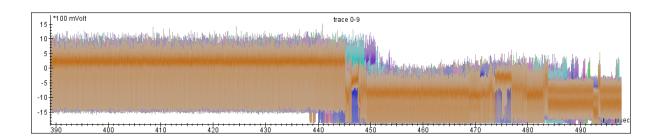

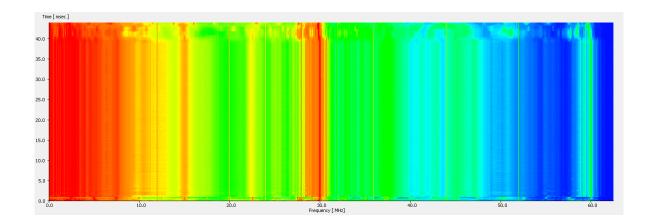

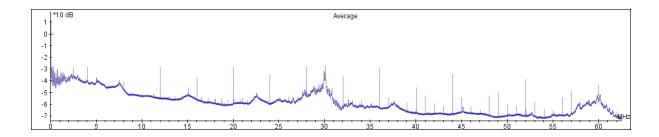

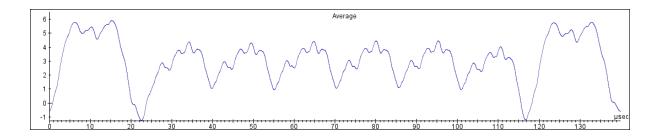

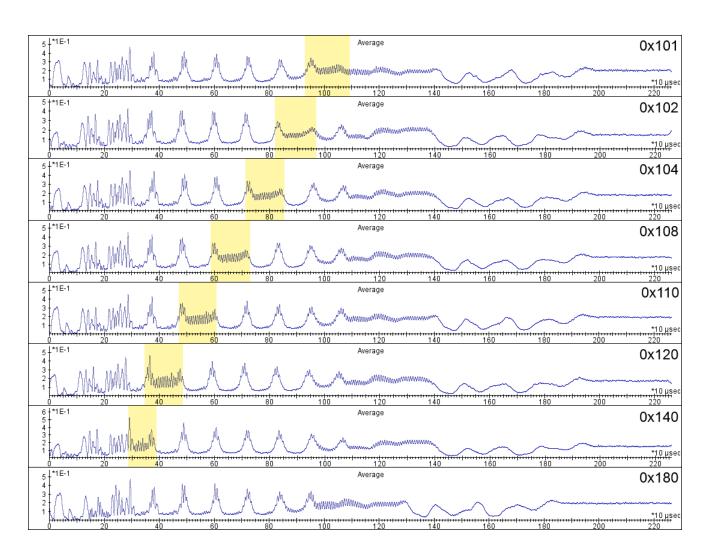

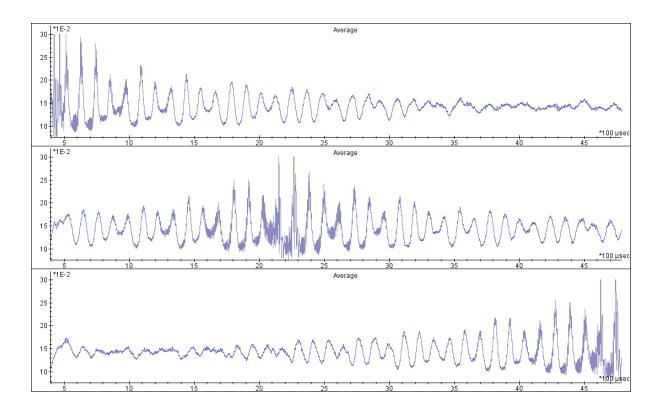

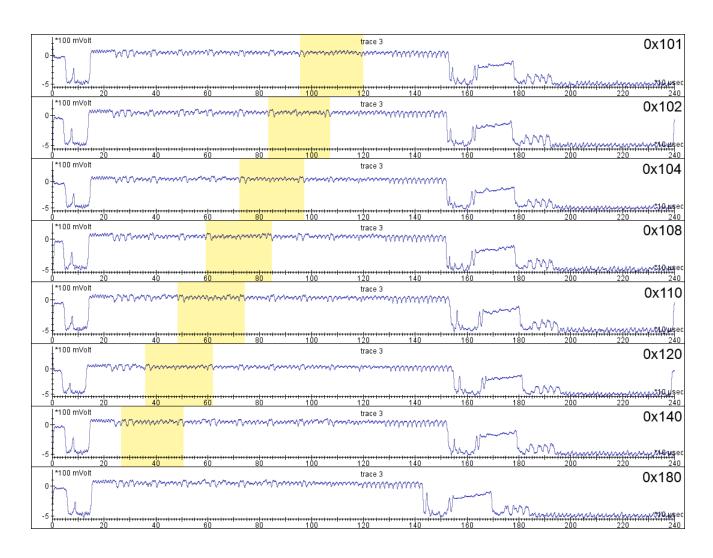

#### 2.6.3 Clock Jitter