# MASTER'S THESIS

## RADBOUD UNIVERSITY NIJMEGEN

## Asm3: modeling assembly languages efficiently in Why3

Author: Jonathan Moerman  $Supervisor: \\ Freek Wiedijk \\$

Second reader: Marc Schoolderman

#### Abstract

In this thesis, I present a domain-specific language for modeling straight-line assembly code, along with a plugin that extends Why3 with support for this language. This plugin contains its own VC generator that emits verification conditions that generally can be proven in less time and by more provers compared to what Why3 would generate for equivalent WhyML code. This VC generator differs among other things, in that, for each sub-goal, it automatically omits premises that do not appear useful. The language has an alternative to Why3's ref references, which, unlike those references, supports aliasing and offsets while not increasing the verification time.

This thesis starts with a short introduction to Why3 and a list of short comings of using Why3's WhyML language for modeling assembly code. I introduce the Asm3 language and the VC generator of the Asm3 plugin. I demonstrate how this plugin performs compared to plain Why3, using a short  $16\times16$  multiplication AVR assembly routine as an example. Finally, I show what the effects of the Asm3 plugin's VC generation optimizations are on the verification times and the number of goals each prover was able to verify, using a  $64\times64$  Karatsuba multiplication routine as a benchmark.

# Contents

| 1 | Intr | roduction                                                                | 4         |

|---|------|--------------------------------------------------------------------------|-----------|

| 2 | Wh   | v3                                                                       | 4         |

| - | 2.1  | WhyML                                                                    | 4         |

|   | 2.2  | Proving program properties                                               | 6         |

|   |      | 2.2.1 Defining bytes in WhyML                                            | 9         |

|   |      | 2.2.2 Building a simple verification condition for double                | 9         |

|   |      | 2.2.3 Mutable variables                                                  | 13        |

|   |      |                                                                          |           |

| 3 | Mo   | deling assembly code in Why3                                             | <b>15</b> |

|   | 3.1  | What makes verifying assembly code difficult?                            | 15        |

|   |      | 3.1.1 Aliasing                                                           | 15        |

|   |      | 3.1.2 Code length                                                        | 16        |

|   | 3.2  | Previous techniques used when verifying assembly code with Why $3$       | 17        |

|   |      | 3.2.1 Abstract blocks                                                    | 17        |

|   |      | 3.2.2 Ghost code                                                         | 17        |

|   |      | 3.2.3 Underspecification                                                 | 21        |

|   | 3.3  | Issues with modeling assembly code in Why3                               | 21        |

|   |      | 3.3.1 Type system issues                                                 | 21        |

|   |      | 3.3.2 Proof context pollution                                            | 21        |

|   |      | 3.3.3 Prover dependence                                                  | 22        |

| 4 | Δen  | a3 framework                                                             | 22        |

| - | 4.1  | The Asm3 language                                                        | 22        |

|   | 7.1  | 4.1.1 Index references                                                   | 23        |

|   |      | 4.1.2 Multi-byte integers                                                | 27        |

|   |      | 4.1.3 Alias annotations                                                  | 27        |

|   |      | 4.1.4 Expressive power of index references                               | 27        |

|   |      | 4.1.5 Weak types                                                         | 28        |

|   | 4.2  | VC generation in the Asm3 framework                                      | 30        |

|   |      | 4.2.1 Effect selection                                                   | 31        |

|   |      | 4.2.2 Predictable premise names                                          | 33        |

|   |      |                                                                          |           |

| 5 |      | nparison with WhyML: 16×16 multiplication                                | 34        |

|   | 5.1  | Comparing specification annotations                                      | 35        |

|   | 5.2  | Comparing VCs                                                            | 36        |

| 6 | Rea  | l world example: 64×64 Karatsuba multiplication                          | 40        |

| Ū |      | Effects of each configuration on verification of assertions and postcon- | 10        |

|   |      | ditions                                                                  | 41        |

|   |      | 6.1.1 Verification time                                                  | 41        |

|   | 6.2  | Effects of each configuration on verification of preconditions           | 45        |

|   | 6.3  | Summary                                                                  | 45        |

|   | 6.4  | Comparison with prior verification work on this assembly routine         | 45        |

|   |      | •                                                                        |           |

| 7 | Fut  | ure work                                                                 | <b>47</b> |

|   | 7.1  | Integration into Why3                                                    | 47        |

|   | 7.2  | Missing features                                                         | 48        |

|   |      | 7.2.1 Jumps                                                              | 48        |

|   | _ ^  | 7.2.2 Code extraction                                                    | 48        |

|   | 7.3  | Further improvements                                                     | 48        |

|   |      | 7.3.1 Improved memory separation                                         | 48        |

|   |      | 7.3.2 Improving effect selection                                         | 49        |

| 8 | Rela | ated work                                                                | 49        |

| 9            | Conclusion                                                                                            | 50        |

|--------------|-------------------------------------------------------------------------------------------------------|-----------|

| Re           | eferences                                                                                             | <b>50</b> |

| A            | Instruction definitions used in section 5                                                             | <b>51</b> |

| В            | Observations made during the process of verifying the $64{\times}64$ karatsuba multiplication routine | 53        |

| $\mathbf{C}$ | Asm3 code for the $64 \times 64$ Karatsuba multiplication routine                                     | <b>53</b> |

| D            | A possible approach for extending Asm3 with support for branching                                     | 64        |

## 1 Introduction

Software verification is an important process with which we can help make sure that mission-critical code doesn't crash or fail and make sure that cryptographical software doesn't leak secrets. Unfortunately, this is often a complex, tedious, and time-intensive process.

Verifying properties of highly optimized assembly code can be especially tricky as routines can be hundreds to thousands of instructions long, contain steps that are interleaved with other steps, and contain tricks that are non-trivial to reason about. The number of instructions is not only larger than the number of statements in high–level programming languages, each instruction may have a large number of effects. For example, an instruction may update a register but also update 5 flags. In many cases, only a few of these effects are relevant for the result of a piece of code. For example, the next instruction may already overwrite all status flags set by the previous instruction, without using any of these flags to generate its output.

Marc Schoolderman and I have previously used the Why3 platform to formally verify a high-speed implementation of the Curve25519 key agreement scheme for 8-bit AVR microcontrollers [13]. While modeling the AVR instruction set in Why3's WhyML language and translating the assembly code to WhyML using this model was generally straightforward, we hit several issues.

Among other things, the verification conditions (See page 10) Why3 discharged contained a lot of hypotheses that weren't useful for the current proof goal. Another issue was that due to Why3's strict aliasing requirements it wasn't feasible to model registers with separate variables. This made it more complicated to specify which registers were modified by a section of code and also negatively impacted the verification of the generated goals. When comparing these verification conditions with hand-made verification conditions that did not suffer from these issues, the verification times of Why3's verification conditions generally were higher and fewer provers were able to verify these verification conditions.

In this thesis, I will present a proof-of-concept plugin that allows for the generation of verification conditions that are generally both easier to read by users, and easier to prove for automated theorem provers. This plugin provides a way to automatically filter out hypotheses that are unlikely to positively contribute to the proof of the current goal. It also provides a means to model the value stored in objects such as registers separately while allowing aliasing and working with offsets of these objects.

## 2 Why3

Why3 [8] is a platform for deductive program verification. This platform features a language, WhyML, that is suitable for modeling the behavior of most programs while also allowing the user to formally specify the semantics of the code using annotations. Why3 automates the process of proving these properties as much as possible. Why3 generates proof obligations for the annotated programs and can encode these problems into the input of a wide range of automated theorem provers and interactive proof assistants. In many cases, SMT solvers such as Z3, CVC4, or Alt-Ergo or ATP systems such as E or Vampire can automatically verify that a property holds, while proof assistants (Isabelle/HOL, Coq, or PVS) can be used in cases where automated theorem provers fail.

#### 2.1 WhyML

Why3 provides an ML-like language called WhyML. WhyML can be divided into a logical specification language part [2] and an ML-like programming language part. Similarly, the world of Why3 can be divided into a logic and a program part. The logic part contains mathematical constructs such as predicates, lemmas, and mathematical functions while the program part contains variables and program functions. The

- function f(x: a) : b = X defines a logic function f of type b taking an argument of type a. The definition of f is X.

- let f(x: a): b S = X defines a program function f(x) = X of type f(x) = X is the specification given for f(x) = X is the body of this function.

- val f(x:a):b s axiomatically defines a program function f of type b taking an argument of type a. Axiomatic here means that no implementation of this f is given. The specification S is used as an axiom to describe the behavior of f.

- m[x] this returns element of the map m stored at key x. [] is the map-get operator.

- $m[x \leftarrow y]$  this returns a copy of m with the value stored at x replaced with y. [<-] is the map-set operator.

Table 1: Important WhyML syntax descriptions

programming part of WhyML isn't constrained to just specifying program functions: lemmas and mathematical functions can be constructed with it as well, as long as the code is purely functional<sup>1</sup>. This can be useful as, for example, this allows defining a mathematical function and a program function at the same time. Another advantage is that it is sometimes easy to provide an algorithm to prove a lemma. An example of some WhyML code is given in listing 1. Table 1 describes the WhyML syntax essential to understanding the listings contained in this thesis.

Listing 1: Example of some simple definitions in WhyML

```

module ExampleModule

(* Use module Int from standard library file int *)

use int.Int

use ref.Ref

(* functions can be defined in WhyML's logic language *)

function xor (x y: bool) : bool = (x \/ y) /\ not (x /\ y)

lemma double_xor_ident: forall x y. xor (xor x y) y = x

(* functions can be logic and program functions *)

(* fib is both a logic and a program function *)

let rec function fib (n: int) : int

requires \{ n \ge 0 \}

(* fib terminates because n always decreases

while remaining >= 0 *)

variant { n }

= if n = 0 then 0 else

if n = 1 then 1 else

fib (n-1) + fib (n-2)

(* iterative_fib is just a program function *)

let iterative_fib (n: int) : int

requires { n >= 0 }

ensures { result = fib n }

= if n = 0 then 0 else

let prev = ref 0 in

let current = ref 1 in

for i = 2 to n do

```

<sup>&</sup>lt;sup>1</sup>The code doesn't modify or depend on any global state.

```

invariant { !current = fib (i-1) }

invariant { !prev = fib (i-2) }

let new_prev = !current in

current := !current + !prev;

prev := new_prev

done;

!current

(* Lemmas can be defined using code.

This is equivalent to:

lemma fib_is_pos : forall \ n:int. \ n \ge 0 \rightarrow fib \ n \ge 0

But here we already provide the induction steps. *)

let rec lemma fib_is_pos (n: int)

requires \{ n >= 0 \}

ensures { fib n \ge 0 }

variant { n }

= if n > 1 then begin

fib_is_pos (n-2);

fib_is_pos (n-1)

end

```

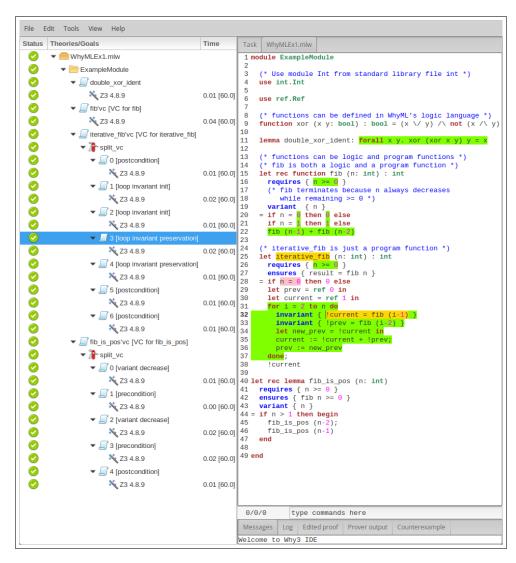

An example of how working with Why3's IDE looks like is shown in figures 1 and 2. These figures give a glimpse into the process of writing WhyML code proving specifications of this code in Why3's IDE.

#### 2.2 Proving program properties

The formal specification of WhyML programs is provided by specifying preconditions (for what initial state is the behavior defined) and postconditions (what are the effects of the program; what does it do). Preconditions are given by  $\mathbf{requires} \ \{ \cdots \}$  annotations while postconditions are given by  $\mathbf{ensures} \ \{ \cdots \}$  annotations. Why3 will create a proof obligation each time a program function with preconditions is called to check that these preconditions are met. It uses the postconditions of each called function to encode the resulting state after executing this function. For each program function, Why3 will generate a single logic formula, a verification condition, that holds if and only if, given all preconditions are satisfied, the program function executes correctly and terminates in a state where all postconditions hold.

Figure 1: Interface of the Why3 IDE: Working with the WhyML code from listing 1

The right pane shows the WhyML code in the IDE's editing tab, while the left pane shows the proof goals generated for this code. Currently a sub-goal of the proof goal generated for iterative\_fib is selected. The IDE highlights the source of the sub-goal with yellow, while sections of code that are used to generate this goal are highlighted with green.

Formulas of which the negation is used are highlighted red.

```

Time

Status Theories/Goals

▼ ■ WhyMLEx1.mlw

Ø

▼ ExampleModule

3 function xor (x:bool) (y:bool) : bool =

4   if (x = True \/ y = True) /\ not (x = True /\ y = True) then True

5   else False

000000000000

X Z3 4.8.9

0.01 [60.0]

,

/double_xor_ident : forall x:bool, y:bool. xor (xor x y) y = x

X Z3 4.8.9

0.04 [60.0] 8 9 function fib int : int

10

11 fib'def :

12 forall n1:int.

13 n1 >= 0 ->

▼ ___ iterative_fib'vc [VC for iterative_fib]

▼ 🎥 split_vc

forall name

n1 >= 0 ->

(if n1 = 0 then fib n1 = 0

else if n1 = 1 then fib n1 = 1

else fib n1 = (fib (n1 - 1) + fib (n1 - 2)))

0.01 [60.0] 15

16

17

X Z3 4.8.9

17

18 constant n : int

19

20 Requires : n >= 0

21

22 H3 : not n = 0

X Z3 4.8.9

0.02 [60.0]

2 [loop invariant init]

X Z3 4.8.9

0.01 [60.0]

23

24 H2 : 2 <= (n + 1)

25

00000000000000000000

X Z3 4.8.9

0.02 [60.0]

▼

☐ 4 [loop invariant preservation]

26 constant current1 : int

0.01 [60.0] 27

28 constant prev1 : int

X Z3 4.8.9

0.01 [60.0] 30 constant i : int

31 32 H1 : 2 <= i

X Z3 4.8.9

▼

☐ 6 [postcondition]

0.01 [60.0] 33 34 H : i <= n

X Z3 4.8.9

▼ ___ fib_is_pos'vc [VC for fib_is_pos]

36 LoopInvariant1 : current1 = fib (i - 1)

37

38 LoopInvariant : prev1 = fib (i - 2)

▼ 🎥 split vc

▼ ■ 0 [variant decrease]

X Z3 4.8.9

41

42 Ensures1 : current = (current1 + prev1)

43

44 constant prev : int

X Z3 4.8.9

▼ _ 2 [variant decrease]

0.02 [60.0] 45 46 Ensures : prev = current1 47

X Z3 4.8.9

▼

☐ 3 [precondition]

49

50 goal iterative_fib'vc : current = fib ((i + 1) - 1)

51

X Z3 4.8.9

0.02 [60.0]

0.01 [60.0] 52

X Z3 4.8.9

```

Figure 2: Interface of the Why3 IDE: Showing a sub-goal generated from the WhyML code in listing  ${\color{red}1}$

#### 2.2.1 Defining bytes in WhyML

To look at how we can prove the specification of a program function we will generate a verification condition for a simple function operating on bytes. If we want to model code working with bytes in WhyML, we would first need to model what a byte is. Listing 2 provides an example of a type byte along with a corresponding definition of addition. The infix function + (let (+) ··· in listing 2) defines addition in terms of integer addition (addition in  $\mathbb{Z}$ ). This program function has ensures { byte'int result = byte'int b1 + byte'int b2 } as postcondition, which states that the integer projection of the output<sup>2</sup> is equal to the sum of the integer projections of its input. This can only hold if the sum of the inputs would fit in a byte. This requirement is encoded in the precondition requires { in\_bounds (byte'int b1 + byte'int b2) }.

Listing 2: Modeling bytes in Why3's WhyML language

```

type byte = < range 0 255 >

Currently very little is defined for type byte.

We just have the projection function byte'int which gives the

projection of a byte in \mathbb{Z} (Why3 type int).

We can use this to define operations on bytes.

predicate in_bounds (n: int) = 0 <= n <= 255</pre>

byte'int is only a logic function and not a program function,

so we cannot call it from a program function.

We can use it in the specification of a program function,

though.

*)

val to_int (n: byte) : int

ensures { result = byte'int n }

val of_int (n: int) : byte

requires is_in_bounds { in_bounds n }

ensures { byte'int result = n }

(* Defining addition for bytes *)

let (+) (b1 b2: byte) : byte

requires { in_bounds (byte'int b1 + byte'int b2) }

ensures { byte'int result = byte'int b1 + byte'int b2 }

= return of_int (to_int b1 + to_int b2)

```

We can let Why3 automatically insert byte'int when it encounters a byte where it expects an int. This can be accomplished by adding the following line below the definition of byte:

```

meta coercion function byte'int

```

As leaving out all applications of byte'int makes the specifications significantly easier to read we will no longer explicitly use it past this point.

#### 2.2.2 Building a simple verification condition for double

Now we have this basic definition we can write some simple program functions operating on bytes and verify that their specification holds. Listing 3 contains a program

<sup>&</sup>lt;sup>2</sup>The keyword **result** denotes the output of a program function.

function double which returns a value that is twice as large as its input.

Listing 3: WhyML program function double

```

let double (b: byte): byte

requires result_fits { in_bounds (2 * b) }

ensures { result = 2 * b }

= b + b

```

We will now show how the specification of a program function such as double is proven in Why3. To verify that the specifications of programs are correct, Why3 generates Verification Conditions (VCs). VCs are logical formulas that are generated to help prove that the specifications of code are correct. A VC implies that given that the preconditions of a piece of code hold, the specification of its body is consistent and after execution the postconditions hold.

Why3 generates VCs using a standard weakest-precondition procedure [8]. The weakest precondition [6] of a statement S with respect to a formula Q, is a formula encoding the most general initial state such that, when executing S

- Execution does not go wrong. (i.e. assertions do not fail and the preconditions of program functions called in S are met.)

- $\bullet$  Upon termination Q holds.

This weakest precondition of a statement S with respect to a formula Q is given by wp(S, Q). For straight-line WhyML code we can approximate the weakest precondition of a statement with the following two rules:

- $wp(S, Q) \approx pre_S \land (post_S \rightarrow Q)$ : the preconditions  $pre_S$  of statement S hold and the postconditions  $post_S$  imply that Q holds.

- $wp(S_1; S_2, Q) = wp(S_1, wp(S_2, Q))$  gives the weakest precondition of the sequence  $S_1; S_2$ .

These rules only approximate the weakest precondition as they do not state how program variables are modeled. Section 2.2.3 provides some information on this topic.

We can apply these rules to generate a verification condition for double. For this program function we need to prove that the postcondition result = 2\* b holds given in\_bounds (2\* b). We haven't defined how program variables such as b and result are used to build the weakest precondition. For now, we will replace these variables [b] and [result]] which should be interpreted as representing the semantics of b and result respectively. As the body of double consists of the single statement b + b we need to generate  $in\_bounds(2 \times [b]) \rightarrow wp(b + b, [result] = 2 \times [b])$ . The statement b + b has in\_bounds (b + b) as precondition and result = b + b as postcondition, meaning that we can approximate the weakest precondition of double with  $in\_bounds(2 \times [b]) \rightarrow in\_bounds([b] + [b]) \wedge ([result] = [b] + [b]) \rightarrow [result] = 2 \times [b])$

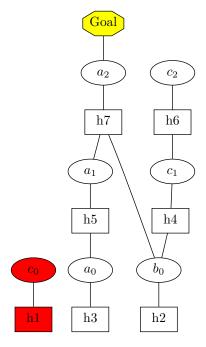

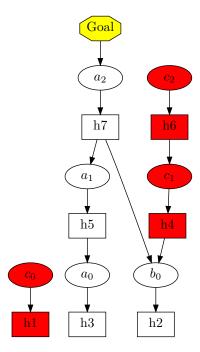

Figure 3 shows the proof obligation Why3 generates for double. Observe that this closely matches the formula we generated previously. While almost any automatic theorem prover will be able to verify the goal formula of this VC, often it is necessary to verify a sub-goal (such as an assertion) individually. After introducing the bound variables and splitting the formula at the conjunction we are left with the more readable sub-goals shown in figures 4 and 5.

```

1 ------ Local Context ------

3 type byte = <range 0 255>

5 function byte'int byte : int

7 constant byte'maxInt : int = 255

9 constant byte'minInt : int = 0

10

11 predicate in_bounds (n:int) = 0 \le n / n \le 255

13 ----- Goal -----

14

15 goal double'vc :

16

forall b:byte.

in_bounds (2 * b) ->

17

in_bounds (b + b) /

18

(forall result:byte. result = (b + b) \rightarrow result = (2 * b))

19

```

Figure 3: Verification condition containing all proof obligations generated for double. This image is a crop of a screenshot of the Why3 IDE window.

Figure 4: First sub-goal of the VC of double: the precondition of b + b

```

1 ----- Local Context -----

3 type byte = <range 0 255>

5 function byte'int byte : int

7 constant byte'maxInt : int = 255

9 constant byte'minInt : int = 0

10

11 predicate in_bounds (n:int) = 0 \le n / n \le 255

13 constant b : byte

15 result_fits : in_bounds (2 * b)

16

17 constant result : byte

18

19 Ensures : result = (b + b)

20

----- Goal -----

22

23 goal double'vc : result = (2 * b)

```

Figure 5: Second sub-goal of the VC of double: the postcondition of double

#### 2.2.3 Mutable variables

So far, we have only shown code without mutable variables. WhyML is also suitable for modeling imperative code. We can, for example, easily model mutable variables by using Why3's ref references. Why3 includes the writes annotation to specify which mutable variables will be modified and the reads annotation to specify whether the values initially stored in mutable variables are used by the code. In Why3 version 1.3, these annotations are often optional: Why3 will derive this information itself. quadruple\_by\_ref in listing 4 gives an example of a program function working with mutable variables. It updates the value where b points to. Here := denotes assignment and the ! operator returns the value to which a reference points.

While the programming part of Why3 supports mutable variables, the logic part does not. Why3 solves this issue by modeling mutable variables by creating a new incarnation of a variable each time a program this variable is updated. For example the sequence  $\mathbf{x} := \mathbf{0}$ ;  $\mathbf{x} := \mathbf{1}$ ;  $\mathbf{x} := \mathbf{2}$ ; assert  $\{!\mathbf{x} > \mathbf{1}\}$  can be encoded as  $\forall_{x_1,x_2,x_3\in\mathbb{Z}} x_1 = 0 \land x_2 = 1 \land x_3 = 2 \to x_3 > 1$  where  $x_1$  represents the value stored in  $\mathbf{x}$  after executing  $\mathbf{x} := \mathbf{0}$ ,  $x_2$  represents the value after executing  $\mathbf{x} := \mathbf{1}$ , and  $x_3$  represents the value after executing  $\mathbf{x} := \mathbf{2}$ .

Listing 4: WhyML program function that quadruples a value passed by reference

```

let quadruple_by_ref (b: ref byte) : unit

requires result_fits { in_bounds (4 * !b) }

ensures { !b = 4 * old !b }

reads { b }

writes { b }

b := !b + !b;

b := !b + !b

```

The user can refer to previous values stored in a mutable variable or field by using the at and old keywords. The keyword old allows us to refer to the state prior to execution, while the keyword at can be used to refer to the state at a specific point during execution. When using at, a label is used to specify the specific state during execution. This label doesn't affect the execution of the code, but simply allows us to assign a name to a specific moment during execution. Listing 5 provides a simple demonstration of how at can be used to refer to a previous state.

Listing 5: WhyML fragment showing how the keyword at can be used.

```

...

x := 0;

label L in y = ...;

...

x := !x + !y;

assert { !x = !y by ((!x = 0) at L) }

(* This is equivalent to (!x = 0) at L /\ (!x = 0) at L -> !x = !y *)

```

Using the information from above, we can improve our previous approximation of the weakest precondition of straight-line WhyML code:

•  $wp(S, Q) = pre_S \wedge (\forall_{i_0} \cdots \forall_{i_n} post_S \rightarrow Q')$  where  $i_0$  through  $i_n$  are new incarnations of the program variables  $v_0$  through  $v_n$  modified by S. Q' is Q with  $v_0$  through  $v_n$  replaced with these new incarnations, **unless** this variable appears under either at or old. For example: wp([a:=!a+1]],  $[!a]_{ub} > [old !a]_{ub}$  (where  $[!a]_{ub}$  is an unbound variable modeling !a): results in  $\forall a_{new} \ a_{new} = [a]_{ub}$

$[\![!a]\!]_{ub} + 1 \rightarrow a_{new} > [\![old !a]\!]_{ub}$  given  $post_S$  is defined as  $a_{new} = [\![!a]\!]_{ub} + 1$  and  $pre_S$  is defined as true.

- wp(label L in S, Q) = remove\_label(L, wp(S, Q)). Where remove\_label removes the given label from its second argument.

If wp(S, Q) = Q' and remove\_label(L, Q') = Q" then Q" is Q' with every sub-formula "X at L" is replaced with "X" in Q'. Unbound program variables appearing in X are now available to be replaced by incarnations generated by subsequent applications of the first rule.

- $wp(S_1; S_2, Q) = wp(S_1, wp(S_2, Q))$ , this rule remains unchanged.

We can now apply these rules to generate the weakest precondition for quadruple\_by\_ref (here  $[\![!b]\!]_{ub}$  is an unbound variable modeling  $[\![!b]\!]_{ub}$ :

```

\begin{split} wp(\mathbf{b}:=!\mathbf{b}+!\mathbf{b};\mathbf{b}:=!\mathbf{b}+!\mathbf{b}, & [\![!\mathbf{b}]\!]_{\mathbf{ub}} = 4 \times [\![\mathsf{old}\ !\mathbf{b}]\!]_{\mathbf{ub}}) &= \\ wp(\mathbf{b}:=!\mathbf{b}+!\mathbf{b}, & wp(\mathbf{b}:=!\mathbf{b}+!\mathbf{b}, & [\![!\mathbf{b}]\!]_{\mathbf{ub}} = 4 \times [\![\mathsf{old}\ !\mathbf{b}]\!]_{\mathbf{ub}})) &= \\ & wp(\mathbf{b}:=!\mathbf{b}+!\mathbf{b}, & \textit{in\_bounds}([\![!\mathbf{b}]\!]_{\mathbf{ub}} + [\![!\mathbf{b}]\!]_{\mathbf{ub}}) \wedge \\ & (\forall_{b_0} \ b_0 = [\![!\mathbf{b}]\!]_{\mathbf{ub}} + [\![!\mathbf{b}]\!]_{\mathbf{ub}} \to b_0 = 4 \times [\![\mathsf{old}\ !\mathbf{b}]\!]_{\mathbf{ub}})) &= \\ & \textit{in\_bounds}([\![!\mathbf{b}]\!]_{\mathbf{ub}} + [\![!\mathbf{b}]\!]_{\mathbf{ub}}) \wedge (\forall_{b_1} \ b_1 = [\![!\mathbf{b}]\!]_{\mathbf{ub}} + [\![!\mathbf{b}]\!]_{\mathbf{ub}} \to \\ & \textit{in\_bounds}(b_1 + b_1) \wedge (\forall_{b_0} \ b_0 = b_1 + b_1 \to b_0 = 4 \times [\![\mathsf{old}\ !\mathbf{b}]\!]_{\mathbf{ub}})) \end{split}

```

We now need to bind the remaining unbound program variables and add the precondition:

```

\forall_{b_2} \textit{in\_bounds}(4 \times b_2) \rightarrow \textit{in\_bounds}(b_2 + b_2) \land \\ (\forall_{b_1} \ b_1 = b_2 + b_2 \rightarrow \textit{in\_bounds}(b_1 + b_1) \land (\forall_{b_0} \ b_0 = b_1 + b_1 \rightarrow b_0 = 4 \times b_2))

```

When we look at the VC generated by Why3 itself, shown in figure 6, we can see that this VC is equivalent to the formula we just generated.

```

----- Local Context -----

3 type byte = <range 0 255>

5 function byte'int byte : int

7 constant byte'maxInt : int = 255

8

9 constant byte'minInt : int = 0

11 predicate in_bounds (n:int) = 0 \le n / n \le 255

----- Goal -----

13

14

15 goal quadruple_by_ref'vc :

16

forall b:byte.

in_bounds (4 * b) -> in_bounds (b + b) /\

17

18

(forall o:byte.

19

20

o = (b + b) ->

21

(forall b1:byte.

b1 = o ->

22

23

in_bounds (b1 + b1) /

24

(forall o1:byte.

o1 = (b1 + b1) \rightarrow (forall b2:byte. b2 = o1 \rightarrow b2 = (4 * b)))))

25

26

```

Figure 6: The VC generated for quadruple\_by\_ref by Why3

## 3 Modeling assembly code in Why3

This chapter describes some of the factors that make analyzing and verifying assembly code difficult. Section 3.2 describes techniques that have previously been used to combat these issues. Section 3.3 describes difficulties that remain even when these techniques are used.

#### 3.1 What makes verifying assembly code difficult?

Assembly code has some properties that make it more difficult to analyze and verify than most code written in high level languages. In this thesis I will focus on two aspects that complicate the verification of assembly code: the prevalent occurrence of aliasing and the length of assembly routines.

#### 3.1.1 Aliasing

One issue when verifying assembly code is that aliasing occurs often. To see why this would be an issue consider the program function add in listing 6. Why3 requires that aliasing of mutable arguments must be statically known and will thus not allow rd and rr to alias. One could annotate add with alias {rd with rr}, but in that case, rd and rr must alias.

Listing 6: WhyML program function which adds the value stored in two 8 bit registers and stores the lowest 8 bits of the result in the first register and the carry bit in flag cf.

```

type reg = ref byte (* registers *)

val cf: ref bool (* carry flag *)

let add (rd rr: reg) : unit

ensures {

let result = old (!rd + !rr) in

!rd = mod result 256 /\

!cf = not div result 256 = 0

}

writes { rd, cf }

= let result = to_int !rd + to_int !rr in

rd := of_int (mod result 256);

cf := not div result 256 = 0

```

It is, of course, possible to model functions in which arguments may alias. We could, for example, model such arguments as indices into a single mutable map<sup>3</sup>. add could then be modeled as shown in listing 7.

Aside from solving the aliasing issue this also allows us to work with offsets, which is desirable when working with registers and essential when modeling main memory. Otherwise, we would need to pass a reference for every byte that is read from or written to, which would not only be cumbersome but in many cases impossible<sup>4</sup>.

Modeling mutable objects such as registers using indices into a single mutable object has its disadvantages. All aliasing is allowed by default, meaning that the user must write preconditions to explicitly exclude all undesired aliasing cases. As long as the indices used are constants, the verification conditions Why3 generates are generally simple enough that most provers perform well. However, providing indices as arguments to the program function complicates these verification conditions to such a degree that provers perform much worse. In practice, this means that it takes more effort to verify functions that generalize a recurring step in an assembly routine for which the registers used vary. Another disadvantage is that tracking which values were

<sup>&</sup>lt;sup>3</sup>In Why3's standard library the type map is defined as type map 'a 'b = 'a -> 'b

<sup>&</sup>lt;sup>4</sup>Example: a function that copies n bytes of memory, where n is passed as an argument.

Listing 7: Alternative implementation of add

```

val regs : ref (map int byte) (* registers *)

val cf: ref bool (* carry flag *)

val reg_set (r : int) (b : byte) : unit

ensures { !regs = !(old regs)[r <- b] }</pre>

writes { regs }

let add (rd rr: int) : unit

ensures {

let result = !(old regs)[rd] + !(old regs)[rr] in

(*implicit byte'int*) !regs[rd] = mod result 256 /\

!cf = not div result 256 = 0

}

ensures {

!regs = !(old regs)[rd <- !regs[rd]]

writes { regs, cf }

= let result = to_int !regs[rd] + to_int !regs[rr] in

reg_set rd (of_int (mod result 256));

cf := not div result 256 = 0

```

modified becomes more expensive, both in the time needed to write specifications and verification times of these specifications. Why3 can automatically track what memory has been modified and what remained unchanged if simple ref objects are used to model memory. This is not the case when modeling a memory address space in a single object. In that case, the user will need to manually specify all writes in the ensures part of the specification. These postconditions result in extra premises for any subsequent goals, which has a cost.

#### 3.1.2 Code length

Highly optimized assembly code often consists of a large number of instructions. Branching is often kept to a minimum as jumping is costly<sup>5</sup> and having separate branches may leak information on the internal state (for example: through difference in timing or energy usage). The latter issue is of great concern if the code is handling sensitive data. Steps may also be interleaved to best make use of resources such as the available registers. For example, in one step some values may be produced which are needed for a subsequent step. It may be the case that, not enough registers are available to efficiently complete the current step while keeping these values untouched. Here, it could be better to execute a part of this next step and write the results to main memory. If these steps are performed sequentially then these values would have to be temporarily stored in main memory and retrieved in the subsequent step. Meanwhile, the results may still need to be stored in main memory. In this case, executing the steps sequentially would result in an extra store and load instructions having to be executed.

The minimal amount of branching combined with interleaved steps, and possibly other optimizations to best utilize the still available resources, can result in large intricate pieces of code that cannot neatly be divided into separate parts. This division would enable, or at least simplify, the separate analysis of the steps present in an assembly routine. It would allow for straightforward proof reuse if a continuous section of code reoccurs multiple times.

While instructions perform simple operations they can have a large number of

<sup>&</sup>lt;sup>5</sup>Jumping itself adds a bit of overhead, but the main issue is that, if the branch predictor doesn't predict the right branch, the instruction pipeline has to be flushed.

effects<sup>6</sup>, though this is highly dependent on the instruction set architecture (ISA). Take addition, in a language such as C the statement a = a + b will simply add the values of a and b together and store the result in a. In AVR assembly, the instruction ADD R2, R3 not only adds the values stored in registers R2 and R3 together and stores the result in R2, but it will also update a number of flags. Specifically, it will update

- the carry flag (did the addition cause an overflow?)

- the zero flag (is the new value stored in R2 all zeroes?)

- the negative flag (is the sign bit of R2 now 1?)

- the two's complement overflow indicator (does the most significant bit of the result differ from the inputs?)

- the sign flag

- the half carry flag (did the addition of the lowest 4 bits result in a carry?)

While some of these effects may influence the end result of the code it is unlikely that all of these effects have an impact.

The large number of instructions combined with potentially a large number of effects per instruction results in a large number of premises in the generated VCs. This can be an issue as provers tend to perform worse as the number of premises increases.

# 3.2 Previous techniques used when verifying assembly code with Why3

#### 3.2.1 Abstract blocks

One intuitive step to deal with the amount of premises is to break the code up into smaller chunks. In WhyML it is possible to divide code into abstract blocks. Abstract blocks hide their contents from any subsequent code. Only the specification given by the user and the information on what memory is modified are exported. These abstract blocks allow us to summarize the relevant effects while discarding all irrelevant information. If necessary, abstract blocks can be nested. The advantage of using abstract blocks instead of dividing the code into multiple program functions is that the information from earlier parts of the code is still available (such as the preconditions at the start of the assembly routine and the effects of previous instructions and abstract blocks). If code is divided into multiple program functions this information would likely need to be explicitly restated as preconditions which would result in a larger number of annotations overall.

#### 3.2.2 Ghost code

While dividing the code into blocks helps it is still desirable to keep these blocks as large as possible without having to provide additional annotations such as assertions. Here Why3's concept of *ghost code* [7] is quite useful. Ghost code is code for which Why3 guarantees that it cannot affect the outcome of normal code. This allows us to insert or extend code without the risk of affecting the behavior modeled by the code.

One of the things that ghost code enables is that we can pass values as ghost parameters. An example of a case where this is very helpful is in cases where a consecutive area of main memory is modified. This is often done by storing a pointer to the start of this area in one or multiple registers (depending on whether the pointer fits in a single register), followed by repeated writing to the memory the pointer refers

<sup>&</sup>lt;sup>6</sup>Here an effect means a modification of the system state. Some examples of effects are: setting the carry flag, loading a constant into a register or storing the contents of a register in main memory (RAM memory).

to and incrementing the pointer. Normally this might result in a list of postconditions like shown in listing 9.

Listing 8: A sequence of 16 ST Z+, r1 "Store Indirect From Register to Data Space using Index Z" instructions modeled in WhyML.

```

label START in

st_inc r30 r1;

label L1 in

st_inc r30 r1;

label L2 in

st_inc r30 r1;

label L3 in

st_inc r30 r1;

...

label L15 in

st_inc r30 r1;

label L15 in

```

Listing 9: Example of what formulas would result from the code from listing 8. The at keyword is used here to refer to the state of the main memory and registers at previous points of execution. Why3 itself will not generate formulas containing the at keyword. Here it is used to relate the incarnations of mem to the original code.

```

(* pointer is stored in registers r30 and r31 *)

(* START and L1 through L16 are code labels (positions in the code) *)

mem at L1 = (mem[(reg[r30] + 256 * reg[r31]) <- reg[r1]]) at START

(reg[r30] + 256 * reg[r31]) at L1 = (1 + reg[r30] + 256 * reg[r31]) at START

mem at L2 = (mem[(reg[r30] + 256 * reg[r31]) <- reg[r1]]) at L1

(reg[r30] + 256 * reg[r31]) at L2 = (1 + reg[r30] + 256 * reg[r31]) at L1

mem at L3 = (mem[(reg[r30] + 256 * reg[r31]) <- reg[r1]]) at L2

(reg[r30] + 256 * reg[r31]) at L3 = (1 + reg[r30] + 256 * reg[r31]) at L2

...

mem at L16 = (mem[(reg[r30] + 256 * reg[r31]) <- reg[r1]]) at L15

(reg[r30] + 256 * reg[r31]) at L16 = (1 + reg[r30] + 256 * reg[r31]) at L15</pre>

```

If we store the initial pointer value in a ghost variable we can use this variable to define the postconditions in terms of the initial pointer value. The postconditions now could look like what is shown in listing 11.

Listing 10: A sequence of 16 ST Z+, r1 instructions modeled in WhyML. Here the pointer stored in Z (registers r30 and r31 combined) is passed as a ghost argument to st\_inc'.

```

label START in

let ghost ptr = uint 2 reg r30 in

st_inc' r30 r1 ptr;

label L1 in

st_inc' r30 r1 (ptr + 1);

label L2 in

st_inc' r30 r1 (ptr + 2);

label L3 in

st_inc' r30 r1 (ptr + 3);

...

label L15 in

st_inc' r30 r1 (ptr + 16);

label L16

```

Listing 11: Example of what formulas would result from the code from listing 10. These formulas are easier to work with than the formulas from listing 9 as the pointer values are expressed directly in terms of the original value. Previously we would need to work back through all previous versions of reg to see how this value has changed.

```

(* The initial pointer value is stored in ghost variable ptr *)

ptr = reg[r30] + 256 * reg[r31] at START

mem at L1 = (mem[ptr <- reg[r1]]) at START

(reg[r30] + 256 * reg[r31]) at L1 = ptr + 1

mem at L2 = (mem[ptr+1 <- reg[r1]]) at L1

(reg[r30] + 256 * reg[r31]) at L2 = ptr + 2

mem at L3 = (mem[ptr+2 <- reg[r1]]) at L2

(reg[r30] + 256 * reg[r31]) at L3 = ptr + 3

...

mem at L16 = (mem[ptr+15 <- reg[r1]]) at L15

(reg[r30] + 256 * reg[r31]) at L16 = ptr + 16</pre>

```

Another area where ghost code is quite useful is in using mutable ghost variables to help express what registers were modified. While we can not directly use separate variables to model the registers we can still use them to help express what register got updated in a block of code. By specifying that these ghost variables are synchronized with the modeled registers both before and after execution of a block of code while only updating the ghost variables corresponding to registers that were updated in this block, we can provide the provers with enough information on what registers have changed. An example of this technique in use can be seen in listing 12. While this notation isn't more compact than specifying the same information without ghost registers (see listing 13) this technique seems to generally scale better.

Listing 12: Example of specifying register modifications with shadow registers

```

use avrmodel.Shadow as S

let mul16 (): unit

(* The ghost registers in S.shadow are synchronized with reg.

* The registers are modeled in reg, which is a mutable map

* from integers to bytes. *)

requires { S.synchronized S.shadow reg }

(* uint is a function that returns the value stored in multiple

* consecutive bytes interpreted as an unsigned integer *)

ensures { uint 4 reg 12 = old(uint 2 reg 2 * uint 2 reg 7) }

(* After execution the ghost registers are again synchronized with reg *)

ensures { S.synchronized S.shadow reg }

(* Implicit: writes \{reg, S.r0, S.r1, S.r12, etc.\} *)

clr r23;

mul r3 r8;

movw r14 r0;

mul r2 r7;

movw r12 r0;

mul r2 r8;

add r13 r0;

adc r14 r1;

adc r15 r23;

mul r3 r7;

add r13 r0;

adc r14 r1;

adc r15 r23;

(* Update the shadow registers for which the register in reg was updated *)

S.modify_r0();

S.modify_r1();

S.modify_r12();

S.modify_r13();

S.modify_r14();

S.modify_r15();

S.modify_r23()

```

Listing 13: An alternative way of specifying which registers where modified in mul16.

```

ensures {

reg = (old reg)[r0 <- reg[r0]][r1 <- reg[r1]]

[r12 <- reg[r12]][r13 <- reg[r13]][r14 <- reg[r14]][r15 <- reg[r15]]

[r23 <- reg[r23]]

}</pre>

```

The assembly code modeled in listing 12 can be seen in listing 14. Observe that the WhyML code looks very much alike.

Listing 14: 16×16 bits multiplication implementation in AVR assembly

```

mul16: CLR R23

MUL R3, R8

MOVW R14, R0

MUL R2, R7

MOVW R12, R0

MUL R2, R8

ADD R13, R0

ADC R14, R1

ADC R15, R23

MUL R3, R7

ADD R13, R0

ADC R14, R1

ADC R15, R23

```

#### 3.2.3 Underspecification

Another measure that helps to keep the amount of premises in check is to only model those parts of the architecture that are relevant for the modeled code. Parts of the architecture that aren't relevant for the instructions of the modeled code can be safely omitted. For example, when working with AVR code without branching it is safe to omit the zero flag as this part of the state is only used by branch (jump) instructions. Any effects that describe modifications on the modeled state can also be safely omitted, as long as the **writes** specification is complete (for any part X of the architecture model state it is fine to omit information on how an instruction modifies X, but not that it modifies X.). This is equivalent to removing premises in a logic formula: the new formula will only hold if the original formula did.

#### 3.3 Issues with modeling assembly code in Why3

While an implementation of Curve25519 in AVR assembly modeled in WhyML [12, 13] has previously been verified, some difficulties were noticed during this effort.

#### 3.3.1 Type system issues

One of the most noticeable issues is that we previously weren't able to port our work from Why3 0.88 to Why3 1.2 within a reasonable time frame. Why3 1.0 changed how type invariants (constraints placed on the values instances of a type can take) are modeled in its SMT output, which had a dramatic effect on the performance of the provers. Proofs that previously finished within a fraction of a second now no longer succeeded within a minute or ran out of the set 2GB memory limit. While emulating the old behavior by manually modeling type invariants using pre- and postconditions did work, this resulted in at least one additional precondition for each instruction. This greatly increased clutter and would slow (re-)loading files with hundreds of instructions down to such a degree of being unusable. Using range types showed some promise, but it seemed that we still would not be able to match the performance of 0.88 in the number of instructions per annotation. Due to time constraints, we decided to stick with Why3 version 0.88 for [13].

#### 3.3.2 Proof context pollution

The proof context contains all information available to prove the generated proof obligations. The proof context contains all previously defined lemmas and axioms, constants and types as well as the current premises. Examples of the (local) proof

context can be seen in figures 2 through 6: the proof context is the part between Local Context and Goal. Every annotation or instruction not inside the body of a previous abstract block adds information to the proof context. While this information often is essential, we only need information on the current state and how this relates to the initial state, not all information may be necessary to prove local properties. In section 3.2 some techniques were described to limit the number of premises present in the proof context, but these techniques are not always sufficient. Much of the information is relevant for some of the proof obligations, but not necessarily for the current goal. The proof context may contain so much noise that provers are no longer able to verify the current goal. If the proof context cannot be reduced any further without removing any information necessary to prove later goals it may be useful to model a block of code in a separate program function.

It may be useful to pass some of the registers used as arguments if a step is repeated but some of the registers the step operates on differ. Unfortunately, this comes with disadvantages: where provers generally perform well with registers modeled as static indices, with known values, into a mutable map, they perform far worse if the value of the index isn't known. Additionally, the user needs to manually exclude any register passed as an argument from aliasing with (nearly) any other register in use by the code

Another disadvantage of dividing code into program functions is that code may be harder to relate to the original assembly code. Why3 doesn't provide a way to recursively replace calls to program functions with the contents of these functions until only calls to the functions modeling instructions are left. This means that checking that a verified program function indeed models a given assembly routine takes an increasing amount of effort the more this routine has been divided into program functions.

#### 3.3.3 Prover dependence

Another issue we hit was that for some goals only a single version of a single prover would be able to prove this goal. Specifically: CVC4 1.4 was often the only prover able to verify that blocks of code performed the specified multiplications. Newer versions of the same prover often wouldn't be able to prove these same goals or would take much longer to do so. While I'm not aware of any soundness issues of CVC4 version 1.4, depending on a single outdated version is something that is best to be avoided.

#### 4 Asm3 framework

To combat the issues listed in section 3.3 the Asm3 framework was created. This framework consists of a plugin for Why3 and it provides a language specializing in modeling assembly code based on Why3's WhyML. The language contains a special feature for modeling statically accessed memory while additionally providing syntax for working with multi-byte integers. The framework provides its own VC generator which features heuristics to automatically filter out most premises that are unlikely to contribute to proving the current proof goal. This filtering step can be configured or disabled per sub-goal.

### 4.1 The Asm3 language

The Asm3 language is designed to be an annotated variant of traditional assembly source code. The language is similar to WhyML but doesn't have program functions, instead, it has instructions, macros, and entry points.

Instructions are the most basic programming elements in Asm3 and can be used to model assembly instructions. Currently, it is only possible to define instructions axiomatically<sup>7</sup> as it currently is the smallest building block available.

<sup>&</sup>lt;sup>7</sup>In the future it would be desirable to have the user give a proof of the consistency of the

Macros can be used to model reusable sequences of instructions. The body of a macro consists of a sequence of instructions or invocations of other macros. The arguments for instructions or macro invocations appearing in this body do not have to be constants, but can also be expressed in terms of the arguments of the macro. Like WhyML's program functions macros abstract their implementation details from their users.

Listing 15: Asm3 macro modeling the assembly code from listing 14

```

let macro mul16

ensures { $r12...4 = old ($r2...2 * $r7...2) }

reads { r2, r3, r7, r8 } (* Reads specification is optional here *)

writes { r0, r1, r12, r13, r14, r15, r23 }

writes { cf, hf, sf, vf, nf, zf }

clr r23;

mul r3 r8;

movw r14 r0;

mul r2 r7;

movw r12 r0;

mul r2 r8;

add r13 r0;

adc r14 r1;

adc r15 r23;

mul r3 r7;

add r13 r0;

adc r14 r1:

adc r15 r23

```

Entry points are quite similar to macros in that both model the behavior of sequences of instructions, but unlike macros, entry points cannot be included in another entry point or macro. Where macros model reusable sections of code, entry points are used to model entire assembly programs or routines. Once implemented it would be possible to extract a sequence of instructions and labels by recursively expanding any macros appearing in the body of an entry point. As code extraction currently isn't implemented using entry points does not provide an advantage over using only macros.

#### 4.1.1 Index references

Asm3 contains a concept of *index references* that can be thought of as a hybrid approach between working with Why3's **ref** references and indices into mutable maps. In Asm3 it is possible to use these index references to model memory such as registers using (seemingly) separate references while allowing aliasing and working with offsets. To properly explain what an index reference is and what we can do with it we first need to introduce the related concepts of index types and indexed objects.

To define an index reference we first need to define an *index type*. For example, we can define an index type *i-type* with

```

index i-type = create_index i-obj (a, b)

```

Here index and create\_index are keywords, while a and b are types. i-obj is the name of the memory space indexed by references of index type i-type. We will refer to these memory spaces indexed by index references as indexed objects.

For simplicity, i-obj can be thought of as a mutable variable of type map a b while references of index type i-type can be thought of as constants of type a. i-obj never appears in any code or specifications, but may appear in the VCs generated by the Asm3 plugin. It is accessed only through references of index type i-type.

specification of an instruction. Users should be able to prove that an implementation of an instruction could exist.

Now we have defined an index type we can define an index reference. We can define such a reference in a similar way to defining a variable, only we don't specify a type, but an index type. For example, we can define an index reference x of index type i-type with x: i-type. When x is used by itself it is coerced to a value of type a. An index reference is generally only useful when used in combination with the \$ operator: the index dereference operator. This operator returns the value stored at the position of an index reference in its corresponding indexed object. For example, we can think of x as returning i-obj[x].

Listing 16 provides an example in which two index types get defined. The index type reg is used to model 32 8-bit wide registers, while the index type srbit is used to model 8 bits of the status register SREG. Listing 16 also shows how we can define

Listing 16: A simple example of using index references in the Asm3 language

```

(* Definition of 32 8 bits registers *)

type reg_index : <range 0 31>

(* Definition of index type reg with its indexed object regs *)

index reg = create_index regs (reg_index, byte)

(* variables (x: req) implicitly index the indexed object reqs *)

(* regs is an internal mutable object containing bytes *)

(* Definition of status register SREG, which contains the status flags *)

type rb_index = <range 0 7> (* SREG is 8 bits wide *)

index srbit = create_index sreg (rb_index, bit)

(* Carry flag *)

let constant cf: srbit = 0 (* cf is the value stored in sreq at position 0 *)

(* This instruction models a simplified version of the AVR ADD instruction *)

(* $ dereferences index references *)

val instr add (rd rr: reg)

ensures Post_rd { $rd = mod (old ($rd + $rr)) 256 }

ensures Post_cf { $cf = div (old ($rd + $rr)) 256 }

reads { rd, rr }

writes { rd, cf }

may_alias { rd with rr }

let macro avr_double (dst: reg)

requires { $dst < 128 }</pre>

ensures { $dst = 2 * old $dst }

writes {dst, cf}

add dst dst

```

an index reference. The declaration let constant cf: srbit = 0 defines an index reference cf. This reference models the value stored at position 0 in SREG.

Index references are fairly similar in use to Why3's ref references. In both cases mutable, memory locations can be modeled with separate references, where modifications are specified in terms of just this reference. (Here memory refers to registers and RAM or any other form of volatile memory.) This allows for a syntax that is very close to that of Why3's ref references: if one were to rewrite WhyML code using references to Asm3 code the specifications would need very few changes. The writes and reads annotations remain unchanged while in the pre- and postconditions the! ref dereference operators need to be replaced with \$. Listings 17, 18 show how the syntax of working with index references compares to working with ref in WhyML<sup>8</sup>. Observe that the specifications of simple\_add in listings 17 and are nearly identical.

$<sup>^8\</sup>mathrm{Do}$  note that, although rd rr : reg appears in listings 17 and 18 the meaning of reg differs.

#### **Listing 17** Asm3: defining a simple addition instruction using index references

```

type reg_index = <range 0 31>

index reg = create_index regs (reg_index, byte)

val instr simple_add (rd rr : reg)

ensures Post_rd { $rd = mod (old ($rd + $rr)) 256 }

reads { rd, rr }

writes { rd }

```

Listing 18 WhyML: defining a simple addition instruction using ref references

```

type reg = ref byte

val simple_add (rd rr : reg): unit

ensures Post_rd { !rd = mod (old (!rd + !rr)) 256 }

reads { rd, rr }

writes { rd }

```

Syntax comparison between modeling registers in Asm3 with index references and modeling registers with ref references in WhyML

Unlike WhyML's **ref** references, it is possible to work with offsets. This makes it possible to define instructions that interact with consecutive sections of memory while only passing a single element of this memory. An example of this is given in listing 19, which not only operates on registers **rd** and **rr**, which are given as arguments, but also on the registers next to those registers. Listing 19 also demonstrates why it

Listing 19: Axiomatic defintion of the AVR movw instruction in Asm3

```

val instr movw (rd rr: reg)

writes { rd, rd+1 }

reads { rr, rr+1 }

requires Pre_rd_rr { mod rd 2 = 0 /\ mod rr 2 = 0 }

ensures Post_rd { $rd = old ($rr) }

ensures Post_rdp1 { $(rd+1) = old $(rr+1) }

```

can be useful to be able to interpret index references as a value, rather than just a reference. Here a precondition is given to check that rd and rr are even as the movw instruction in AVR architecture requires its arguments to be aligned to register pairs.

We have previously demonstrated that it is possible to work with offsets and aliasing in WhyML by modeling memory with a single mutable object. The previous description of index references and indexed objects may lead one to expect that index references just introduce a new syntax for working with a mutable map. That is not the case, however. The Asm3 framework tracks the state of the memory at each position in the indexed object. As long as Asm3 can determine that the memory pointed to by an index reference was last modified from this specific index reference or wasn't modified at all, Asm3 models this memory separately from the rest of the memory modeled by the indexed object. For example, for the following abstract block (abstract blocks are sections of code along with a specification enclosed by the begin and end keywords):

Listing 20: Abstract block containing two load immidate instructions.

```

begin ensures { $r0 = 37 /\ $r1 = 0 }

```

In listing 18 it denotes a type while in 17 it declares reg as a an index into the virtual variable regs.

```

ldi r0 37;

ldi r1 0

end

```

Asm3 will generate a proof formula that looks similar to:

```

\forall_{r0_{new},\,r1_{new}}\ r0_{new}=37\rightarrow r1_{new}=0\rightarrow r0_{new}=37\wedge r1_{new}=0

```

Observe that the new values of registers  $\tt r0$  and  $\tt r1$  are modeled separately using the variables  $\tt r0_{new}$  and  $\tt r1_{new}$ . This is quite different from the proof formula that Why3 would generate if we would model registers with a single mutable map. In that case we would get a formula that would look similar to:

$$\begin{array}{ll} \forall_{\mathrm{regs_{temp}}} & \mathrm{regs_{temp}} = \mathrm{regs_{old}}[0 \leftarrow 37] & \rightarrow \\ \forall_{\mathrm{regs_{new}}} & \mathrm{regs_{new}} = \mathrm{regs_{temp}}[1 \leftarrow 0] & \rightarrow \\ & \mathrm{regs_{new}}[0] = 37 \wedge \mathrm{regs_{new}}[1] = 0 \end{array}$$

Where regs<sub>old</sub> models the initial state of the registers.

The syntax for index references generally leads to more succinct specifications than working with mutable maps. An example of the difference is given in listings 21 and 22. Observe that the postcondition Post\_rd in the Asm3 version is much shorter than the one in the WhyML version.

**Listing 21** Asm3: defining a simple addition instruction using index references

```

type reg_index = <range 0 31>

index reg = create_index regs (reg_index, byte)

val instr simple_add (rd rr : reg)

ensures Post_rd { $rd = mod (old ($rd + $rr)) 256 }

reads { rd, rr }

writes { rd }

may_alias {rd with rr}

```

Listing 22 WhyML: defining a simple addition instruction using mutable maps

```

type reg = <range 0 31>

val regs : ref (map reg byte)

val simple_add (rd rr : reg): unit

ensures Post_rd { !regs = old (!regs[rd <- mod (!regs[rd] + !regs[rr]) 256]) }

reads { regs }

writes { regs }</pre>

```

Syntax comparison between modeling registers in Asm3 with index references and modeling registers in WhyML with indices of an integer type into a mutable map

One might wonder why indexed objects are assigned names (such as regs and sreg in listing 16). The user can only interact with these objects through index references, so why mention these objects at all? The reason is that it isn't always possible to model the values index references point to separately. In cases where index references may be aliased and to one of them an assignment is made these values will be modeled using a single map. To make it clear where this map originates from, this map will appear in VCs as a variable with its name based on the name assigned to the indexed object.

#### 4.1.2 Multi-byte integers

In assembly code it is often necessary to store values with a higher bit size than can be stored at a single memory location, for example in AVR architecture a 32 bits number would need to be stored in 4 separate registers (or other memory locations). In Asm3 it is straightforward to describe values spread over multiple memory locations. It includes an operator for concatenating sized integers: for example, for sized integer expressions<sup>9</sup> x and y, the expression x::y gives a value of x and y concatenated. This concatenation is defined as  $[x::y] = [x] + radix(x) \times [y]$ , where [e] is the semantic value of the Asm3 formula e.

Asm3 also contains syntax for describing values stored in consecutive locations in memory. With the triple dot operator  $f(x) \dots y$  one can specify numbers stored over y consecutive memory locations. In its current state this is only defined for  $\{[x] \dots y] = [x::x(x+1): \dots ::x(x+y-1)]$  and for the map get operator  $[]([x[z] \dots y] = [x[z]::x[z+1]: \dots ::x[z+y-1]])$ . If modeling a big endian architecture a negative value for y can be used to reverse the order of the components of the value. Examples:  $[x^2 \dots y] = [x^2 \dots y]$ , where  $[x^2 \dots y] = [x^2 \dots y] = [x^2 \dots y]$ , where  $[x^2 \dots y] = [x^2 \dots y]$ , where  $[x^2 \dots y]$  and  $[x^2 \dots y]$  are three consecutive registers.

The ensures part of the specification of movw given in listing 19 could alternatively be given as ensures { rd...2 = old (rr...2) }.

#### 4.1.3 Alias annotations

Unlike references in WhyML, whether index references will or will not alias doesn't have to be statically defined. The user only has to specify if indices are allowed to alias. To accomplish this the Asm3 language includes the may\_alias annotation. With this annotation, the user can specify that in invocations of a macro, given pairs of index object indices may alias. For each invocation of a macro, the framework checks if any aliasing that would occur is allowed. Take the following example:

Listing 23: Example of an procedure in which some arguments may be aliased.

```

let macro add_reg_to_word (dst src tmp: reg)

requires { $dst...2 + $src <= 0xFFFF }

ensures { $dst...2 = old ($dst...2 + $src) }

may_alias { src with tmp }

may_alias { dst, dst+1 with src }

writes {dst, dst+1, tmp}

=

add dst src;

clr tmp;

adc (dst+1) tmp</pre>

```

This macro adds src to dst and adds the carry bit to the register that follows dst. add\_reg\_to\_word r2 r2 r1 would be allowed as while dst src both map to r2 this is allowed by the specification. add\_reg\_to\_word r2 r2 r2 on the other hand wouldn't be allowed as then dst tmp both map to r2 which isn't allowed according to the specification (may\_alias is reflexive, but not transitive).

#### 4.1.4 Expressive power of index references

Section 4.1.1 states that index refrences can be thought of as a hybrid approach between WhyML's references and working with mutable maps, but didn't go into detail about what that means.

$<sup>^9</sup>$ x is positive and has a radix. For for binary values the radix is  $2^b$  where b is the number of bits of the integer size. The radix of a byte is 256, so for any byte i the following holds:  $0 \le i < 256$ .

In cases where aliasing cannot occur or cases where no writes occur to indices that can be aliased (with an index passed as argument or a statically defined index), index references can be considered to be a less restrictive version of WhyML's references. Like with WhyML's references, in the generated proof obligations the value stored at the location of each index is modeled with separate variables. Take add a b (\*a := a + b\*); assert {\$a = 5 /\ \$b = 3} where a cannot alias with b, the following formula would appear in the obligation generated for this code:

$$a_{\text{new}} = a_{\text{old}} + b_{\text{old}} \rightarrow a_{\text{new}} = 5 \land b_{\text{old}} = 3$$

Here  $a_{\rm old}$  and  $b_{\rm old}$  model the original values of a and b respectively and variable  $a_{\rm new}$  models the new value stored in a.

Once a write occurs to an index that may be aliased with another index the modeled memory starts to behave much more similarly to a map. If we again look at add a b; assert  $\{a = 5 / \ b = 3\}$ , now with the condition that a and b are allowed to alias.

```

a_{\text{new}} = a_{\text{old}} + b_{\text{old}} \land regs_{\text{new}} = regs_{\text{old}}[b \leftarrow b_{\text{old}}][a \leftarrow a_{\text{new}}] \rightarrow a_{\text{new}} = 5 \land regs_{\text{new}}[b] = 3

```

Now maps  $regs_{\text{new}}$  and  $regs_{\text{old}}$  along with locations a and b (for a and b respectively) appear in the formula to model the new value stored in b. The sub-formula  $regs_{\text{new}} = regs_{\text{old}}[b \leftarrow b_{\text{old}}][a \leftarrow a_{\text{new}}]$  constructs a new map to model the new value of b (Here it is assumed that b is not already modeled with  $regs_{\text{old}}$ ). If a and b are indeed aliases  $regs_{\text{new}}[b]$  will be equal to  $a_{\text{new}}$ , while it will be  $b_{\text{old}}$  if these indices do not alias. While the new value of a is now stored in  $regs_{\text{new}}$  we can continue to model a with the new incarnation  $a_{\text{new}}$  until we would write to b.

As soon as a write occurs to an index that could be aliased with other indices these other indices are no longer modeled separately. In these cases Asm3 will construct maps, write the old value stored at the affected indices to it and include the new value of the index that was written to.

Using maps directly is much more powerful, however, as index reference appearing in terms must be statically defined with respect to local (arguments passed to the current macro) or global indices (globally defined indices). This isn't an issue when modeling statically addressed memory such as registers<sup>10</sup>, but this makes index references generally unsuitable for modeling main memory. For example, it isn't suitable for modeling a loop that doesn't iterate a predetermined amount of times (the loop can not be unrolled at compile time) that writes to a new location every iteration. An example of this is shown in listing 24 (assume that n isn't a constant).

Listing 24: Example of something (written in C) that cannot be modeled with just index references

```

// given arrays x and y, positive integer n

for (int i = 0; i < n; i++) {

x[i] = y[i];

}</pre>

```

The advantages index references have over simple mutable maps in Why3 are that it is easier to specify which specific parts of memory get modified and that values at separate indices can often be modeled in a fully separate way. This last difference can make a large difference in a automatic theorem prover's ability to verify a property in a reasonable amount of time.

#### 4.1.5 Weak types

As previously stated in section 3.3.1 Why3 1.0 changed the way type invariants are modeled in its SMT2 output. This led to an unacceptable loss of prover performance

$<sup>^{10}</sup>$ Architectures exist in which the register being accessed can be determined at run time. Index references aren't a good match for code in which this is prevalent.

when performing a simple syntactic port of our verification work of a curve25519 implementation written in AVR assembly. To be specific: in Why3 0.88 we would model the registers and main memory as an instance of type address\_space, which was defined as:

```

type address_space = { mutable data: map int int }

invariant { forall i. 0 <= self.data[i] < 256 }</pre>

```

In the SMT2 input it generated for SMT solvers instances of this type were modeled using arrays of integers along with a premise that the invariant held for this instance. In Why3 1.0 and later address\_space would be modeled as some abstract type with a projection function<sup>11</sup> to an array of integers. Here the type invariant is encoded into the projection function. While this is a perfectly valid way of modeling types with type invariants, the fact that the values are no longer directly modeled but only the projection of these values, had a profound negative effect on the performance of provers used previously.

Asm3 provides an alternative way of modeling types with type invariants. It can model a limited number of type invariants in a similar way as to how it was modeled in earlier versions of Why3. Currently, this is limited to modeling range types, maps containing range types, maps containing range types, etc.

Asm3 can model the type invariants of these types using only integers and arrays. For example: in both WhyML and Asm3 one could model bytes with type byte = <range 0 255>. As previously stated in section 2.2.1 a byte defined this way is not modeled as an integer, but as some abstract type byte with an projection function to the integers. In Asm3 bytes can also be defined with weak\_type byte = <range 0 255>, in which case bytes will be modeled as integers for which the following (automatically generated) predicate applies: predicate byte'constraint (b: int) = (-1) < b < 256. We will refer to types modeled this way as weak types.

To demonstrate how this difference in modeling bytes translates to different verification conditions it may be useful to have a practical example of the differences. For example, when modeling bytes using a Why3 range type the following VC would get generated for the postcondition of avr\_double from listing 16:

Listing 25: Proof goal of listing 16 when modeling bytes using Why3s type system

```

constant dst'0 : byte

constant dst'1 : byte

add_Post_dst: byte'int r5'1 = mod (byte'int dst'0 + byte'int dst'0) 256

goal: byte'int dst'1 = 2 * byte'int dst'0

```

If we were to model bytes using a weak type the following VC would get generated:

Listing 26: Proof goal of listing 16 when modeling bytes using weak types

```

constant dst'0 : int

constant dst'1 : int

H1: byte'constraint dst'0

H: byte'constraint dst'1

add_Post_dst: dst'1 = mod (dst'0 + dst'0) 256

goal: dst'1 = 2 * dst'0

```

Note that the new value dst'1 of register dst is described directly while previously only information on byte'int dst'1 was provided. For some SMT solvers, notably Z3 this can make a significant difference in verification time and/or memory usage. It is worth noting that Why3's IDE offers an option to hide applications of projection function

<sup>&</sup>lt;sup>11</sup>The projection functions generated by Why3 are not always visible to the user. In some cases the projection function only appears in the input Why3 generates for the provers.

such as byte'int that Why3 itself inserted. In this case the formula add\_Post\_dst as well as the goal formula would *look* identical.

Outside of the generated VCs, weak types have the advantage that less casting functions need to be used, which can make specifications a bit cleaner in cases where Why3 cannot insert the projection function itself.

Weak types come with their own drawbacks: these "types" are not modeled using Why3's type system, meaning that they cannot be used in the definitions of normal types and are not available within logic terms. If bytes are modeled using a weak type, forall x: byte. f x = y will be rejected by Why3's type system (it will complain that it doesn't know type byte) however forall x: int. byte'constraint  $i \rightarrow f$  (x) = y will work fine.

#### 4.2 VC generation in the Asm3 framework

Why3 has support for language plugins. These plugins allow users to prove the specifications of code written in languages other than WhyML. Normally this is accomplished by transforming such code into a WhyML AST representation of the code. After parsing the process of generating VCs is identical to that of code written in WhyML. Why3 itself provides plugins to allow working with a small subset of C and Python.

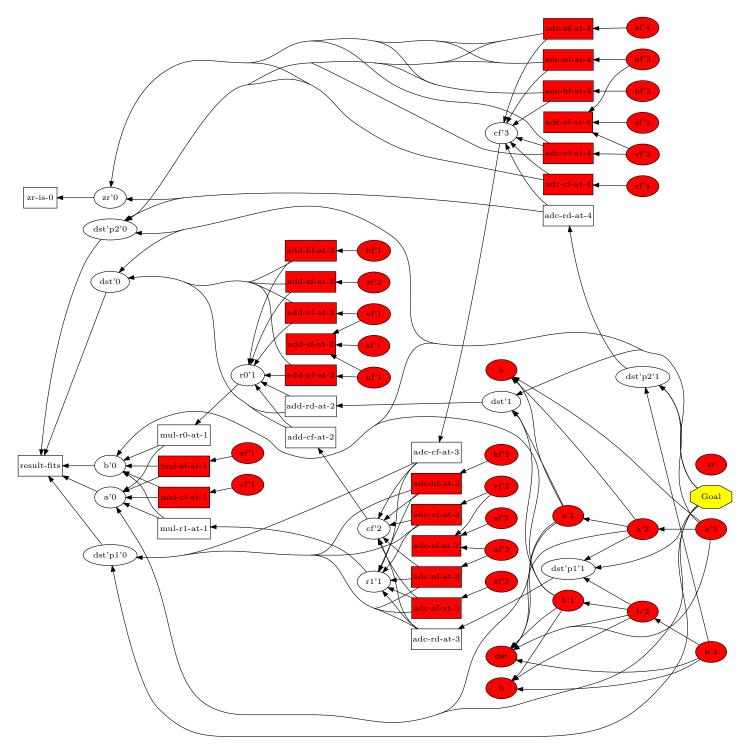

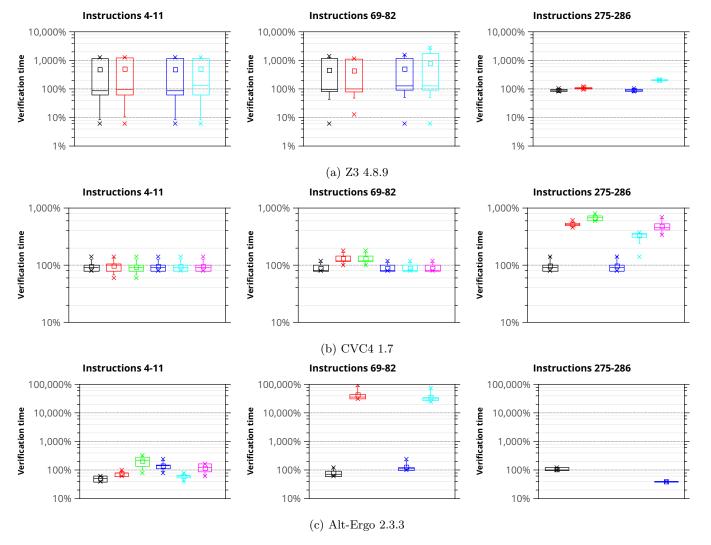

This method wouldn't work well with Asm3, as the Asm3 language doesn't map well to WhyML and Why3's VC generator isn't suitable for applying the optimizations that Asm3 can perform on each sub-goal. Because of this the Asm3 plugin features its own VC generator. A large difference between Why3's VC generator and Asm3's VC generator is that Asm3's VC generator collects information on which premises and variables are likely to be useful for each sub-goal. This information can then be used to generate an optimized VC for each sub-goal. Why3's VC generator, on the other hand, does not keep track of this information and generates a single VC containing the combined proof obligation of all sub-goals.