# MASTER THESIS COMPUTING SCIENCE

# RADBOUD UNIVERSITY

# Optimizing the MEDS Implementation for ARMv8

Author: Lars Jeurissen s1022856 lars.jeurissen@ru.nl First supervisor/assessor: prof. dr. Peter Schwabe peter@cryptojedi.org

Second supervisor: dr. Simona Samardjiska simonas@cs.ru.nl

# Abstract

As the risk of quantum computers breaking current cryptographic schemes grows, the need for post-quantum cryptography becomes more pressing. The recent NIST competition on post-quantum signature schemes has led to the creation of MEDS, a signature scheme based on the Matrix Code Equivalence (MCE) problem. In this work, we optimize the existing MEDS implementation for the ARMv8 CPU architecture using parameter-specific optimizations and NEON SIMD instructions.

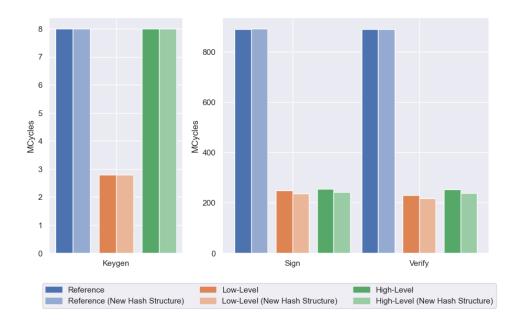

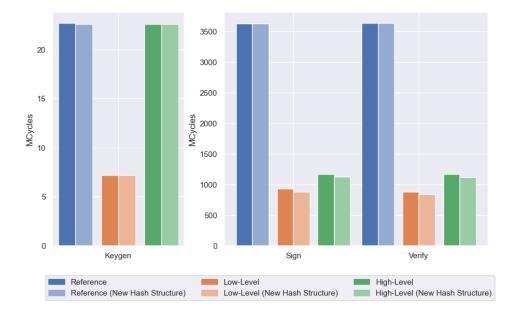

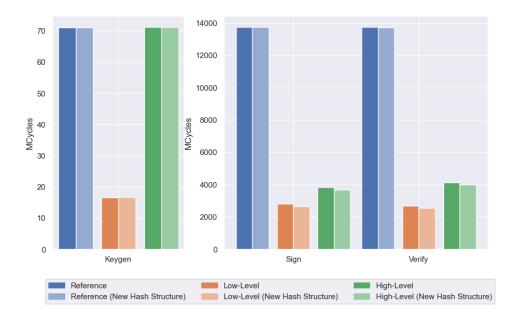

We explore two approaches: a low-level approach that optimizes the individual operations of the scheme and a high-level approach that parallelizes over the main commitment loop. The low-level approach gives the best results, with a speedup of  $3.2\times$  for key generation,  $3.9\times$  for signing, and  $4.1\times$  for verification, in NIST category 3, on the ARM Cortex-A72.

Additionally, we suggest an optimization to the hashing structure used in MEDS which, when combined with the low-level optimizations, increases the speedup for signing and verification to  $4.1\times$  and  $4.4\times$ , respectively, in NIST category 3, on the ARM Cortex-A72.

We also provide a brief analysis of the performance on the Apple M2, which shows that our optimizations are even more effective on this architecture.

# Contents

| 1 | Intr           | roduction 3                                                  |

|---|----------------|--------------------------------------------------------------|

|   | 1.1            | Context                                                      |

|   | 1.2            | Motivation                                                   |

|   | 1.3            | Scope                                                        |

|   | 1.4            | Related work                                                 |

|   | 1.5            | Contributions                                                |

|   | 1.6            | Outline                                                      |

| 2 | $\mathbf{Pre}$ | liminaries 8                                                 |

|   | 2.1            | Notations                                                    |

|   | 2.2            | Matrix Equivalence Digital Signature (MEDS) 9                |

|   |                | 2.2.1 Signature schemes                                      |

|   |                | 2.2.2 Codes and Matrix Code Equivalence (MCE) 10             |

|   |                | 2.2.3 Sigma protocol and Fiat-Shamir transform 12            |

|   |                | 2.2.4 Parameter sets                                         |

|   |                | 2.2.5 MEDS algorithms                                        |

|   | 2.3            | ARMv8, Cortex-A72, and NEON                                  |

|   |                | 2.3.1 Vectorization and SIMD                                 |

|   |                | 2.3.2 Cortex-A72 Micro-Architecture 21                       |

|   | 2.4            | Optimizing cryptographic schemes                             |

|   |                | 2.4.1 Branching and conditional execution                    |

|   |                | 2.4.2 Data-dependent memory access 26                        |

|   |                | 2.4.3 Non-constant-time operations                           |

|   |                | 2.4.4 Preventing timing attacks with Valgrind and Timecop 26 |

|   | 2.5            | Modular reduction                                            |

|   |                | 2.5.1 Barrett reduction                                      |

| 3 | Pro            | filing 30                                                    |

|   | 3.1            | Profiling techniques                                         |

|   |                | 3.1.1 Cycle counting                                         |

|   | 3.2            | MEDS profiling results                                       |

|   |                | 3.2.1 Measurement setup                                      |

|              |              | 3.2.2    | Result analysis                               |    |     | ٠   |   | •  | 32              |

|--------------|--------------|----------|-----------------------------------------------|----|-----|-----|---|----|-----------------|

| 4            | Met          | hodolo   | $_{ m gy}$                                    |    |     |     |   |    | 35              |

|              | 4.1          | Modula   | ar reduction                                  |    |     |     |   |    | 36              |

|              |              | 4.1.1    | Choosing $k$ for Barrett reduction            |    |     |     |   |    | 36              |

|              |              | 4.1.2    | Implementation                                |    |     |     |   |    | 37              |

|              |              | 4.1.3    | Freeze operation                              |    |     |     |   |    | 38              |

|              | 4.2          | Low-le   | vel optimization                              |    |     |     |   |    | 40              |

|              |              | 4.2.1    | Matrix multiplication                         |    |     |     |   |    | 40              |

|              |              | 4.2.2    | Matrix systemizer                             |    |     |     |   |    | 46              |

|              |              | 4.2.3    | Isometry derivation                           |    |     |     |   |    | 50              |

|              | 4.3          | High-le  | evel optimization                             |    |     |     |   |    | 54              |

|              |              | 4.3.1    | Parallelization of datatypes and supplemental | al | go: | rit | h | ms | 55              |

|              |              | 4.3.2    | Parallelization of commitment computations    |    |     |     |   |    | 58              |

|              |              | 4.3.3    | Limitations                                   |    |     |     |   |    | 60              |

|              | 4.4          | Bitstre  | am filling                                    |    |     |     |   |    | 60              |

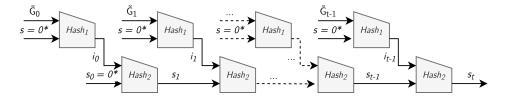

|              | 4.5          | Hash s   | tructure                                      |    |     |     |   |    | 62              |

|              |              | 4.5.1    | Hash structure optimization                   |    |     |     |   |    | 63              |

|              |              | 4.5.2    | Implementation                                |    |     |     |   |    | 64              |

|              | 4.6          | Non-co   | onstant-time implementations                  |    |     |     |   |    | 64              |

|              |              | 4.6.1    | Finite field inversion                        |    |     |     |   |    | 64              |

|              |              | 4.6.2    | Matrix systemizer                             |    |     |     |   |    | 65              |

| _            | D            | 14       |                                               |    |     |     |   |    | cc              |

| 5            | Res          |          | 1+::                                          |    |     |     |   |    | 66              |

|              | 5.1          |          | vel optimizations                             |    |     |     |   |    | 66              |

|              | <b>F</b> 9   | 5.1.1    | Theoretical and actual speedup factors        |    |     |     |   |    | 68              |

|              | 5.2          |          | ng implementation variants                    |    |     |     |   |    | 69              |

|              | 5.3          |          | l performance                                 |    |     |     |   |    | 72              |

|              | 5.4          | _        | rison to similar schemes                      |    |     |     |   |    | 75<br>70        |

|              | 5.5          | Discuss  | sion                                          |    |     | •   | ٠ | •  | 78              |

| 6            | Con          | clusior  | ns                                            |    |     |     |   |    | <b>7</b> 9      |

| 7            | Futi         | ure Wo   | ark                                           |    |     |     |   |    | 81              |

| •            | 7.1          |          | r optimization possibilities                  |    |     |     |   |    | 81              |

|              | $7.1 \\ 7.2$ |          | onal research topics                          |    |     |     |   |    | 82              |

|              | 1.4          | Addition | onar research topics                          |    |     | •   | • | •  | 02              |

| $\mathbf{A}$ | ME           | DS Alg   | gorithms                                      |    |     |     |   |    | 92              |

|              | A.1          | Notatio  | ons and functions                             |    |     |     |   |    | 92              |

|              |              | A.1.1    | Notations                                     |    |     |     |   |    | 92              |

|              |              | A.1.2    | Functions                                     |    |     |     |   |    | 92              |

|              | A.2          |          | lgorithms                                     |    |     |     |   |    | 94              |

|              | A.3          |          | mental algorithms                             |    |     |     |   |    | 97              |

| В            | Ben          |          | k Results                                     |    |     |     |   |    | 99              |

| _            |              |          | A TOODGIUD                                    |    |     |     |   |    | $\sigma \sigma$ |

# Chapter 1

# Introduction

# 1.1 Context

As the research on quantum computers progresses, we are getting increasingly closer to the point where quantum computers will be able to utilize algorithms such as Shor's algorithm [69] and Grover's algorithm [44] to break various cryptographic schemes, causing the absolute collapse of the present public key algorithms that are considered secure [53]. As the majority of the digital world relies on the security of these cryptographic schemes, this will have devastating consequences for the security of not only the internet, but also financial transactions, secure communication, and many other critical sectors.

The solution to this problem lies in the development of cryptographic schemes that are secure against quantum computers. Such algorithms have been around for a long time, but this area of research has experienced a boost in attention ever since the National Institute of Standards and Technology (NIST) started the post-quantum cryptography (PQC) standardization process in 2017 [60]. The goal of this process is to standardize cryptographic schemes that are secure against quantum computers.

In 2022, NIST announced the set of selected PQC algorithms, which included three digital signature schemes: CRYSTALS-Dilithium [36], Falcon [39], and SPHINCS<sup>+</sup> [21]. As two of these schemes are based on structured lattices, NIST announced a second competition in the PQC standardization process, which aims to find additional general-purpose signature schemes that are not based on structured lattices. One of the candidates in this competition is Matrix Equivalence Digital Signature (MEDS) [29]. MEDS is a code-based digital signature scheme based on the notion of Matrix Code Equivalence. In this thesis, we aim to optimize the performance of the MEDS implementation for the ARMv8 architecture.

# 1.2 Motivation

The need for digital signature schemes that are secure against quantum computers is increasing. Of course, the security of these schemes is the most important aspect, but the speed at which an implementation can create or verify a signature is also important. The speed of a digital signature scheme is essential for many applications, such as TLS/SSL certificate verification, electronic payments, and blockchain transactions.

Although the MEDS scheme is actively being optimized in terms of key and signature sizes, the performance of the scheme is still lacking. The reported signature verification times are in the order of hundreds of milliseconds and sometimes even seconds, depending on the security level and the chosen parameters. Traditional digital signature schemes such as RSA [64] and ECDSA [45] can verify thousands of signatures per second on both modern and even older hardware [34, 49]. The new post-quantum digital signature schemes must eventually achieve similar performance levels.

The two most widely used CPU architectures in the world are x86 (used in Intel and AMD processors) and ARM. ARM is used in a wide variety of devices, for example,

- mobile devices and tablets such as the Apple iPhone and iPad, Samsung Galaxy, and Google Pixel;

- embedded and Internet of Things (IoT) devices such as smart light bulbs, smart thermostats, and smart doorbells;

- Apple M1/M2/M3 chips used in Apple MacBooks.

Optimizing the MEDS implementation for the ARMv8 architecture will improve the MEDS performance for these devices, as well as provide valuable insights into the performance of MEDS on ARMv8.

# 1.3 Scope

The goal of this thesis is to optimize the performance of the MEDS implementation for the ARMv8 architecture to the extent that further optimizations are either infeasible or provide only minimal performance improvements. To achieve this goal, we investigate the following research questions:

RQ I. How is CPU time distributed across the code of the MEDS implementation?

- RQ II. What optimizations can be made to improve the performance of the MEDS implementation for the ARMv8 architecture?

- a) Which of these optimizations can be used in general for any architecture?

Since the submission of the original MEDS implementation to the NIST PQC competition in 2023 [28], the authors have proposed several optimizations to the scheme to reduce the size of the public key and the signatures [30]. The authors have provided a new reference implementation for MEDS that implements these optimizations. In this thesis, we focus on optimizing this new implementation for the ARMv8 architecture. There are two main reasons for this focus:

- Research has been done on the optimization of the original MEDS implementation for the x86 architecture (using AVX512 instructions) in [1, 2]. Although the ARMv8 architecture is different and an optimization of the original implementation for ARMv8 would be interesting, we believe that optimizing the new implementation provides better insights into the performance of a state-of-the-art MEDS implementation.

- The new MEDS variant has quite a few differences compared to the original, but the core structure and algorithms remain the same. This suggests that the optimizations that we make for the new implementation can also be applied to the original implementation, should the need arise.

In this thesis, when talking about the MEDS implementation, we refer to the new reference implementation that was provided by the authors in [30], unless stated otherwise.

# 1.4 Related work

Digital signature schemes and their optimization have been the subject of many research papers over the last few decades. Traditional widely-used digital signature schemes such as RSA [64], ECDSA [45], and EdDSA [20] have received optimizations for various versions of ARM CPUs over the years [74, 75, 81]. The introduction of NEON [6] (ARM's SIMD instruction set) in ARMv7 has led to a new wave of optimizations for traditional digital signature schemes based on NEON instructions, starting with the work of Bernstein and Schwabe in 2011 [22]. This work has been continued for both symmetric and asymmetric cryptographic algorithms over the years [11, 42, 67, 68, 78].

The introduction of the NIST post-quantum cryptography standardization process in 2016 has led to the development of many new public key encryption

(PKE), key encapsulation mechanism (KEM), and digital signature schemes that are believed to be secure against quantum computers. Research into the NEON optimization of PKE/KEM schemes soon followed [57, 58, 61, 70, 73]. The optimization of post-quantum digital signature schemes has mostly focused on finalists of the competition: CRYSTALS-Dilithium [36], Falcon [39], SPHINCS<sup>+</sup> [21], and Rainbow [35] have received NEON-based optimizations for ARMv8 CPUs [17, 18, 46, 47, 50, 59].

More relevant to this thesis is the work on the implementation and optimization of other (code-based) schemes that are similar to MEDS. Many schemes in the ongoing NIST PQC competition, including ALTEQ [26], LESS [12], PERK [3], and RYDE [5], have been optimized for x86 CPUs using AVX2/AVX512 [63] instructions. However, only a few schemes, such as MiRitH [4] and UOV [24], have been optimized for ARMv8.

Of particular interest is the work on the optimization of the original MEDS implementation for the x86 architecture using AVX512 instructions [1, 2]. Both this optimization and ALTEQ [26] provide the high-level optimization idea of intertwining multiple mathematical objects to allow for more parallelism in the signature generation and verification algorithms. Besides this, LESS [12] explores the low-level optimization of the computation of the RREF of a matrix, which is also used in MEDS.

Besides the use of NEON instructions, the use of already optimized algorithms can greatly improve the performance of a cryptographic scheme. Common cryptographic building blocks such as the KECCAK permutation [23] (which is used in MEDS) and Montgomery multiplication [54] have already been optimized for various ARM CPUs [18, 27, 66] and are used in many digital signature schemes.

# 1.5 Contributions

This thesis makes the following contributions:

- We provide a detailed profiling of the MEDS implementation for the ARMv8 architecture (specifically, the ARM Cortex-A72), which gives insights into the performance bottlenecks of the implementation. These profiling results, although specific to the ARMv8 architecture, can be used as a guideline for optimizing the MEDS implementation for other architectures.

- We provide two mutually exclusive optimizations for the MEDS implementation: a low-level optimization that focuses on the optimization of underlying functions such as matrix multiplication and the matrix systemizer, and a high-level optimization that focuses on the paral-

lelization of the commitment loop in the signature and verification algorithms.

- We provide novel assembly implementations of essential functions such as modular reduction and matrix multiplication that are optimized for the ARMv8 architecture. These implementations can be used in other cryptographic schemes that require similar functions.

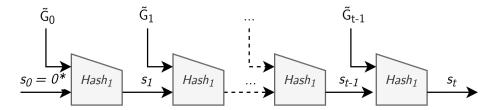

- We propose a change to the MEDS scheme that allows for larger parallelizability in the hashing process. This change provides a speedup of both signature generation and verification.

- We present the benchmarking results of the optimized MEDS implementation on the ARM Cortex-A72 and the Apple M2 and compare these results to the reference implementation.

- We compare MEDS to similar digital signature schemes in terms of performance and show that the optimized MEDS implementation is competitive with these schemes.

# 1.6 Outline

In Chapter 2, we provide the necessary background information on the functioning of MEDS and the specific details of the ARMv8 architecture. In Chapter 3, we discuss the profiling techniques that we use to obtain an understanding of the performance of MEDS and present the profiling results of the MEDS implementation. Following that, in Chapter 4, we discuss the optimization techniques that we use to optimize the MEDS implementation. In Chapter 5, we present and discuss the benchmarking and profiling results of our optimizations. We conclude the thesis in Chapter 6, where we reflect on the results that we obtained. Finally, we discuss the remaining future work in Chapter 7.

All code used in this thesis is available on GitHub for reference under the GPL-3.0 license.<sup>1</sup>

<sup>1</sup>https://github.com/MeItsLars/MEDS-ARMv8-optimization-thesis

# Chapter 2

# **Preliminaries**

In this chapter, we provide the relevant background concepts on the functioning of the MEDS scheme, the ARMv8 architecture, the optimization of cryptographic schemes and modular reduction. Additionally, we give a small overview of the notations that we use in this thesis.

# 2.1 Notations

In the MEDS scheme and this thesis, we use the following notations:

- $\mathbb{F}_q$ : The finite field of size q.

- $\mathbb{F}_q^{m \times n}$ : The set of matrices of size  $m \times n$  (m rows and n columns) over  $\mathbb{F}_q$ , meaning that each element of the matrix is an element of  $\mathbb{F}_q$ .

- $\mathrm{GL}_k(q)$ : The set of all invertible  $k \times k$  matrices over  $\mathbb{F}_q$ .

- $\mathbf{A} \in \mathbb{F}_q^{m \times n}$ : A matrix  $\mathbf{A}$  of size  $m \times n$  over  $\mathbb{F}_q$ .

- $\mathbf{I}_n$ : The identity matrix of size  $n \times n$ .

- A[i][j]: The element in the *i*-th row and *j*-th column of matrix A.

- $\mathbf{A}^T$ : The transpose of matrix  $\mathbf{A}$ .

- $A^{-1}$ : The inverse of matrix A.

- $\mathbf{A} \times \mathbf{B}$  or simply  $\mathbf{AB}$ : The matrix product of  $\mathbf{A}$  and  $\mathbf{B}$ .

- A + B: The element-wise matrix sum of A and B.

- $A \otimes B$ : The Kronecker product of A and B.

- $\pi_{\mathbf{A},\mathbf{B}}(\mathbf{G})$ : Simplified notation for the operation  $\mathbf{G}(\mathbf{A}^T \otimes \mathbf{B})$ .

- $\bullet$  (A  $\mid$  B): The matrix formed by concatenating matrices A and B.

# 2.2 Matrix Equivalence Digital Signature (MEDS)

Matrix Equivalence Digital Signature (MEDS) [29] is a code-based digital signature scheme and the candidate in the NIST PQC competition that we aim to optimize in this thesis. A series of optimizations for the key and signature sizes of MEDS have already been proposed by the authors of the scheme [30], together with a new reference implementation that implements these optimizations. In this paper, we focus our efforts on optimizing this new reference implementation.

# 2.2.1 Signature schemes

A digital signature scheme is a cryptographic scheme with the purpose of verifying the authenticity of a message. The scheme allows a party to sign a piece of data such as a message or a document, after which any party can verify the signature and thereby the authenticity of the data.

A digital signature scheme consists of three algorithms:

- **Key generation**: This algorithm generates 2 keys, a private key and a public key. The private key is used to sign the data, and the public key is used to verify the signature.

- **Signature generation**: Given a message and the private (and sometimes public) key, this algorithm generates a signature for the message.

- **Signature verification**: Given a message, a signature, and the public key, this algorithm verifies the signature over the message.

The formal definition of a digital signature scheme is given in Definition 2.2.1.

# **Definition 2.2.1** (Signature Scheme, following [40]).

A digital signature scheme is a tuple of algorithms (Keygen, Sign, Verify) where:

- Keygen( $1^n$ ) generates a key pair (pk, sk), where pk is the public key and sk is the private key. The parameter n represents the security parameter which determines the security level of the scheme.

- Sign(sk, m) generates a tag T which represents the signature over the message m using the private key sk.

- Verify(pk, m, T) outputs 1 if the tag T is a valid signature over the message m using the public key pk, and 0 otherwise.

Such that, given  $(pk, sk) \leftarrow \text{Keygen}(1^n)$ :

$$Verify(pk, m, Sign(sk, m)) = 1$$

for all m (with a negligible probability of error).

# 2.2.2 Codes and Matrix Code Equivalence (MCE)

Most PQC schemes are based on mathematical concepts such as linear codes, isogenies, lattices and multivariate equations. These concepts have associated decisional and computational problems that are believed to be hard to solve for both classical and quantum computers. MEDS is based on the notion of Matrix Code Equivalence (MCE), which is closely related to the notion of Code Equivalence that is used in LESS [25], a similar scheme in the NIST PQC Signature competition. In this section, we provide background information on codes and the MCE problem. A more detailed explanation of matrix codes can be found in [41]. A study on the hardness of the MCE problem, as well as related problems, can be found in [62].

#### Codes

Each matrix has a so-called rank, of which the definition is given in Definition 2.2.2.

# **Definition 2.2.2** (Matrix Rank).

The rank of a matrix  $\mathbf{A} \in \mathbb{F}_q^{m \times n}$ , denoted as rank $(\mathbf{A})$ , is the maximum number of linearly independent rows (or columns) of  $\mathbf{A}$ .

The matrix rank can be used to create a distance metric between matrices. This metric is called the rank metric, and its definition is provided in Definition 2.2.3.

**Definition 2.2.3** (Rank Metric, following [41]).

The rank metric between two matrices  $\mathbf{A}, \mathbf{B} \in \mathbb{F}_q^{m \times n}$  is defined as:

$$d(\mathbf{A}, \mathbf{B}) = \operatorname{rank}(\mathbf{A} - \mathbf{B})$$

where  $\mathbf{A} - \mathbf{B}$  is the element-wise difference of the matrices.

Using the rank metric, we can define a (matrix) rank metric code: the underlying mathematical object of MEDS. The definition of a rank metric code is given in Definition 2.2.4.

**Definition 2.2.4** ((Matrix) Rank Metric Code, following [41]). A rank metric code (also called matrix code)  $\mathcal{C}$  is a subspace of  $\mathbb{F}_q^{m \times n}$ , meaning it is a set of matrices of size  $m \times n$  over  $\mathbb{F}_q$  that are closed under addition and scalar multiplication.

A 'codeword' of a rank metric code is a matrix that is an element of the code. Codewords in a rank metric code can have different ranks.

A mapping, also called an isometry, can be applied to a code  $\mathcal{C}$  to create a new code  $\mathcal{D}$ . An isometry is denoted by  $\phi$  and is defined in Definition 2.2.5.

# **Definition 2.2.5** (Isometry, following [41]).

An isometry  $\phi$  is a bijective transformation on  $\mathbb{F}_q^{m \times n}$ , defined by a pair of matrices  $(\mathbf{A}, \mathbf{B})$  where  $\mathbf{A} \in \mathrm{GL}_m(q)$  and  $\mathbf{B} \in \mathrm{GL}_n(q)$ , having the following form:

### $\mathbf{M}\mapsto \mathbf{A}\mathbf{M}\mathbf{B}$

$\phi$  can be applied to a code  $\mathcal{C}$  to obtain a new code  $\mathcal{D}$ :  $\phi(\mathcal{C}) = \mathcal{D}$ . For every codeword  $\mathbf{C}$  in  $\mathcal{C}$ , the matrix  $\mathbf{D} = \mathbf{ACB}$  is in  $\mathcal{D}$ . All codewords in  $\mathcal{D}$  can be obtained by applying  $\phi$  to the codewords in  $\mathcal{C}$ .

# Matrix Code Equivalence (MCE)

MEDS, just like many other (post-quantum) signature schemes, is based on an equivalence problem, which asks if there exists a mapping (isometry) between two mathematical objects that preserves certain properties. When given two objects, it is usually hard to find such a mapping, but it is easy to verify if a given mapping is correct. This is the underlying principle of the security of many cryptographic schemes.

In the case of MEDS, these mathematical objects are rank metric codes. Two rank metric codes  $\mathcal{C}$  and  $\mathcal{D}$  are called equivalent if there exists an isometry  $\phi$  with  $\phi(\mathcal{C}) = \mathcal{D}$ . The isometry should preserve the rank of the matrices in the code. This means that after applying  $\phi$ , the rank distance between any two matrices in  $\mathcal{C}$  should be the same as the rank distance between the corresponding matrices in  $\mathcal{D}$ .

The computational form of the MCE problem is shown in Definition 2.2.6.

**Definition 2.2.6** (Matrix Code Equivalence Problem, following [28]). Given two rank metric codes  $\mathcal{C}, \mathcal{D} \in \mathbb{F}_q^{m \times n}$ , find an isometry  $\phi$  on  $\mathbb{F}_q^{m \times n}$  such that  $\mathcal{C} = \phi(\mathcal{D})$  and  $\phi$  preserves the rank metric.

# 2.2.3 Sigma protocol and Fiat-Shamir transform

#### Sigma protocol

The MCE problem is used in MEDS to construct a 3-pass Sigma protocol [32]. A Sigma protocol ( $\Sigma$ -protocol) is a variant of a zero-knowledge proof, which is a protocol between a prover and a verifier where the prover convinces the verifier that it knows a piece of information without revealing the information itself. A slightly simplified definition of a Sigma protocol is given in Definition 2.2.7.

# **Definition 2.2.7** (Sigma Protocol, following [32]).

A Sigma protocol for a relation R over a pair (x, w) where x is a statement (an instance of some computational problem) and w is a witness (a solution to that instance) is a 3-pass protocol between a prover P and a verifier V consisting of the following steps:

- Commitment: The prover P generates a commitment a based on generated values of x and w and sends it to the verifier V.

- Challenge: The verifier V sends a random challenge e to the prover P.

- Response: The prover P sends a reply z based on the challenge e, the commitment a, and the information x and w. The verifier V can verify z based on a and e.

In the above definition, a prover P can cheat the verifier V with some probability by guessing the challenge e before sending the initial commitment.

In the case of MEDS, the prover convinces the verifier that it knows a certain isometry  $\phi$  that satisfies an instance of the MCE problem, without revealing the isometry itself. In the definition of the Sigma protocol, x is an instance of the MCE problem (two rank metric codes  $\mathcal{C}$  and  $\mathcal{D}$ ), and w is an isometry  $\phi$  (such that  $\phi(\mathcal{C}) = \mathcal{D}$ ). The Sigma protocol for the optimized version of MEDS is provided in [30, Section 4.2].

# Fiat-Shamir transform

To convert a Sigma protocol into a digital signature scheme, the Fiat-Shamir transform [38] is used. The initial Sigma protocol is interactive, meaning that the prover and verifier exchange messages, which is not suitable for a digital signature. The Fiat-Shamir transform converts the Sigma protocol such that the prover can show knowledge of the isometry while only sending a single message to the verifier, making it non-interactive. This is achieved by creating the challenge based on a collision-resistant hash of the message

to be signed and the commitment. The bits in the resulting digest are used as the challenge in the Sigma protocol.

When working with the Fiat-Shamir transform, various techniques and optimizations can be used to increase the security or lower the size of the public key and the signature. In the list below, we provide an overview of some of the techniques that are considered in the MEDS scheme. In addition to this list, Section 2.2.5 discusses more complex optimizations that are not listed here.

# • Multiple challenges:

Following the structure of a Sigma protocol used in MEDS, where a challenge is either 0 or 1, an attacker can impersonate an honest prover with  $\frac{1}{2}$  probability. This can be prevented by extracting not one, but t challenges from the bits in the digest that was created by the hash of the message and the commitment. This reduces the probability of impersonation to  $\frac{1}{2t}$ .

# • Multiple public keys:

As mentioned before, an attacker can impersonate an honest prover with  $\frac{1}{2}$  probability. To reduce this probability, the scheme can use multiple public keys, each of which is used to compute a different isometry. This increases the challenge space from 2 to s+1, reducing the probability of impersonation to  $\frac{1}{s+1}$  (s is the number of public keys used in the scheme).

# • Fixed-weight challenge strings:

A challenge is a number in the range [0, s]. If a challenge is 0, the response consists of matrices that are generated uniformly at random. In this case, it is sufficient to set the response to the seed that was used to generate the matrices, greatly reducing the size of the signature. By fixing a certain number w of challenges to 0, the average size of a response can be reduced. This technique has a slightly negative impact on the security of the scheme, but this can be compensated by increasing the number of challenges.

# • Seed tree:

If a scheme requires sending multiple seeds for the generation of matrices (or other objects), a seed tree can be used to reduce the size of the public key and the signature. This is a structure that allows the prover to transmit a smaller amount of bits than the size of the seeds, at the cost of an increased computational complexity.

By selecting t, s and w carefully and combining them with other parameters of the scheme, the security of the scheme can be increased to the desired level. Multiple combinations of parameters are used in MEDS to achieve various security levels [28]. The selection of these parameters has a big influence on

Table 2.1: Recommended MEDS parameter sets. **pk** and **sig** represent the size in bytes of the public key and the signature, respectively.

| Parameter Set | q    | n  | m  | k  | s | t   | w   | pk     | $_{ m sig}$ |

|---------------|------|----|----|----|---|-----|-----|--------|-------------|

| MEDS-21595    | 4093 | 26 | 25 | 25 | 2 | 144 | 48  | 21595  | 5200        |

| MEDS-55520    | 4093 | 35 | 34 | 34 | 2 | 208 | 75  | 55520  | 10906       |

| MEDS-122000   | 4093 | 45 | 44 | 44 | 2 | 272 | 103 | 122000 | 19068       |

the size of the public key and the signature, as well as the computational performance of the scheme.

#### 2.2.4 Parameter sets

The security of MEDS depends on the choice of a set of parameters. The parameters that are used in the MEDS scheme are the following:

- q: The size of the finite field  $\mathbb{F}_q$  over which all computations are done.

- n: The width and height of the private matrices  $A_i \in \mathbb{F}_q^{n \times n}$  that are used to generate the key pair.

- m: The width and height of the private matrices  $B_i \in \mathbb{F}_q^{m \times m}$  that are used to generate the key pair.

- k: The width and height of the private matrices  $T_i \in \mathbb{F}_q^{k \times k}$  that are used to generate the key pair.

- s: The number of different public keys that are used in the scheme.

- t: The number of challenges that are used in the Fiat-Shamir transform.

- w: The number of challenges in the Fiat-Shamir transform that are fixed to be 0.

The team behind MEDS has proposed three parameter sets for the new optimized version of the scheme [30]. These parameter sets are optimized for the three different security levels that are required in the NIST PQC competition. The parameter sets are shown in Table 2.1. The security level for each parameter set is shown in Table 2.2.

We can see that all parameter sets use the same finite field size q=4093. The dimensions of the matrices that are used increase with each security level, as well as the number of challenges t (and the number of fixed challenges w). The number of public keys s is always set to 2, meaning the scheme does not use the multiple public keys technique. Note that this differs from the original MEDS scheme [28], which used multiple public keys.

Table 2.2: MEDS security levels. **FS** denotes the claimed security of a MEDS parameter set in bits, following the currently best-known attack of [55].

| Parameter Set | NIST Category | FS      |

|---------------|---------------|---------|

| MEDS-21595    | Level 1       | 128.406 |

| MEDS-55520    | Level 3       | 192.058 |

| MEDS-122000   | Level 5       | 256.005 |

#### 2.2.5MEDS algorithms

In this section, we give an algorithmic overview of the three algorithms of MEDS: key generation, signature generation, and signature verification. The complete and detailed pseudocode of these algorithms is shown in Appendix A. Additionally, we provide some information on the matrix systemizer and isometry mapping derivation, two common functions used in the MEDS algorithms.

# **Key generation**

A simplified overview version of the MEDS key generation algorithm is shown in Algorithm 2.1. The full and detailed key generation algorithm for MEDS is shown in Algorithm A.1 (Appendix A).

# **Algorithm 2.1** MEDS key generation (overview)

- 1: **Input:** -

- 2: Output: public key pk, private key sk

- 3: Generate random matrix  $\mathbf{G}_0 \in \mathbb{F}_a^{k \times mn}$

- 4: **for**  $i \in \{1, \dots, s-1\}$  **do**

- Generate random invertible matrix  $\mathbf{T}_i \in \mathbb{F}_q^{k \times k}$

- 6:

- Compute  $\mathbf{G}_0' \in \mathbb{F}_q^{k \times mn} = \mathbf{T}_i \times \mathbf{G}_0$ Compute isometry  $(\mathbf{A}_i \in \mathbb{F}_q^{m \times m}, \mathbf{B}_i \in \mathbb{F}_q^{n \times n})$  from codewords in  $\mathbf{G}_0'$ 7:

- Compute  $\mathbf{G}_i \in \mathbb{F}_q^{k \times mn} = \pi_{\mathbf{A}_i, \mathbf{B}_i}(\mathbf{G}_0)$ 8:

- Convert  $G_i$  to systematic form

- 10: **return** pk =  $\mathbf{G}_0$ ,  $\mathbf{G}_i$ , sk =  $\mathbf{G}_0$ ,  $\mathbf{A}_i$ ,  $\mathbf{B}_i$ ,  $\mathbf{T}_i$  (for  $i \in \{1, \dots, s-1\}$ )

# Signature generation

A simplified overview version of the MEDS signature algorithm is shown in Algorithm 2.2. The full and detailed signature generation algorithm for MEDS is shown in Algorithm A.2 (Appendix A).

# Algorithm 2.2 MEDS signature generation (overview)

```

1: Input: private key sk, message m

2: Output: signature \sigma (contains the tag)

3: Parse \mathbf{G}_0 and \mathbf{T}_i from \mathbf{sk} for i \in \{1, \dots, s-1\}

4: for i \in \{0, \dots, t-1\} do

Generate random matrix \mathbf{M}_i \in \mathbb{F}_q^{2 \times k}

Compute \mathbf{C} \in \mathbb{F}_q^{2 \times mn} = \tilde{\mathbf{M}}_i \times \mathbf{G}_0

6:

Compute isometry (\mathbf{A} \in \mathbb{F}_q^{m \times m}, \mathbf{B} \in \mathbb{F}_q^{n \times n}) from codewords in \mathbf{C}

7:

Compute \tilde{\mathbf{G}}_i \in \mathbb{F}_q^{2 \times mn} = \pi_{\mathbf{A}, \mathbf{B}}(\mathbf{G}_0)

8:

Convert \tilde{\mathbf{G}}_i to systematic form

9:

10: Hash m and \tilde{\mathbf{G}}_i for i \in \{0, \dots, t-1\} to obtain d

Parse a set of hashes h_0, \ldots, h_{t-1} from d

for i \in \{0, ..., t-1\} do

if h_i > 0 then

13:

Compute \kappa_i \in \mathbb{F}_q^{2 \times k} = \tilde{\mathbf{M}}_i \times \mathbf{T}_h^{-1}

14:

15: return Signature \sigma = \kappa_0, \dots, \kappa_{t-1}, h_0, \dots, h_{t-1}, m

```

# Signature verification

A simplified overview version of the MEDS signature verification algorithm is shown in Algorithm 2.3. The full and detailed signature verification algorithm for MEDS is shown in Algorithm A.3 (Appendix A).

# Matrix systemizer

The matrix systemizer is responsible for converting a matrix  $A \in \mathbb{F}_{4093}^{m \times n}$  over the finite field  $\mathbb{F}_{4093}$  into a systematic form. In MEDS, the systematic form  $A' \in \mathbb{F}_{4093}^{m \times n}$  of a matrix  $A \in \mathbb{F}_{4093}^{m \times n}$  can take two forms:

#### • **REF**':

A' is in row-echelon form (REF) [77, Section 3.2], with the additional property that the leading coefficient of row i is in column i.

# • RREF':

A' is in reduced row-echelon form (RREF), with the additional property that the first  $m \times m$  submatrix of A' is the identity matrix.

The algorithm used in MEDS to systemize a matrix is a Gaussian elimination algorithm with some extra properties. The algorithm is implemented such that it runs in constant time, meaning that the execution time is the same for all matrices of equal size. Additionally, the algorithm contains three optional features that can be used (based on the input arguments):

•  $r_{\text{max}}$ : Set the number of rows of the input matrix that need to be systemized. If not specified, the entire matrix is systemized.

# Algorithm 2.3 MEDS signature verification (overview)

```

1: Input: public key pk, signature \sigma

2: Output: 1 if the signature is valid, 0 otherwise

3: Parse G_0 and G_i from pk for i \in \{1, ..., s-1\}

4: Parse \kappa_i, h_i, d and m from \sigma for i \in \{0, \dots, t-1\}

5: for i \in \{0, \dots, t-1\} do

if h_i > 0 then

6:

Compute \mathbf{G}_0' = \kappa_i \times \mathbf{G}_{h_i}

Cmpt. isometry (\mathbf{A} \in \mathbb{F}_q^{m \times m}, \mathbf{B} \in \mathbb{F}_q^{n \times n}) from codewords in \mathbf{G}_0'

7:

8:

9:

Re-generate matrix \tilde{\mathbf{M}}_i \in \mathbb{F}_q^{2 \times k} as in Algorithm 2.2

10:

Compute \mathbf{C} \in \mathbb{F}_q^{2 \times mn} = \tilde{\mathbf{M}}_i \times \mathbf{G}_0

Compute isometry (\mathbf{A} \in \mathbb{F}_q^{m \times m}, \mathbf{B} \in \mathbb{F}_q^{n \times n}) from codewords in \mathbf{C}

11:

12:

Compute \hat{\mathbf{G}}_i \in \mathbb{F}_q^{2 \times mn} = \pi_{\mathbf{A}, \mathbf{B}}(\mathbf{G}_0)

13:

Convert \hat{\mathbf{G}}_i to systematic form

14:

15: Hash m and \hat{\mathbf{G}}_i for i \in \{0, \dots, t-1\} to obtain d'

16: return 1 if d = d', 0 otherwise

```

- do\_swap: Allow the algorithm to swap columns of the matrix to ensure that the leading coefficient of a row is not 0.

- do\_backsub: Whether or not to perform back substitution after the matrix has been systemized into REF'/RREF' form.

The complete algorithm is depicted in Algorithm A.7 (Appendix A.3).

# Deriving isometry mappings

For more information on the isometry derivation process, we refer the reader to [30, Section 4.2], where the authors provide a detailed explanation of the technique.

In key generation, signing, and verification, as a result of an optimization technique that is applied to reduce the signature size [30], MEDS requires the derivation of an isometry mapping  $\phi = (\mathbf{A} \in \mathbb{F}_q^{m \times m}, \mathbf{B} \in \mathbb{F}_q^{n \times n})$ . This isometry mapping maps two full-rank, linearly independent codewords  $\tilde{\mathbf{C}}_1, \tilde{\mathbf{C}}_2 \in \mathbb{F}_q^{1 \times mn}$  that are stored in a matrix  $\mathbf{C} \in \mathbb{F}_q^{2 \times mn}$  to two matrices  $\mathbf{D}_0, \mathbf{D}_1 \in \mathbb{F}_q^{m \times n}$ . The deriving of this isometry is done by constructing a linear system of 2mn equations and  $m^2 + n^2$  variables formed by:

$$\mathbf{A} \times \mathbf{C}_0 = \mathbf{D}_0 \times \mathbf{B}^{-1}$$

$$\mathbf{A} \times \mathbf{C}_1 = \mathbf{D}_1 \times \mathbf{B}^{-1}$$

The resulting system of linear equations can be solved using a simple Gaussian elimination algorithm. However, because of the large size of the linear system,

this would result in a complexity of  $\mathcal{O}(2mn\cdot(m^2+n^2)^2) = \mathcal{O}(n^6)$  (as n=m+1 for the parameter sets that we consider) which is very inefficient.

Luckily, there is a better alternative. As the values of  $\mathbf{D}_0$  and  $\mathbf{D}_1$  can be public information or random matrices, we have the freedom to choose them. By setting  $\mathbf{D}_0 = (\mathbf{I}_m \mid 0) \in \mathbb{F}_q^{m \times n}$  and  $\mathbf{D}_1 = (0 \mid \mathbf{I}_n) \in \mathbb{F}_q^{m \times n}$ , we obtain a much more sparse and structured linear system which can be solved with an algorithm that has a complexity of  $\mathcal{O}(n^3)$ .

This is precisely what the solve\_opt function in the MEDS reference implementation is responsible for. Its input is a matrix  $\mathbf{C} \in \mathbb{F}_q^{2 \times mn}$  that represents the two codewords. It then constructs the sparse linear system of equations mentioned above and solves it in  $\mathcal{O}(n^3)$  time. The output of the function are the matrices  $\mathbf{A}$  and  $\mathbf{B}$  that represent the isometry mapping. The code for this function is rather long and is therefore omitted, but can be found in the code repository of this thesis.

# 2.3 ARMv8, Cortex-A72, and NEON

In this thesis, we focus on optimizing the MEDS implementation for the ARMv8 CPU architecture [52]. ARMv8 supports a wide range of instruction sets and extensions, of which the following are relevant to this thesis:

- **A64**: The default 64-bit instruction set for ARMv8.

- **NEON** (Advanced SIMD): The NEON instruction set is an extension to the ARMv8 architecture that is mandatory in all ARMv8 implementations. It allows for SIMD operations on 128-bit registers (see Section 2.3.1).

- **Crypto**: The cryptographic extension to the ARMv8 architecture. This is a non-mandatory extension that supports hardware support for various cryptographic algorithms.

# 2.3.1 Vectorization and SIMD

Single Instruction, Multiple Data (SIMD) is a type of instruction that operates on multiple pieces of data (vectors) in parallel. Using this technique, it is possible to execute a single operation (such as an addition or multiplication) on a vector of multiple numbers in a timeframe that is similar to the conventional operation on a single number. This can greatly improve the performance of algorithms that lend themselves to vectorization.

https://github.com/MeItsLars/MEDS-ARMv8-optimization-thesis/blob/main/re f/src/util.c

Table 2.3: Possible ARMv8 NEON lane sizes and their assembly instruction suffixes.

| Lane Count | Lane Width | ASM Suffix |

|------------|------------|------------|

| 2          | 64 bits    | .2d        |

| 1          | 64 bits    | .1d        |

| 4          | 32 bits    | .4s        |

| 2          | 32 bits    | .2s        |

| 8          | 16 bits    | .8h        |

| 4          | 16 bits    | .4h        |

| 16         | 8 bits     | .16b       |

| 8          | 8 bits     | .8b        |

In ARM, the SIMD instruction set is called NEON or Advanced SIMD (both terms refer to the same instruction set). NEON is a 128-bit SIMD architecture extension that is required in all standard ARMv8 implementations [6]. The NEON unit contains 32 128-bit registers, each of which can be used to store a vector of values. Each NEON register can be split into several different lanes. The lane sizes that are supported in NEON, together with their assembly (ASM) code suffixes, are shown in Table 2.3.

In assembly code, we can refer to a NEON register by using the register prefix v0-v31 followed by a suffix that indicates the lane size. For example, v0.4s refers to a 128-bit NEON register that contains 4 lanes of 32 bits each and can therefore store 4 32-bit values.

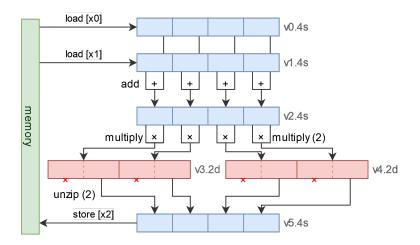

The NEON instruction set contains a wide range of instructions that can be used to perform various operations on these vectors. Some illustrative examples are included in Algorithm 2.4. A graphical depiction of the instructions in the code snippet above is shown in Figure 2.1.

In the remainder of this thesis, we use such NEON instructions in two forms:

- Assembly: Directly writing assembly code that uses NEON instructions, such as the add v2.4s, v0.4s, v1.4s instruction that adds two 4-lane vectors of 32-bit values.

- C intrinsics: Using C intrinsics, which are functions that map directly to NEON instructions. ARM provides a set of intrinsics that can be used when including the arm\_neon.h header file [9].<sup>2</sup> An example is the vadd\_u16(uint16x4\_t a, uint16x4\_t b) intrinsic, which adds two 4-lane vectors of 16-bit unsigned integers.

<sup>&</sup>lt;sup>2</sup>https://developer.arm.com/architectures/instruction-sets/intrinsics/#f:@navigationhierarchiessimdisa=[Neon]&f:@navigationhierarchiesarchitectures=

[A64]

# Algorithm 2.4 NEON instruction example (assembly)

Figure 2.1: Visual representation of the NEON registers and instructions in Algorithm 2.4.

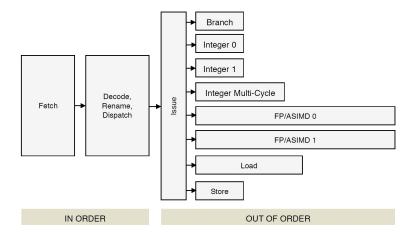

Figure 2.2: High-level overview of the ARM Cortex-A72 instruction processing pipeline [7].

#### 2.3.2 Cortex-A72 Micro-Architecture

For profiling (and benchmarking) our code, we use a Raspberry Pi 4 Model B, which has a 64-bit quad-core ARM Cortex-A72 CPU that uses the ARMv8-A architecture (which is a specific profile of ARMv8). The term 'Cortex-A72 Micro-Architecture' refers to the specific design of the ARM Cortex-A72 CPU, which differs from other CPUs that implement the ARMv8-A architecture.

We work with the A64 instruction set, combined with the NEON extension. Unfortunately, the Cortex-A72 does not support the Crypto extension, which means that we cannot use hardware acceleration for cryptographic operations such as SHA-3 [37].

In this thesis, we focus on optimizing the MEDS implementation for the Cortex-A72 CPU. However, we also provide benchmarks for the Apple M2 CPU, which runs on the ARMv8.6-A architecture and supports the Crypto extension.

# Core pipeline

The core pipeline of the Cortex-A72 consists of 15 stages which are split into a front-end and a back-end. A high-level overview of the instruction processing pipeline [7] is shown in Figure 2.2.

The pipeline consists of two parts:

1. **Front-end** (In Order): This part of the pipeline is responsible for fetching and decoding incoming instructions into micro-ops: smaller instructions that are easier to execute. These micro-ops are then

- fed into the back end. The front end works on instructions in order, meaning that it processes them in the order that they are received.

- 2. Back-end (Out of Order): This part of the pipeline is responsible for executing the micro-ops that are generated by the front end. It consists of multiple pipelines that serve different purposes, such as branching, integer arithmetic, NEON operations, and memory operations. The back-end pipelines can execute micro-ops out of order, meaning they can execute operations in a different order than they were received.

The front-end can work on 3 instructions at the same time and it can dispatch up to 5 micro-ops per cycle to the back-end [65]. The back-end pipelines can execute one or two micro-ops per cycle, depending on the specific pipeline. The main goal of the front end (and this structure in general) is to make sure that the back-end pipelines are always filled with micro-ops to minimize stalls (where a pipeline has to wait for an earlier operation to finish).

# Assembly instructions and latency

In this thesis, we use A64 assembly instructions to optimize the MEDS implementation. Each used instruction has three relevant properties:

- Execution latency: The number of CPU cycles after starting an instruction that it takes for the results of that instruction to be available for usage in the next instruction.

- Execution throughput: The maximum amount of times that a particular instruction can be executed per cycle.

- Utilized pipeline: The back-end pipeline(s) that this instruction uses.

As the Cortex-A72 uses an out-of-order execution model, it is impossible to provide instruction timing information that will predict how long a certain instruction will take to execute in a certain context [7]. Nevertheless, the execution latency and throughput of instructions provide valuable information about the performance of that instruction. Therefore, we list the execution latency and throughput of the NEON instructions that we use in the assembly code that was written for this thesis in Table 2.4. We also use many intrinsic functions in the C code, which are functions that map directly to assembly instructions. However, as the compiler is still able to reorder and optimize these instructions, it is not directly beneficial to know the latencies and throughputs of these instructions.

Table 2.4: ARM Cortex-A72 latency and throughput for the NEON assembly instructions used in this thesis [7].

| Instruction | Description                        | Latency | Throughput |

|-------------|------------------------------------|---------|------------|

| ld1         | Load from memory                   | 5       | 1          |

| st1         | Store to memory                    | 5       | 1          |

| umull       | Unsigned multiply long             | 4       | 1          |

| umull2      | Unsigned multiply long (high half) | 4       | 1          |

| umlal       | Uns. mult. long & accumulate       | 4       | 1          |

| mls         | Multiply subtract                  | 5       | 1/2        |

| add         | Add                                | 3       | 2          |

| sub         | Subtract                           | 3       | 2          |

| and         | Bitwise AND                        | 3       | 2          |

| ushr        | Unsigned shift right               | 3       | 1          |

| dup         | Store in all lanes                 | 8       | 1          |

| ins         | Store in one lane                  | 3       | 2          |

| xtn         | Extract and narrow                 | 3       | 2          |

| uzp1        | Unzip (keep low)                   | 3       | 2          |

| uzp2        | Unzip (keep high)                  | 3       | 2          |

| cmeq        | Compare equal                      | 3       | 2          |

| cmhs        | Compare higher or same             | 3       | 2          |

# Instruction scheduling

At first glance, it might seem that the order in which instructions of a certain instruction sequence are written in the assembly/intrinsic code influences the performance of the code, as the latencies and throughputs of the various instructions can influence the execution time of the code. This is the case for earlier ARM architectures, where hand-tuning of the instruction order could lead to performance improvements. However, the technical reference manual of the Cortex-A72 states that the out-of-order pipeline of the CPU can schedule and execute the instructions of a certain instruction sequence in an optimal fashion without any instruction reordering required [8]. This means that the CPU can 'hide' the latencies of instructions (by executing other micro-ops in the meantime). Although it is debatable whether this is always the case and whether there are no instruction sequences that the CPU is not able to schedule optimally, it is a good indication that we can focus on writing clean and readable code without having to worry about the order of the instructions.

It is important to note that this does not mean that there are no benefits to knowing the latencies and throughputs of instructions. Choosing a different sequence of instructions to compute the same result can still have an impact on the performance of the code because some instructions might be better suited for that specific computation.

# 2.4 Optimizing cryptographic schemes

When programming or optimizing cryptographic schemes or primitives, it is essential that the security of the scheme is not compromised because of vulnerabilities that are introduced in the code. One of the most important aspects in this context is the notion of constant-time execution [48]. A cryptographic function is said to be executed in constant-time if there exist no side-channel attacks that can extract secret information (such as a private key) by looking at the execution time of the function or any sub-sequence of the instructions in the function. In this section, we go over the main pitfalls that can lead to non-constant-time execution.

# 2.4.1 Branching and conditional execution

One of the most common reasons for non-constant-time execution occurs when the code contains branches that depend on secret data, allowing an attacker to perform a timing attack. A timing attack is a side-channel attack where an attacker measures the time that it takes to execute a certain piece of code and uses this measurement to derive information about the secret data that is used in the code. Consider the example in Algorithm 2.5.

# Algorithm 2.5 Branching on secret data (unsafe)

The execution time of this code snippet depends on the value of 'secret\_data'. If 'secret\_data' is 0, the execution time will be longer than when 'secret\_data' is not 0, allowing an attacker to derive information about the value of 'secret\_data' by measuring the execution time of the code.

Another example of branching on secret data occurs when the code uses a loop in which the execution time depends on secret data. Consider the example in Algorithm 2.6.

# **Algorithm 2.6** Looping on secret data (unsafe)

- 1: for i = 0 to secret\_data do

- 2: DOSOMETHING()

The execution time of this code snippet depends on the value of 'secret\_data'.

# Compiler optimizations and branch prediction

The previous examples are relatively obvious, but there are many more subtle ways in which branching on secret data can occur, especially when working with a smart compiler that tries to optimize the code. Consider the following example in Algorithm 2.7.

# Algorithm 2.7 Conditional swap (unsafe)

```

1: function CONDITIONALSWAP(x, y, \text{secret\_data})

2: if secret_data = 1 then

3: x, y \leftarrow y, x

4: else

5: x, y \leftarrow x, y

6: return x, y

```

Although it might seem that this function is safe, nearly all compilers will optimize this code such that the assignment in the 'else' branch is removed, making a timing attack possible.

Even if you can guarantee that the compiler does not optimize this code, the 'branch prediction' feature in modern CPUs might still make a timing attack possible. Branch prediction is a technique that tries to predict the outcome of a branch instruction before it is executed, allowing a CPU to start executing the instructions within the predicted branch. If the prediction is correct, the code will execute faster, but if the prediction is incorrect, the CPU will need to discard the results and start executing the correct branch, causing a delay. If an attacker knows how the CPU will predict the branch, they can use this information to perform a timing attack.

# Mitigating timing attacks

The most important technique to mitigate timing attacks on conditional execution is to never branch on secret data at all, not even if it seems safe. Most common operations can be rewritten in a way that removes conditional execution. For example, the conditional swap operation in Algorithm 2.7 can be rewritten as shown in Algorithm 2.8.

# Algorithm 2.8 Conditional swap (safe)

```

1: function CONDITIONALSWAP(x, y, \text{secret\_data})

2: d \leftarrow (x \oplus y) \cdot \text{secret\_data} \Rightarrow '\oplus' is the XOR operation

3: x \leftarrow x \oplus d

4: y \leftarrow y \oplus d

```

In this code snippet, if 'secret\_data' is 1,  $x = x \oplus (x \oplus y) = y$ . Otherwise,  $x = x \oplus 0 = x$ . This way, the code does not branch (on secret data) and is

therefore safe from timing attacks, assuming the compiler does not optimize the code in such a way that the branch is reintroduced.

# 2.4.2 Data-dependent memory access

Another common cause for non-constant-time execution is caused by accessing memory at an index that depends on secret data. Consider the example in Algorithm 2.9.

# Algorithm 2.9 Data-dependent memory access (unsafe)

1:  $x \leftarrow \text{public\_array[secret\_data]}$

This code is susceptible to a 'cache-timing attack'. A cache-timing attack is a side-channel attack where an attacker measures the time that it takes to access a certain memory location [19, 48]. If the data at that location is stored in the CPU cache, the access time will be faster than if the data is not (yet) in the cache. By measuring the time that it takes to access a certain memory location, an attacker can infer information about the value of 'secret\_data'.

This is only the most basic form of a cache-timing attack. More advanced attacks can be performed if the attacker has more control over the system, such as the ability to manipulate the cache to ensure that the data is (or is not) in the cache. Although there exist techniques to mitigate these attacks (such as always accessing every index of the array), it is best to avoid accessing memory at an index that depends on secret data altogether.

#### 2.4.3 Non-constant-time operations

A final common cause for non-constant-time execution is the use of CPU instructions that do not execute in constant time. Common examples of such instructions are (integer) division, math functions such as sin/cos, and various other instructions, depending on the CPU architecture. Instructions like these can take a variable amount of time to execute, depending on the input data. It is important to avoid using such instructions with secret data.

# 2.4.4 Preventing timing attacks with Valgrind and Timecop

It has been shown that even if you write code that should theoretically compile to a constant-time binary, the compiler might still optimize the code in such a way that it is vulnerable to various kinds of timing attacks [16, 71]. Therefore, it is good practice to make sure the resulting binary is indeed constant-time.

Vulnerabilities to timing attacks described in Section 2.4.1 and Section 2.4.2 can be detected using Valgrind [56] using a technique that was described

by Langley [51]. Valgrind is a programming tool that is used to detect memory leaks, buffer overflows, and other memory-related problems. Among many other things, Valgrind can detect branching on uninitialized data and memory accessing at an uninitialized index. Valgrind is unable to detect timing attack vulnerabilities caused by non-constant-time operations such as mentioned in Section 2.4.3. Using the following routine, we can use Valgrind to detect timing attack vulnerabilities:

- 1. **Uninitialized secret data**: Make sure our code does not initialize any secret data. Normal operations (such as arithmetic operations) on uninitialized data are ignored by Valgrind.

- 2. Run Valgrind: Run Valgrind on our code. Any resulting complaints about uninitialized data are possible locations at which a vulnerability to a timing attack might exist.

Timecop [76] provides a poison.h header file that can be used to poison secret data, which essentially makes it uninitialized. This can be used in combination with Valgrind to detect timing attack vulnerabilities.

# 2.5 Modular reduction

As MEDS is a cryptographic scheme that operates on elements in a finite field, modular reduction is a basic building block that is used in many parts of the scheme. Various algorithms can be used to perform modular reduction. In this section, we go over the most common algorithms.

#### • Naive reduction

The naive reduction algorithm is slow and not suitable for our purposes, but we use it as a baseline to compare the other algorithms to. This algorithm works by applying an integer division instruction to the input, followed by a multiplication with the modulus and a subtraction. A big disadvantage of this approach is that division is not a constant time operation, which can lead to timing attacks (see Section 2.4.3). Furthermore, the division operation is usually relatively slow compared to other operations.

# • Montgomery reduction

Montgomery reduction [54] is a modular reduction algorithm that is based on the Montgomery multiplication algorithm. It does not use a division instruction, which makes it suitable for constant time operations. Instead, it works by subtracting a multiple of the modulus from the input such that the input is (almost) smaller than the modulus. The algorithm requires the input and outputs to be converted to and from a Montgomery representation.

#### • Barrett reduction

Barrett reduction [15] is a modular reduction algorithm that is similar to Montgomery reduction in the sense that it also subtracts a multiple of the modulus from the input. However, it does not require the input to be converted to a different representation. Additionally, the cost of the reduction is slightly lower for small inputs compared to Montgomery reduction.

Montgomery reduction is generally very efficient when a large chain of multiplications is required and the overhead of converting to and from Montgomery representation is negligible compared to the number of multiplications/reductions, whereas Barrett reduction is typically a bit faster for small inputs.

#### 2.5.1 Barrett reduction

Barrett reduction works by approximating the modular reduction. Given an unsigned integer a and a modulus n,

$$a \mod n = a - \left\lfloor \frac{a}{n} \right\rfloor \cdot n.$$

From this, the Barrett reduction formula for unsigned integers can be derived (Definition 2.5.1).

**Definition 2.5.1** (Barrett reduction for unsigned integers).

Let a be an unsigned integer and n be a modulus. Let R be a constant such that  $R = 2^k > n$  for some k. Then:

$$a \bmod n = a - \left| \frac{a \cdot \left[ \frac{R}{n} \right]}{R} \right| \cdot n.$$

where  $\left[\frac{R}{n}\right]$  represents  $\frac{R}{n}$  rounded up or down, depending on the choice of the rounding operation.

As R is a power of 2, the division by R can be implemented as a cheap right-shift operation. Additionally, the value of  $m = \left[\frac{R}{n}\right]$  can be precomputed because the modulus n is a constant. This leaves us with two things to choose: the value of k and the rounding operation.

#### Choice of k

Usually, the value of k chosen for Barrett reduction is as small as possible such that  $2^k > n$ . Combined with setting the rounding function of the precomputed value to the 'floor' function, this results in a reduction that reduces to a value between 0 and 2n - 1, requiring an additional conditional

subtraction at the end of the reduction. Choosing a larger value of k has one major disadvantage: the precomputed value  $m = \left \lceil \frac{R}{n} \right \rceil$  becomes larger, which means that the multiplication  $a \cdot m$  will result in a larger value (possibly leading to a register overflow). However, choosing a larger value of k can also be beneficial: the quotient m will be closer to the actual value of  $\frac{R}{n}$ , which means that the reduction will be more accurate. If we know that the input a will never be larger than a particular value, we can choose k such that the conditional subtraction at the end of the reduction is not required. For this to work, we need to use the ceiling function for the rounding operation.

# Chapter 3

# **Profiling**

In this chapter, we discuss and execute the profiling of the optimized MEDS implementation from [30], with the goal of identifying the code sections that take up the most time. We use this information to optimize the code in the next chapter.

# 3.1 Profiling techniques

To obtain a better understanding of the performance of (specific functions of) MEDS, we need to profile the implementation. Profiling is the process of measuring the space or time complexity of a program or a specific function. The goal of profiling is to identify the bottlenecks in the speed or memory usage of a program: these are the parts of the program that take the most time or memory. Usually, we hope that a small part of the program is responsible for a large part of the time or memory usage and that this part can be optimized to improve the overall performance.

Typically, profiling is done by running the program with a profiler. There exist a wide variety of profilers for C, such as GProf [43], Valgrind [56], and Linux-Perf [33]. In our case, the most accurate way to measure the performance is to measure the number of cycles that are used by the program or a specific function, which can be done with Linux-Perf.

# 3.1.1 Cycle counting

Cycle counting is a technique that is used to measure the number of CPU cycles that it takes to execute a certain program or function. This is usually done by accessing the performance monitoring unit (PMU) of the CPU, which is a CPU component that measures the performance of the processor. Typically, these PMUs contain a register that can be read to obtain the

number of cycles executed since a certain point in time. On Linux, we can access this data using the Linux-Perf tool [33], which can be used to measure the number of instructions executed, the number of cache misses, etc.

# Advantages

The advantages of profiling the code using a cycle counter are:

- Accurate: Measuring the cycle counter results in the most accurate measurement of time. For comparison, using a technique that measures the current time in (nano)seconds is less accurate, because the CPU is capable of executing multiple cycles in a single nanosecond.

- Low overhead: Measuring the cycle counter has a very low additional performance overhead to the program, as it usually consists of reading a single register.

- **Precise**: By annotating the code with our own cycle counter, we can measure the performance of specific functions or even specific lines of code.

# Disadvantages

The disadvantages of profiling the code using a cycle counter are:

- Interference: The program to be measured shares the CPU (core) with other programs, which can interfere with measurements. If another program is switched in by the operating system, the cycle counter will also count the cycles that were used by this program. Although this usually does not have a big impact on profiling results, this can be problematic for obtaining accurate benchmarks.

- Architecture: The way in which the cycle counter is accessed is different for each architecture. However, since we use the Linux-Perf tool, this is abstracted away for us.

#### Problem mitigation

There are a few problems with cycle counting that we need to mitigate. First of all, there are some features on modern CPUs that will cause cycle counting to produce inaccurate results. These features include frequency scaling (based on the current workload, a CPU can change its clock frequency to save power) and hyperthreading (multiple threads share the same CPU core at the same time by interleaving instructions). It is essential to disable these features to obtain accurate results.

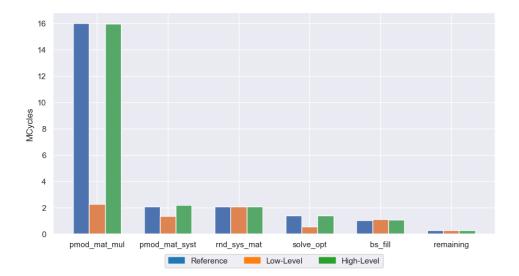

Table 3.1: MEDS-55520 key generation profiling results for the ARM Cortex-A72.

| Function                | # MCycles $(\pm)$ | % of Total $(\pm)$ | # Calls |

|-------------------------|-------------------|--------------------|---------|

| pmod_mat_mul            | 15.98             | 69.78              | 70      |

| ${\tt pmod\_mat\_syst}$ | 2.08              | 9.07               | 6       |

| ${\tt rnd\_sys\_mat}$   | 2.07              | 9.05               | 1       |

| ${\tt solve\_opt}$      | 1.42              | 6.20               | 1       |

| $bs\_fill$              | 1.06              | 4.63               | 1       |

| Cumulative              | 22.61             | 98.73              |         |

| Remaining               | 0.29              | 1.27               |         |

Another problem is program interference (see above). Unfortunately, this is a problem that is hard to prevent completely, but we can work around it. By running the program multiple times and taking the median of the results, we can reduce the impact of interference on the results. This is a common technique in benchmarking and is used in many other cryptographic papers [17, 36].

# 3.2 MEDS profiling results

# 3.2.1 Measurement setup

We added cycle count measurements to all MEDS functions that we anticipate will require a significant amount of time. We decided to profile the code for the MEDS-55520 parameter set, which is in the middle of the three parameter sets in terms of security level. The results are representative of the other parameter sets as well, only the scale is different. We executed measurements for the three algorithms of a digital signature scheme: key generation, signing, and verification, on the ARM Cortex-A72. The results are shown in Tables 3.1 (key generation), 3.2 (signing), and 3.3 (verification). For each algorithm, we list the functions or code sections that take up more than 1% of the total number of cycles. We provide the number of megacycles (MCycles) that were used in that function, the percentage of the total number of cycles that were used by that function, and the number of times that function was called. Note that the number of cycles cannot be divided by the number of calls to obtain the average number of cycles per call, because the number of cycles that are used by a function can depend on the input.

# 3.2.2 Result analysis

Because of the way that MEDS works, the results of the signing and verification operations are very similar. For key generation, the results in the table

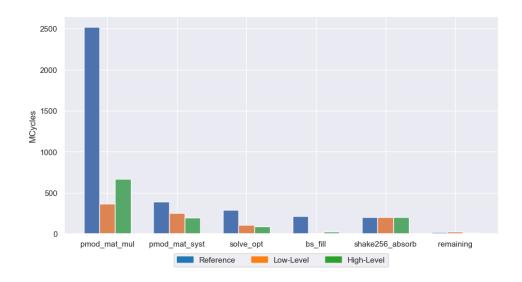

Table 3.2: MEDS-55520 signing profiling results for the ARM Cortex-A72.

| Function           | # MCycles $(\pm)$ | % of Total $(\pm)$ | # Calls |

|--------------------|-------------------|--------------------|---------|

| pmod_mat_mul       | 2518.85           | 69.17              | 14635   |

| $pmod\_mat\_syst$  | 391.36            | 10.75              | 1040    |

| ${\tt solve\_opt}$ | 293.44            | 8.06               | 208     |

| bs_fill            | 212.74            | 5.84               | 1       |

| shake256_absorb    | 203.06            | 5.58               | 212     |

| Cumulative         | 3619.46           | 99.39              |         |

| Remaining          | 22.24             | 0.61               |         |

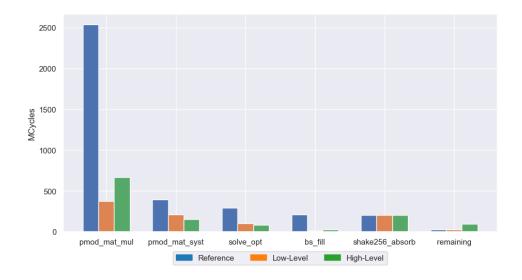

Table 3.3: MEDS-55520 verification profiling results for the ARM Cortex-A72.

| Function           | # MCycles $(\pm)$ | % of Total $(\pm)$ | # Calls |

|--------------------|-------------------|--------------------|---------|

| pmod_mat_mul       | 2537.20           | 69.24              | 14560   |

| $pmod\_mat\_syst$  | 393.22            | 10.73              | 1040    |

| ${\tt solve\_opt}$ | 294.20            | 8.03               | 208     |

| $bs\_fill$         | 212.88            | 5.81               | 1       |

| shake256_absorb    | 203.31            | 5.55               | 267     |

| Cumulative         | 3640.80           | 99.35              |         |

| Remaining          | 23.80             | 0.65               |         |

account for 98.76% of the total number of cycles. For signing and verification, these numbers are 99.42% and 99.39%, respectively. In all three algorithms, the remainder of the cycles is spent on a large set of functions that take up a small amount of time. Given that there are only a few functions that take up a significant amount of time, we can conclude that the performance of MEDS is mostly determined by these functions.

# Matrix multiplication

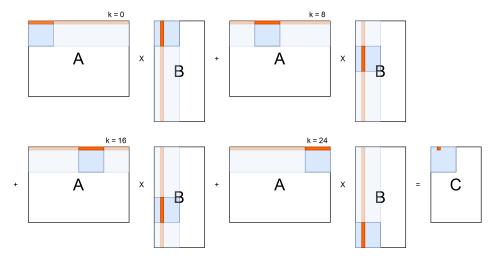

For all three operations, the pmod\_mat\_mul function takes up the most time, almost 70%. This function is used to multiply two matrices  $A \in \mathbb{F}_q^{m \times n}$  and  $B \in \mathbb{F}_q^{n \times o}$  over a finite field  $\mathbb{F}_q$ . The function is implemented in MEDS using a naive algorithm that computes the dot product of each row of A with each column of B, followed by a reduction modulo q. As will be shown in Section 4.2.1, the time complexity of this algorithm is  $\mathcal{O}(mno)$  (=  $\mathcal{O}(n^3)$  for square matrices).

### Matrix systemizer

The pmod\_mat\_syst function (pmod\_mat\_syst\_ct\_partial\_swap\_backsub in the code, but shortened for readability) is responsible for about 11% of the total number of cycles for signing and verification. This function is used to systemize a matrix  $A \in \mathbb{F}_q^{m \times n}$  over a finite field  $\mathbb{F}_q$  (see Section 2.2.5). This is done using a Gaussian elimination algorithm that has a complexity of  $\mathcal{O}(m^2n)$  (this is calculated in Section 4.2.2).

# Isometry derivation

The solve\_opt function is responsible for about 8% of the total number of cycles for signing and verification. This function derives an isometry mapping  $\phi = (\mathbf{A} \in \mathbb{F}_q^{m \times m}, \mathbf{B} \in \mathbb{F}_q^{n \times n})$  by constructing and solving a sparse system of linear equations, see Section 2.2.5. The algorithm has a complexity of  $\mathcal{O}(n^3)$ .

# Bitstream filling

The bs\_fill section is responsible for about 6% of the total number of cycles for signing and verification. In this section of the code, multiple calls are made to the bs\_init, bs\_write, and bs\_finalize. We decided to group them because they are all part of the same operation: filling a bitstream with elements of the finite field  $\mathbb{F}_q$ . In the MEDS parameter sets that we consider, the finite field is  $\mathbb{F}_{4093}$ , which means that the bitstream is filled with 12-bit elements. This is done to reduce the number of bytes required to store a list of field elements.

### SHAKE256

A small percentage of the total number of cycles in each of the three operations is used by either shake256\_squeeze or shake256\_absorb. SHAKE256 is an extendable output function (XOF). It is part of the SHA-3 family [37] and is based on the KECCAK sponge construction [23]. MEDS uses SHAKE256 to generate random field elements and to hash the challenge strings that are used in the Fiat-Shamir transform (see Section 2.2.3).

# Random systemized matrix generation