# Formal Verification of On-Chip Communication Fabrics

## PROEFSCHRIFT

ter verkrijging van de graad van doctor

aan de Radboud Universiteit Nijmegen,

op gezag van de Rector Magnificus prof. mr. S.C.J.J. Kortmann,

volgens besluit van het college van decanen

in het openbaar te verdedigen op

dinsdag 26 maart 2013 om 13:30 uur precies

door

Freek Verbeek

geboren op 17 september 1983

te Nijmegen

Promotoren:

prof. dr. F.W. Vaandrager

prof. dr. M.C.J.D. van Eekelen

Copromotor:

dr. J. Schmaltz

Samenstelling manuscriptcommissie:

prof. dr. H. Gevers

prof. dr. N. Bagherzadeh (University of California, Irvine, CA)

prof. dr. D. Borrione (University Joseph Fourier, FR)

prof. dr. A. Jantsch (KTH Royal Institute of Technology, SW)

dr. M. Kishinevsky (Intel Corporation, OR)

Cover: Pim Sebok

This research is supported by the Netherlands Organisation for Scientific Research (NWO) under the project Formal Validation of Deadlock Avoidance Mechanisms (FVDAM) under grant no. 612.064.811, and is supported by a grant from Intel Corporation.

ISBN 978-94-61083-91-3

---

# Dankwoord

---

Er zijn ontzettend veel mensen die de afgelopen vier jaar in meer of mindere mate aan de totstandkoming van dit proefschrift hebben bijgedragen. Ik wil deze mensen hiervoor bedanken en een aantal er hier uitleggen.

Mijn copromotor, Julien, is essentieel geweest bij iedere stap die ik de afgelopen vier jaar heb gezet. Vier jaar lang hebben we samen hard gewerkt, vele discussies gehad, geluncht, aan conferenties deelgenomen, universiteiten en bedrijven verspreid over Europa en de VS bezocht, nieuwe contacten gelegd en af en toe een biertje gedronken. Ook al kunnen we een diepgaand meningsverschil hebben over de opzet van een intro – en ook al moest ik vaak een paper tot treurens toe “meer structuur” geven – in die vier jaar is er nooit een frustratie ontstaan en heb ik de samenwerking altijd als bijzonder prettig ervaren. Ik ben blij dat we ook in de toekomst nog samen zullen werken. Merci.

Frits en Marko, mijn promotoren, wil ik bedanken voor het vertrouwen en de vrijheid die ik de afgelopen vier jaar heb genoten. Enerzijds hebben jullie me volledig mijn eigen gang laten gaan, maar tegelijkertijd waren jullie altijd betrokken en hebben jullie constructief, gedetailleerd en bovenal nuttige feedback gegeven op mijn proefschrift.

Many thanks go to my manuscript committee, who did not only take the considerable effort of reading and critiquing my thesis to the last detail, but also of traveling many miles to be present at my defense. Professor Borrione, professor Jantsch and dr. Kishinevsky, I hope the future will hold many more collaborations. Professor Geuvers, Herman, to you I am greatly indebted for supervising my master thesis, suggesting me as a PhD candidate to Frits, and finally for presiding at my defense. A special thanks to professor Bagherzadeh and Abdulaziz Alhussien, whose inspiring ideas have had a great influence on this thesis and whose generous hospitality has left a great impression upon me.

Er is een hele lijst aan collega’s om te bedanken, te veel om hier op te sommen. Mijn kamergenoten Bas, Faranak, Maarten, Martijn en Thomas hebben het promoveren af en toe stukken leuker gemaakt dan het eigenlijk is (de USB gestuurde rocket launcher heb ik altijd een goede investering gevonden). De mensen van MBSD, maar ook de rest van ICIS, wil ik bedanken voor de lunches, koffiepauzes, leesclubjes en borrels. Bas, Bernard en Tom, het was geweldig om met jullie samen te werken.

Het promoveren had ik hoogstwaarschijnlijk nog geen twee maanden volgehouden zonder alle vrienden om mij heen. Ik hoop dat iedereen zich realiseert dat ik ze hiervoor ontzettend dankbaar ben. In het bijzonder verdient Pim hier wat lovende woorden voor zijn prachtige design van de voorkant van dit proefschrift. Ik vind het fantastisch dat je niet alleen uitgebreid hebt geluisterd naar mijn uitleg over mijn promotie onderwerp, maar er ook nog genoeg van oppikte om een mooie deadlock in het ontwerp te verwerken.

Arthur en Fabian, paranimfen, het is voor mij een eer naast jullie te staan tijdens de verdediging [Mulders07]. En ook daarbuiten, natuurlijk.

Een promotietraject is nogal een aparte tijd. Een tijd vol onzekerheid over wat je moet doen en of dat gaat lukken, een tijd met veel deadlines en stress, een tijd waarin veel nieuwe en spannende ervaringen tegelijkertijd plaatsvinden. In zo'n tijd is de kennis dat er een constante factor is – namelijk dat er een plek is waar je altijd onvoorwaardelijk terecht kan – van onschabare waarde. Lia en Jos, ik kan jullie niet genoeg bedanken voor alles wat jullie hebben gedaan.

Nijmegen, januari 2013

---

# Contents

---

|                                                              |           |

|--------------------------------------------------------------|-----------|

| <b>I Preamble</b>                                            | <b>1</b>  |

| <b>1 Introduction</b>                                        | <b>3</b>  |

| 1.1 Formal Verification . . . . .                            | 6         |

| 1.2 Communication Networks . . . . .                         | 7         |

| 1.3 Network Layer Isolation versus Integration . . . . .     | 9         |

| 1.3.1 Example 1 . . . . .                                    | 10        |

| 1.3.2 Example 2 . . . . .                                    | 11        |

| 1.3.3 Isolated versus Integrated . . . . .                   | 12        |

| 1.4 Contribution of this Thesis . . . . .                    | 13        |

| 1.5 The Role of ACL2 in this Thesis . . . . .                | 15        |

| <b>2 Advances to the State-of-the-art</b>                    | <b>17</b> |

| 2.1 Communication Networks . . . . .                         | 17        |

| 2.2 Deadlocks in Communication Networks . . . . .            | 20        |

| 2.2.1 Necessary and Sufficient Conditions . . . . .          | 20        |

| 2.2.2 Determining Deadlock Freedom . . . . .                 | 22        |

| 2.3 Mechanical Verification of Interconnects . . . . .       | 23        |

| 2.3.1 ACL2 . . . . .                                         | 24        |

| 2.3.2 GeNoC . . . . .                                        | 26        |

| <b>II Proving Productivity of Communication Networks</b>     | <b>29</b> |

| <b>3 GeNoC for Productivity Proofs</b>                       | <b>31</b> |

| 3.1 Correctness of Communication Networks . . . . .          | 31        |

| 3.2 Generic Communication Network . . . . .                  | 33        |

| 3.2.1 Informal Overview . . . . .                            | 33        |

| 3.2.2 Formal Network Model . . . . .                         | 35        |

| 3.2.3 Generic Constituents . . . . .                         | 36        |

| 3.2.4 Deadlock Configuration . . . . .                       | 37        |

| 3.2.5 The Behavior of the Generic Network . . . . .          | 37        |

| 3.3 Functional Correctness . . . . .                         | 40        |

| 3.3.1 Definition of Functional Correctness . . . . .         | 40        |

| 3.3.2 Proof Obligations for Functional Correctness . . . . . | 40        |

## Contents

|                           |                                                                      |           |

|---------------------------|----------------------------------------------------------------------|-----------|

| 3.3.3                     | Functional Correctness Theorem                                       | 42        |

| 3.4                       | Evacuation                                                           | 42        |

| 3.4.1                     | Proof Obligations for Evacuation                                     | 43        |

| 3.4.2                     | Evacuation Theorem                                                   | 45        |

| 3.5                       | Local Liveness                                                       | 46        |

| 3.5.1                     | Proof Obligations for Local Liveness                                 | 47        |

| 3.5.2                     | Local Liveness Theorem                                               | 48        |

| 3.6                       | Productivity                                                         | 49        |

| <b>4</b>                  | <b>Application to HERMES</b>                                         | <b>53</b> |

| 4.1                       | HERMES                                                               | 53        |

| 4.2                       | User Input, Part I: Executable Specification                         | 54        |

| 4.3                       | User Input, Part II: Proofs                                          | 57        |

| 4.3.1                     | Discharging Proof Obligations                                        | 57        |

| 4.3.2                     | Deadlock Verification                                                | 62        |

| <b>5</b>                  | <b>Conclusion</b>                                                    | <b>63</b> |

| 5.1                       | Definition of Productivity                                           | 63        |

| 5.2                       | Productivity in Literature                                           | 65        |

| 5.3                       | The GeNoC Framework                                                  | 67        |

| <b>III</b>                | <b>Isolated Network Layer Deadlock Verification</b>                  | <b>69</b> |

| <b>6</b>                  | <b>Necessary and Sufficient Conditions for Deadlock-free Routing</b> | <b>71</b> |

| 6.1                       | Notation and Definitions                                             | 72        |

| <b>Packet Switching</b>   |                                                                      | 76        |

| 6.2                       | Formal Condition                                                     | 76        |

| 6.2.1                     | Our Condition                                                        | 76        |

| 6.2.2                     | Proof                                                                | 78        |

| 6.3                       | Definition of Deadlock                                               | 82        |

| 6.4                       | Relation to Duato                                                    | 85        |

| 6.4.1                     | Duato's Condition                                                    | 85        |

| 6.4.2                     | Relation to our Condition                                            | 85        |

| <b>Wormhole Switching</b> |                                                                      | 86        |

| 6.5                       | Formal Condition                                                     | 86        |

| 6.5.1                     | Our Condition                                                        | 87        |

| 6.5.2                     | Proof                                                                | 89        |

| 6.6                       | Definition of Deadlock                                               | 91        |

| 6.7                       | Relation to Duato                                                    | 92        |

| 6.7.1                     | Duato's Condition                                                    | 92        |

| 6.7.2                     | A Counterexample                                                     | 94        |

| 6.7.3                     | Relation to our Condition                                            | 96        |

| 6.8                       | Relation to Schwiebert and Jayasimha                                 | 98        |

| 6.8.1                     | Schwiebert and Jayasimha's Condition                                 | 98        |

| 6.8.2                     | Relation to our Condition                                            | 99        |

| 6.9                       | Relation to Taktak et al.                                            | 99        |

| 6.9.1                     | Taktak's Condition                                                   | 99        |

|           |                                                       |            |

|-----------|-------------------------------------------------------|------------|

| 6.9.2     | Relation to our Condition                             | 100        |

| 6.10      | Conclusion                                            | 101        |

| <b>7</b>  | <b>Deadlock Detection Algorithms</b>                  | <b>103</b> |

|           | <b>Packet Switching</b>                               | 103        |

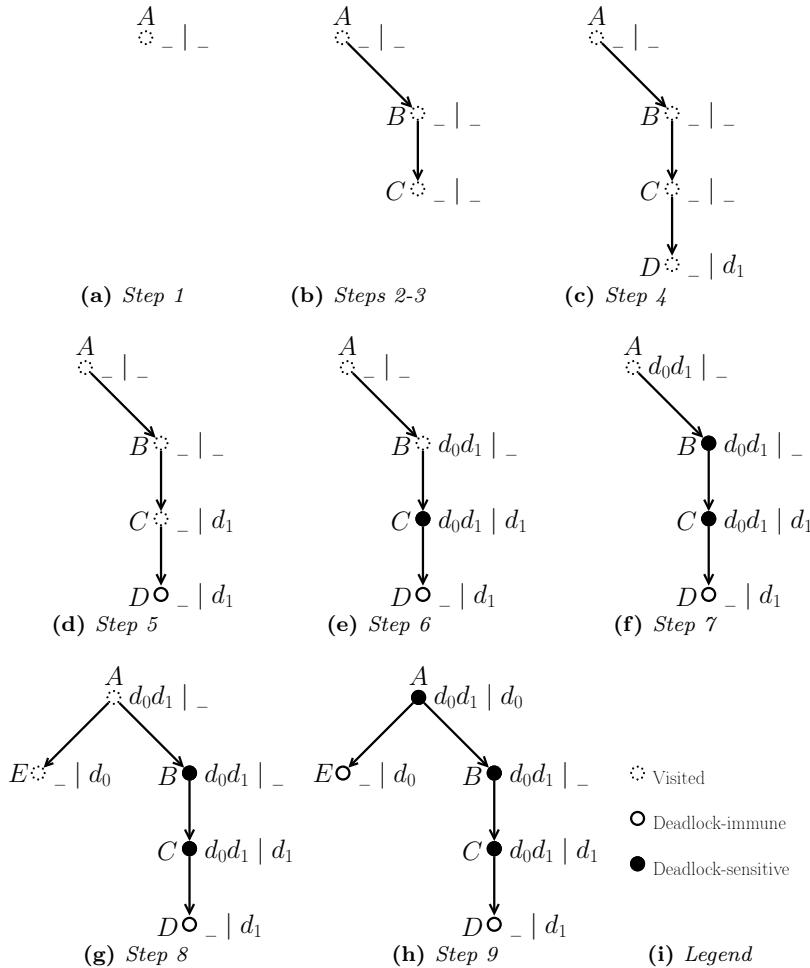

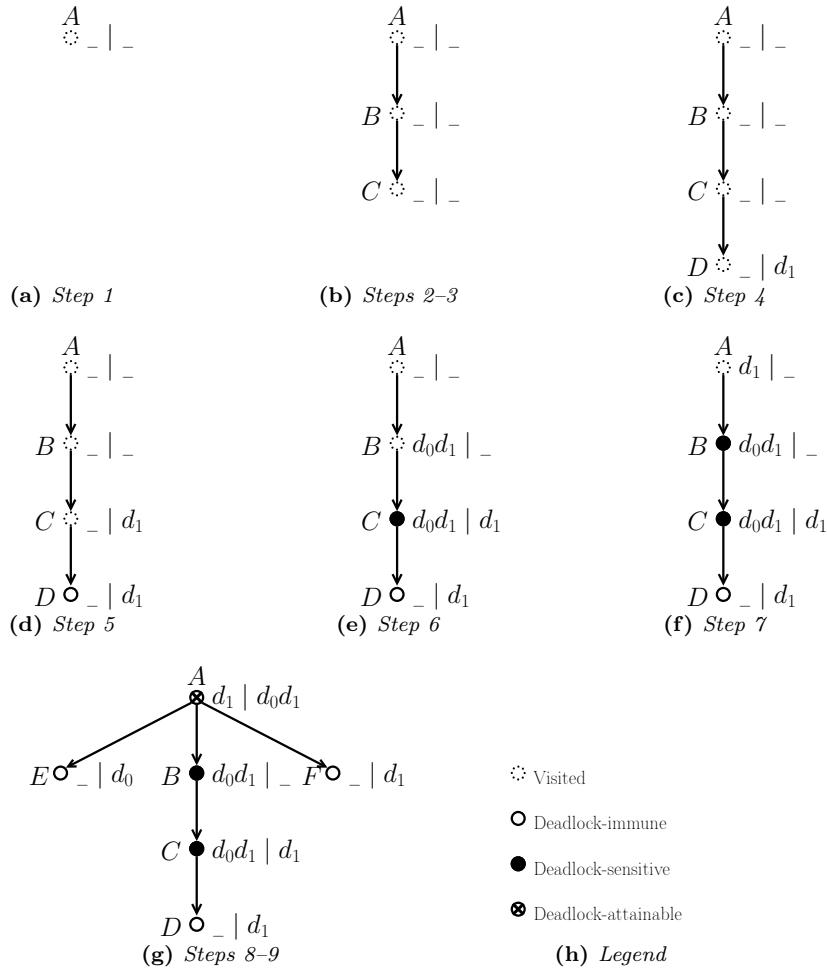

| 7.1       | Algorithm by Example                                  | 104        |

| 7.1.1     | Deadlock-immunity and -sensitivity                    | 104        |

| 7.1.2     | Example Trace                                         | 105        |

| 7.1.3     | Post-processing                                       | 107        |

| 7.2       | Pseudo Code                                           | 108        |

| 7.3       | Analysis                                              | 109        |

| 7.3.1     | Computational Complexity                              | 110        |

| 7.3.2     | Correctness                                           | 111        |

|           | <b>Wormhole Switching</b>                             | 113        |

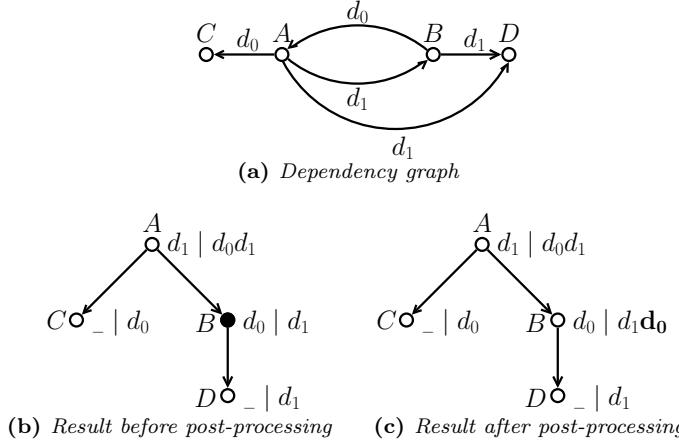

| 7.4       | Algorithm by Example                                  | 114        |

| 7.4.1     | Deadlock-attainability                                | 114        |

| 7.4.2     | Example Trace                                         | 115        |

| 7.5       | Pseudo Code                                           | 117        |

| 7.6       | Analysis                                              | 118        |

| 7.6.1     | Computational Complexity                              | 118        |

| 7.6.2     | Correctness                                           | 120        |

| 7.7       | Proof of co-NP-completeness                           | 122        |

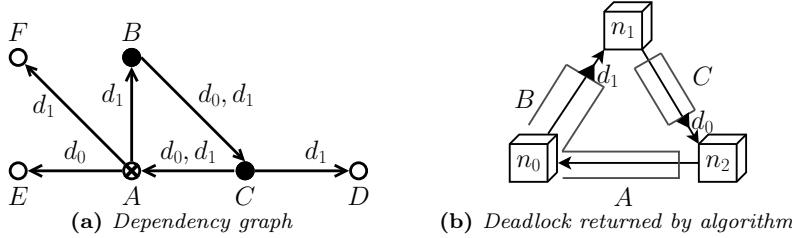

| 7.7.1     | Transformation Example                                | 123        |

| 7.7.2     | Formal Proof                                          | 125        |

| 7.7.3     | Deadlock Freedom versus Deadlock Prediction           | 128        |

| 7.8       | Related Work                                          | 129        |

| 7.9       | Conclusion                                            | 130        |

| <b>8</b>  | <b>Applications</b>                                   | <b>131</b> |

| 8.1       | DCI2                                                  | 131        |

| 8.2       | Benchmarks                                            | 132        |

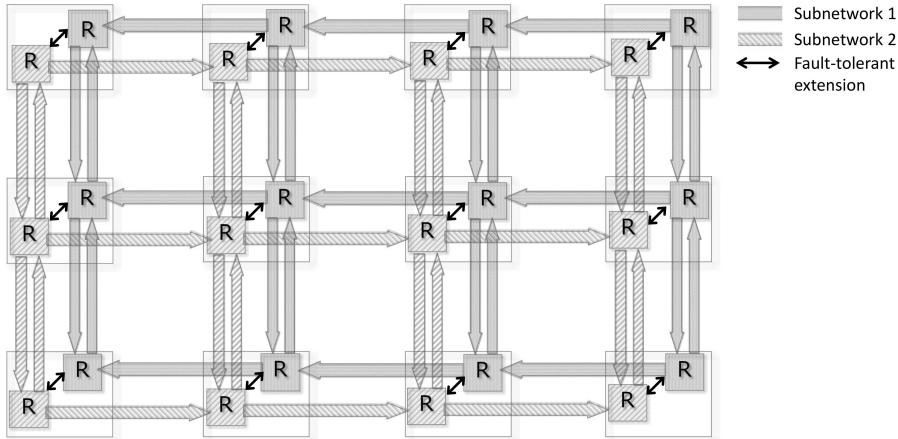

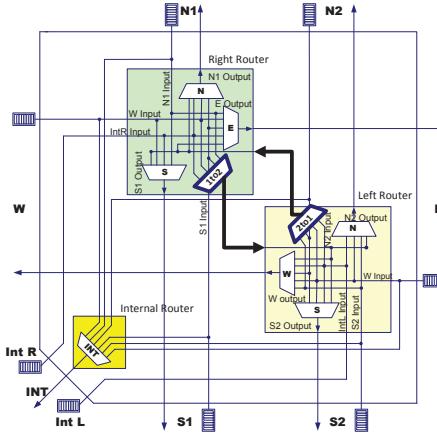

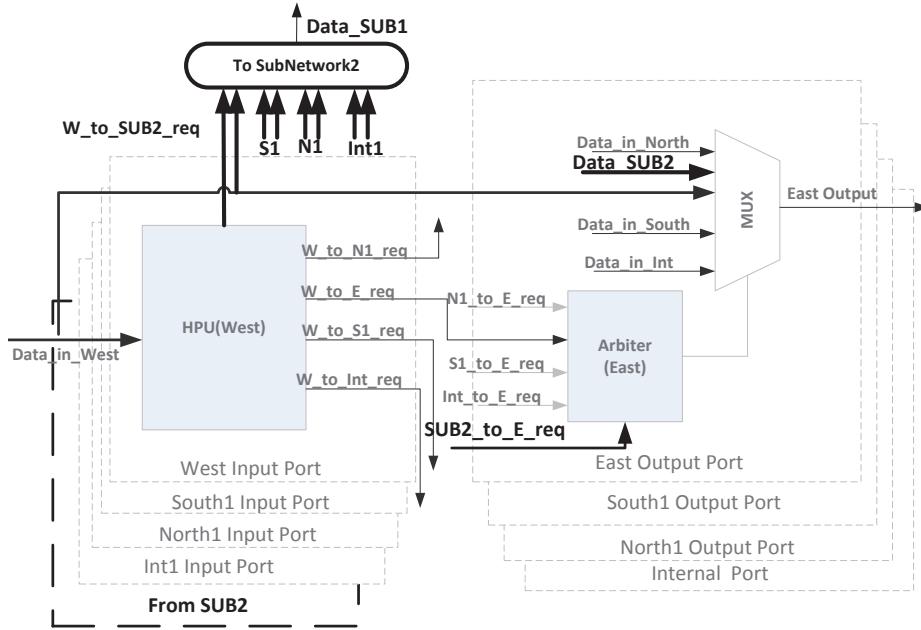

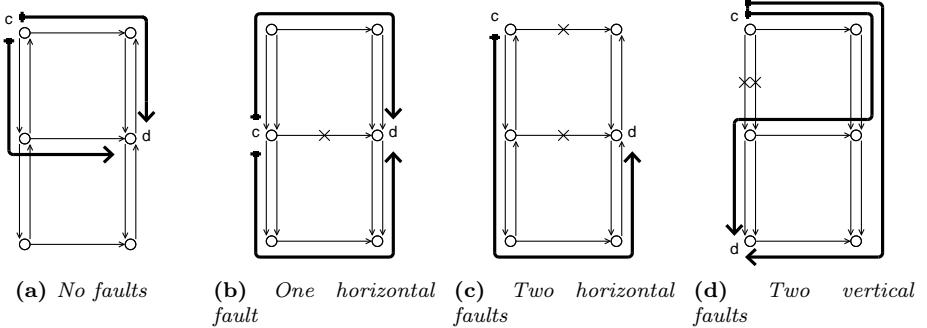

| 8.3       | NePA with Fault-tolerant Routing                      | 134        |

| 8.3.1     | Routing Logic                                         | 135        |

| 8.3.2     | Results                                               | 140        |

| 8.4       | NePA with Wireless Routers                            | 142        |

| 8.4.1     | Routing Logic                                         | 142        |

| 8.4.2     | Results                                               | 143        |

| 8.5       | Comparison to Taktak et al.                           | 144        |

| 8.6       | Conclusion                                            | 145        |

| <b>IV</b> | <b>Integrated Network Layer Deadlock Verification</b> | <b>147</b> |

| <b>9</b>  | <b>Microarchitectural Deadlock Verification</b>       | <b>149</b> |

| 9.1       | MaDLS                                                 | 150        |

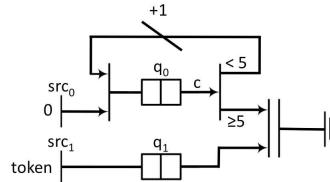

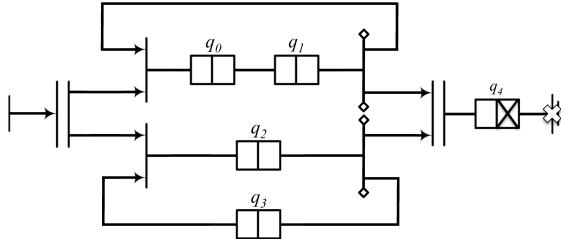

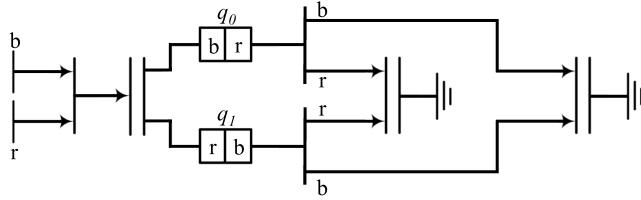

| 9.1.1     | xMAS: a MaDL for communication fabrics                | 150        |

| 9.1.2     | A Family of MaDLs                                     | 152        |

| 9.1.3     | Examples                                              | 153        |

## Contents

|                                      |                                                              |            |

|--------------------------------------|--------------------------------------------------------------|------------|

| 9.2                                  | Deadlock Detection Algorithm . . . . .                       | 155        |

| 9.2.1                                | Definition of Deadlock . . . . .                             | 156        |

| 9.2.2                                | Deadlock LIAPs . . . . .                                     | 157        |

| 9.2.3                                | Algorithm Paraphernalia . . . . .                            | 158        |

| 9.2.4                                | Deadlock Detection Algorithm . . . . .                       | 160        |

| 9.2.5                                | Restrictions . . . . .                                       | 163        |

| 9.3                                  | Correctness Proof . . . . .                                  | 165        |

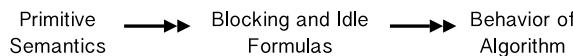

| 9.3.1                                | Automatic Generation of Blocking and Idle Formulas . . . . . | 165        |

| 9.3.2                                | Correctness Proofs of Translations . . . . .                 | 167        |

| 9.3.3                                | Correctness Proof of the Algorithm . . . . .                 | 171        |

| 9.4                                  | Experimental Results . . . . .                               | 173        |

| 9.5                                  | Conclusion . . . . .                                         | 174        |

| <b>Epilogue</b>                      |                                                              | <b>177</b> |

| Summary . . . . .                    |                                                              | 177        |

| Future Work . . . . .                |                                                              | 180        |

| <b>A Datastructures and Notation</b> |                                                              | <b>181</b> |

| A.1                                  | Sets . . . . .                                               | 181        |

| A.2                                  | Lists . . . . .                                              | 182        |

| A.3                                  | Tuples . . . . .                                             | 184        |

| A.4                                  | Graphs . . . . .                                             | 184        |

| <b>B List of Terms</b>               |                                                              | <b>187</b> |

| <b>Bibliography</b>                  |                                                              | <b>189</b> |

| <b>Samenvatting</b>                  |                                                              | <b>203</b> |

| <b>Curriculum Vitae</b>              |                                                              | <b>205</b> |

# Part I

## Preamble

---

# CHAPTER 1

## Introduction

---

As technology advances, microchips become more and more complex. To grasp the complexity of a future chip, consider the streets of a large city from an aerial view. Buildings – like black boxes – continuously inject and consume cars from the infrastructure, helicopters fly around and underneath it all a subway transports masses of people between fixed points. The integral behavior is dazzlingly complex and chaotic. Future microchips may well achieve a similar degree of complexity. On a single chip, hundreds of cores (the buildings) are performing parallel computations. A future on-chip infrastructure can integrate channels (the streets), wireless transmitters (the helicopters), or optical interconnects (the subways) on a few square centimeters. Even three-dimensional chips are feasible, essentially stacking several mutually connected cities upon each other.

The cause of all this on-chip complexity, is the ability of modern manufacturers to integrate huge amounts of transistors on a small surface. Currently, chips are built from transistors being only 22 nanometers long. Smaller transistors are expected (latest research has even developed a transistor consisting of only a single atom [57]) allowing more on-chip possibilities. It is up to both industry and academia to exploit this nano technology and to cope with the complexity inherent to running more than a billion transistors in one integrated circuit.

A general approach is to reduce the overall complexity by raising the level of abstraction of the design phase. Instead of building a chip from scratch, designers use prefabricated building blocks called intellectual properties or cores. A System-on-Chip (SoC) integrates different cores on one die. Examples of cores are processors, memory controllers, and video processing units. Cores are created, verified and tested individually, allowing a divide-and-conquer approach in designing complex microchips.

Essential to the performance of the chip is an efficient communication interconnect between these cores. Traditionally, a bus is used to facilitate all on-chip communications. The major drawback of a bus is scalability. It is possible to connect dozens of cores on one bus, but not hundreds. To deal with this issue, Networks-on-Chip (NoC) have been proposed [8]. In an on-chip network, several cores communicate with each other by transmitting messages which move through the interconnect until they arrive at their destination. An NoC is a “city on chip” with packets of data as its inhabitants.

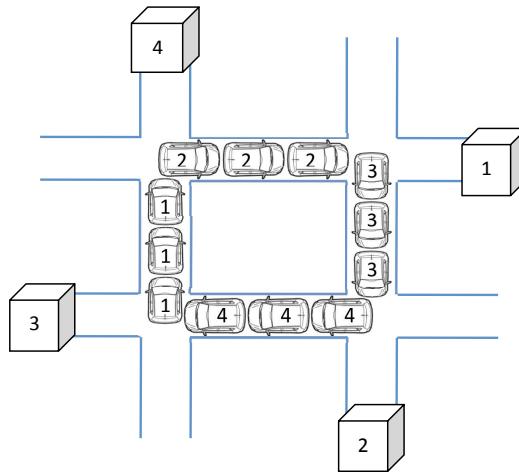

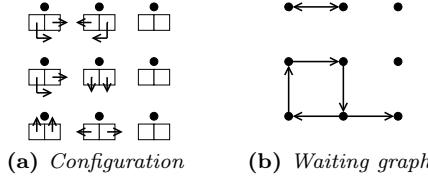

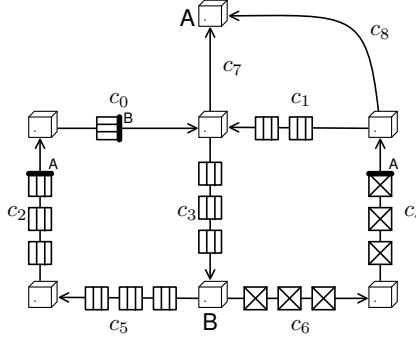

The NoC paradigm introduces new challenges to the world of SoC designers. In a chip with a bus, it is relatively easy to ensure that a message sent from one core to another will always eventually arrive. In an on-chip network this becomes more troublesome. In the interconnect of an NoC scenarios may occur in which messages never arrive at their destination. A deadlock is such a situation. Figure 1.1 shows an example. The cubes represent cores that make use of an on-chip interconnect to transmit and receive messages. The on-chip infrastructure is depicted as a set of streets, and the messages moving through this interconnect are depicted as cars. Each message has a destination, and it knows which direction to take to get towards its destination. However, each message is waiting for another message. All messages are waiting permanently.

A deadlock is not the only scenario in which messages never arrive at their destination. Various network-related issues can occur such as misrouting, livelocks, and starvation. None of these issues may occur, if a network is to be called *correct*.

**Figure 1.1: Deadlock Scenario**

Complex as microchips may be, we base our everyday lives on the assumption that these chips correctly do what we expect them to do. Microchips are omnipresent, ranging from our laptops, to home appliances, to safety-critical systems. A chip that performs correctly often remains unnoticed. It is when bugs occur that we realize how consequential it is to assume correctness of all the hugely complex chips surrounding us. For example, in 2011 Intel identified a problem with its Cougar Point chipset. They had to halt shipments and repair existing systems, with a total cost of about 700 million dollars.

Establishing chip correctness – beyond any doubt – is a hard problem. With cores being validated separately, this thesis focuses on verification of the interconnect between the cores. A major difficulty is that correctness of the interconnect is an emergent property depending on many different facets of the NoC, such as which cores run on top of it, which routes can be taken by messages in the interconnect, and under which conditions messages are stalled.

Formal verification is a technique for assessing that a system is correct, i.e., that it meets a specification formalized in some mathematical language. Generally, a formal model of the system is created using, for example, state machines or Petri nets. A specification is formulated in a logic such as Linear Temporal Logic (LTL). It is then proven that the model always satisfies the specification.

Whether it concerns the formulation of definitions, the implementation of an algorithm, or the proof of a theorem, humans' labor is always error-prone. Wolper asserts that "manual verification [of a program] is at least as likely to be wrong as the program itself" [146]. A proof can only reliably be called sound if it is built from very small logical reasoning steps. However, even in the proofs of the smallest theorems humans have the tendency to think in larger steps, eschewing the rigidity enforced by logic. The result is that human proofs are often unreliable. In contrast, the rigorous and fine-grained nature of logic perfectly suits a computer. The soundness of logical proofs can be verified more reliably by computers than by humans. It is therefore common practice to perform formal verification mechanically, that is, in such a way that its soundness can be ascertained by a computer.

Applying formal methods to on-chip interconnects provides trustworthy claims on their correctness. However, mechanical verification generally has to deal with a trade-off between ease of use and scalability. Automated and general techniques such as model checking are push-button solutions, but do not scale to the complexity of realistic NoCs. On the other hand, interactive and parametric techniques such as theorem proving are laborious and hard to use, which tends to prevent their widespread adoption. Currently, there is no way of formally verifying interconnects on the scale demanded by the NoC paradigm.

The contribution of this thesis consists of *easy* and *scalable* mechanical verification methods for communication networks. We formalize a notion of correctness, stating that a network is always eventually able to inject messages and that any injected message will always eventually arrive at its destination. We show that in order to establish this emergent correctness property for some NoC, it suffices to prove several smaller properties on isolated constituents. With a realistic example we conclude that many of these properties can easily be verified. Deadlock freedom, however, remains difficult to prove due to the interactions between the different constituents of the network. Therefore we provide formally proven correct tools and algorithms to hunt for deadlocks in communication networks.

This thesis advances the state-of-the-art both theoretically and practically. We provide new theories identifying deadlocks in communication networks. We prove that deciding deadlock freedom of wormhole networks is co-NP-complete. On the practical side, we design deadlock detection algorithms. A new tool is presented, which runs optimized C implementations of these algorithms in parallel. We present examples that could previously not be proven deadlock-free, due to either scalability issues or the complexity of dealing with many different facets of NoCs all at once. Our algorithms are able to either prove absence of deadlocks or report a counterexample. The correctness of our theories and algorithms has been established mechanically using the ACL2 theorem prover.

Before discussing the outline of this thesis, we present a short introduction into formal verification and communication networks. We then motivate the structure of this thesis using two examples. More background information and related work can be found in the next chapter.

## 1.1 Formal Verification

The current state-of-the-art in verifying on-chip networks is simulation [17, 15, 91]. Simulation can be used to predict the behavior of complex and interactive systems. An inherent disadvantage of simulation is the difficulty to obtain full coverage. Corner cases are hard to find and debug. Finding simulation patterns that cover them all is even more intricate. Simulation does not scale to future communication-centric SoCs [121]. The focus of this thesis is therefore on *analytical* formal verification approaches to complement simulation.

Analytical approaches do not consider dynamic and runtime behavior of a system, but statically analyze a system. Various different flavors of analytical mechanical verification exist. *Model checking* is an automated technique to check whether some model of a system satisfies a certain specification [81, 5]. The model is described in some sort of state machine and the specification is described in a temporal logic. A model checking algorithm uses the transition function associated to the state machine to explore the state space and to find states that do not satisfy the specification. If it finds such a state, both the state and the trace leading to this state are reported. If such a state is not found, the system is proven correct. Model checking is widely adopted by academia and industry alike, mostly because it is completely automatic and it can provide counterexamples. The major issue is a combinatorial blow-up of the number of states that needs to be explored, referred to as state space explosion. This severely limits the scalability of model checking.

*Theorem proving* is a technique where the proof of some mathematical theorem is formalized in such a way that a computer program can ensure its correctness. Theorem proving is an interactive process, during which the user supplies hints and lemma's to the theorem prover until the proof can be derived by the system. A theorem prover can guide the user while making his proof, by breaking down large proofs into smaller ones, by simplifying and rewriting the current goal, or by automatically searching for lemma's that can be used to prove the current theorem. The major advantage of theorem proving is the ability to deal with parametric systems. For example, the size of a network can remain unspecified, meaning that the theorem is proven to hold for networks with any size. Scalability is then measured by the amount of interaction with the user. Theorem proving is generally considered an academic effort, even though it has been adopted by various industry such as Intel and AMD. The process of theorem proving requires a relatively steep learning curve, and even for an experienced user it still often requires a great amount of interaction to prove non-trivial theorems.

*SAT solvers* are automated algorithms that decide whether some formula is satisfiable [100, 62]. Even though the satisfiability problem is well-known to be NP-complete, SAT solvers can prove truthness of propositional formulae with millions of variables. Satisfiability Modulo Theories (SMT) adds a background theory to a SAT solver, effectively giving an interpretation to some symbols [6]. For example,

the integer arithmetic theory assigns the expected interpretation to symbols such as  $<$ ,  $+$ , and  $0$ . Other examples of theories deal with various data structures such as lists, arrays, or bit vectors. The use of SAT solvers is completely automatic, but it requires the problem or theory that is to be proven to be formulated as a SAT instance. Many model checkers and theorem provers make use of SAT and SMT solvers under the hood.

This thesis applies both theorem proving and SMT solvers to perform parametric and scalable verification of NoCs. The ultimate purpose of this effort is to remove the traditional objection against theorem proving – namely that it is a difficult and time consuming process – while preserving the major advantage of scalable and analytical verification.

## 1.2 Communication Networks

In this thesis, the term communication network denotes a synchronous message passing network with a static topology. The behavior of all the switches in the network is predetermined and is assumed to be reliable. There is no packet loss, and communication wires do not cause any bit loss.

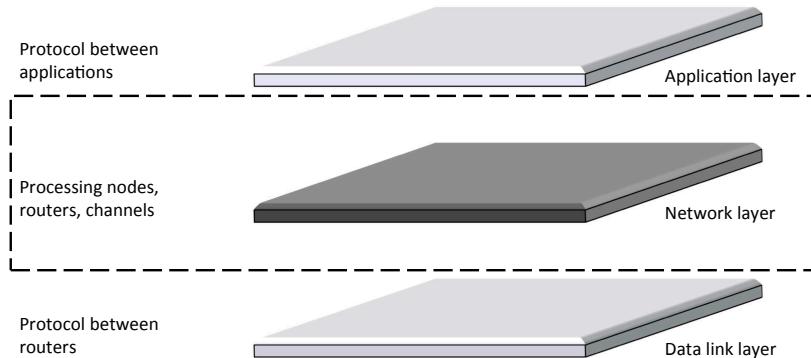

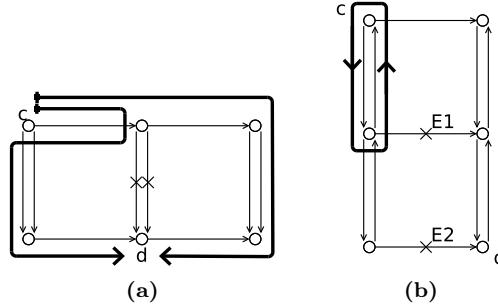

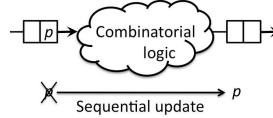

It is common practice to reason about the total functionality of a network in terms of different layers of abstraction defined by the OSI model [139]. This approach has also been adopted for on-chip networks [130, 88, 48]. Figure 1.2 shows the three different layers used in this thesis.

**Figure 1.2:** Three layers occurring in this thesis.

### Application Layer

The highest layer considered in this thesis is the application layer. At this layer, applications (or cores) such as processors or memory controllers run in parallel. These cores communicate with other cores by transmitting messages back and forth

## 1 Introduction

over the network. The behavior of the cores dictates where, when, and which types of messages are injected into the network. It also dictates where, when, and which types of messages are consumed from the network. The behavior of the cores will also be called the *application-layer protocol*.

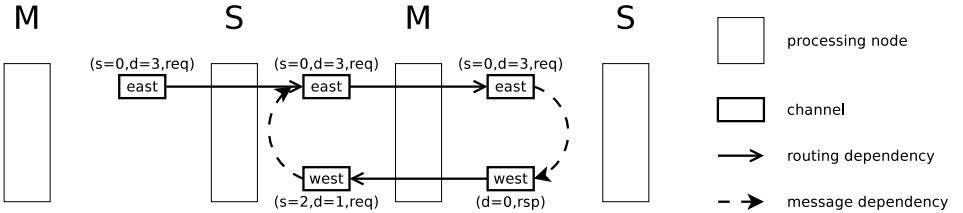

For example, a cache coherency protocol between the cores might induce that some of the cores (e.g., the processors) send out requests, while others transmit responses (e.g., the memory controllers). In this example, the protocol determines that two types of messages exists. It provides the destinations of these messages. It also determines that, e.g., a response is injected only when a request has arrived. In this case, the application-layer protocol causes a *message dependency* between requests and responses [68].

## Network Layer

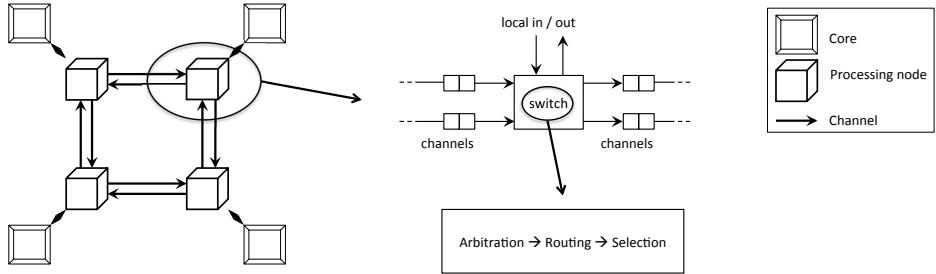

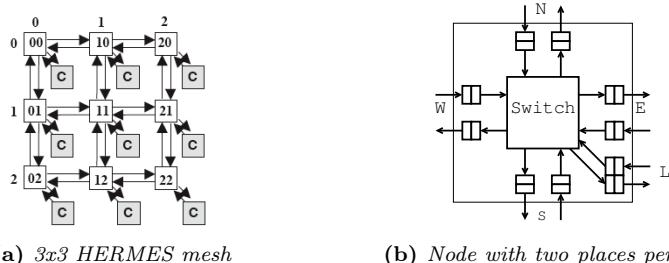

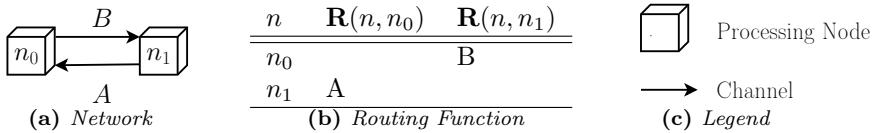

The second layer considered in this thesis is the network layer. In the OSI model, this layer coincides with both the network and the transport layer. Each core is connected to a *processing node* (see Figure 1.3). This node is able to inject messages received from the core into the network, and to remove messages sent to the core from the network. Any message arriving at the processing node is sent through a switch.

Switches are connected to each other via *channels*. Each channel has a certain capacity to store messages. Channels are the only components in the network that buffer messages. Generally, channels are directed, i.e., they are used to transmit messages from switch to switch unidirectionally.

A switch applies arbitration to determine which of their in-going channels is served. A *routing function* decides where the message is sent to. It can choose between one of the channels going out of the processing node, or the local outgoing channel leading to the core. The set of possible channels to which a message can be routed in one step is called the set of *next hops* of the message. Each time a message moves from channel to channel, the processing node at the end of its current channel decides a set of next hops and selects one that is able to receive the message. Routing can be deterministic, in which case each message has at most one next hop. This implies that routes are static and can be precomputed. In contrast, adaptive routing may supply multiple next hops per message. In case of adaptive routing, a selection function determines which of the next hops is taken [44]. Note that in case of adaptive routing at each time the set of next hops is static, i.e., the routing function itself does not change. However, since it supplies multiple next hops of which only one is to be selected, the route that a message can take from source to destination can vary.

We assume there is some atomic unit of transfer called a flow control digit (*flit*) [36]. The size and the type of this unit depend on the type of network. Messages are transformed into flits before they traverse the network. A message may consist of one or more flits, but each flit belongs only to one message.

## Link Layer

The lowest layer considered in this thesis is called the link layer. This layer contains the *transfer protocol* between two nodes. This protocol determines under which

Figure 1.3: Processing nodes in a network.

conditions a message may move from channel to channel.

For example, a network may have wires between each pair of connected channels to facilitate a handshaking protocol. When the target channel is ready to receive, it will send out a signal on such a wire. The transmitting channel does the same when it is ready to send. The transfer protocol states that if both signals are high, a message moves.

More complicated protocols can be applied. A network with credit-based flow control has extra wires to count the messages in the network. It prevents messages from moving to their next channel if a certain bound has been reached, even if the next channel has free buffers. Also, the transfer protocol may take care of synchronization between messages in the network. In this case, a message is moved only if some other message(s) in the network have reached a certain channel.

### 1.3 Network Layer Isolation versus Integration

The main structure of this thesis is based on two points of view on the network layer. In the first view, we formulate assumptions which abstract away from both the application layer and the link layer. This yields the *isolated network model*. In contrast, the *integrated network model* considers the three layers all at once. We first informally introduce both points of view.

In the isolated network model, the assumptions on the application layer state that cores are homogeneous and fair. As for the link layer, we assume that the transfer protocol moves a flit towards a next hop if this next hop is *available*, i.e., if the next hop is able to store the flit. This abstracts away among others counters or synchronizations. As a result, the isolated network model focuses on routing and topology. The isolated network model is based on the following assumptions:

- There is only one type of messages.

- Each core may send messages to all other cores.

- At each core, injection is fair, i.e., given some destination  $d$  each core will always eventually want to send a message to  $d$ .

- At each core, consumption is fair, i.e., if a message arrives at a switch connected to the destination core of the message, it will eventually be consumed. This is commonly referred to as the consumption assumption.

- The size of messages is always finite.

- A flit moves, if there exists a next hop that has available capacity to store the flit.

While the isolated network model abstracts away from details, the integrated network model incorporates all details concerning all three layers. The integrated network model encompasses among others the behavior of the cores, different message types, the interfaces between the cores and the processing nodes, the network topology, the routing logic, the injection method, and the transfer protocol between channels.

With two examples, we illustrate the different facets of both points of view.

### 1.3.1 Example 1

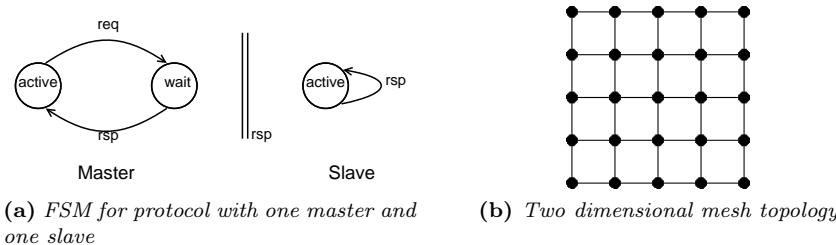

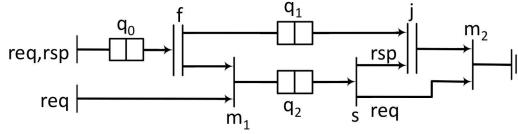

Consider the following simple application-layer protocol: a set of masters (e.g., processors) and slaves (e.g., memory controllers) communicate through request and response messages. A master sends a request to a slave and waits for the slave to return a response. Figure 1.4a shows the corresponding finite state machine. We use the handshaking operator  $\parallel_\alpha$  from Baier and Katoen [5]. At the network layer, masters and slaves are organized in a two dimensional mesh (Figure 1.4b). Messages are routed using XY routing [103]. This routes messages first in the horizontal direction to the right column and then vertically towards the right row. As for the link layer, messages move whenever there is an available next hop.

Figure 1.4

Taken in isolation, all components are deadlock-free. The protocol at the application layer is obviously deadlock-free. Masters wait for slaves, but slaves never wait and therefore there is no terminal state. The network is deadlock-free, as a 2D mesh with XY routing induces no circular dependencies [36]. There also are no circular message dependency, as a response can be generated by a node receiving a request, but not the other way around [68]. We show how deadlocks still may emerge from these deadlock-free components, depending on among others the layout of the masters and slaves.

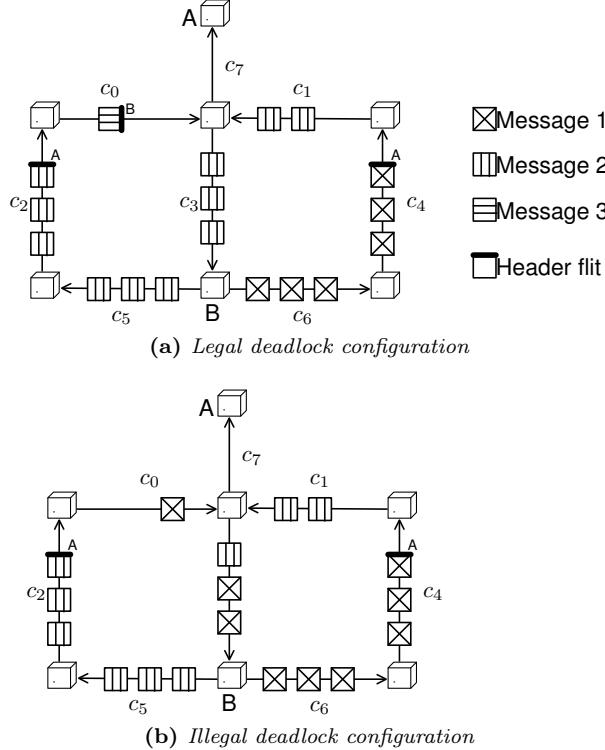

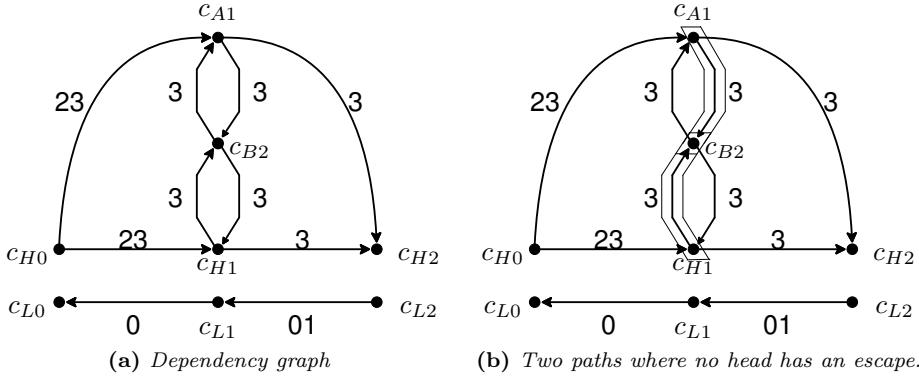

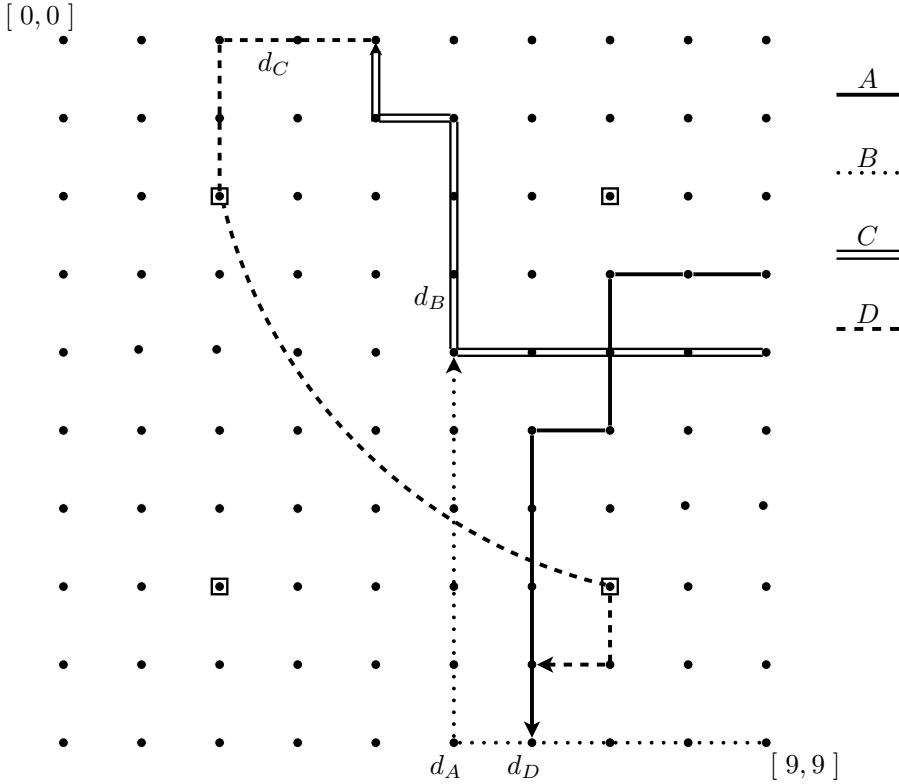

Consider the layout in Figure 1.5 where every odd (even) column is filled with masters (slaves). Each request packet has a source  $s$  (the master where the response needs to be directed to) and a destination  $d$  (the slave where the request needs to be directed to). Each response package has a destination  $d$  only. A deadlock can occur when responses get blocked by requests and cannot arrive at their destination.

Figure 1.5 shows the smallest deadlock possible in this layout. Requests injected at Master 0 and destined for Slave 3 are heading east. At Slave 3, these requests are turned into responses destined for the original source, Master 0. These responses are blocked by western bound requests injected by Master 2. These requests are turned into responses heading east at Slave 1. A circular wait has been created, and no message has an escape possibility out of this cycle. The combination of the routing logic with message dependencies has caused a deadlock.

**Figure 1.5:** Message-dependent deadlock in a 4x1 mesh. Nodes are identified by their  $x$ -coordinate.

Now consider the layout where all masters (slaves) are put on the left (right) side of the mesh. In such a layout, requests can be blocked by responses and other requests. This introduces new dependencies with respect to the routing dependencies. However, these new message dependencies cannot introduce a cycle. This is implied by the fact that a western bound message never needs to wait for a vertical channel or an eastern channel. Any western bound message is always a response, as masters are on the left side of the mesh. The XY routing logic ensures that a western bound message is not routed north or south. The only way a western bound response can be blocked is by another western bound response. Eventually, some western bound response will arrive at its destination. As it is a response, it will be consumed and no further message dependencies will occur. Since a western bound message can wait only for western channels, no cycles occur. In this layout the network is deadlock-free.

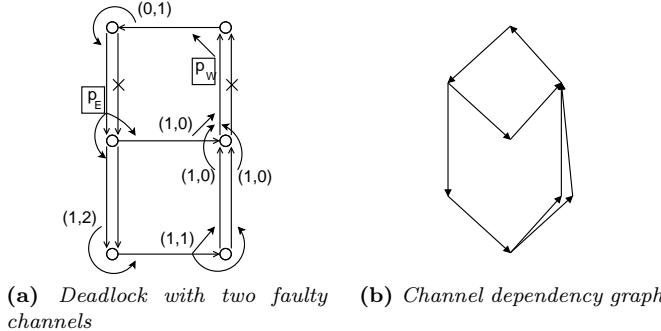

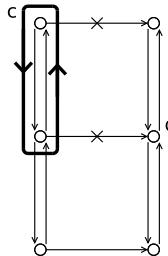

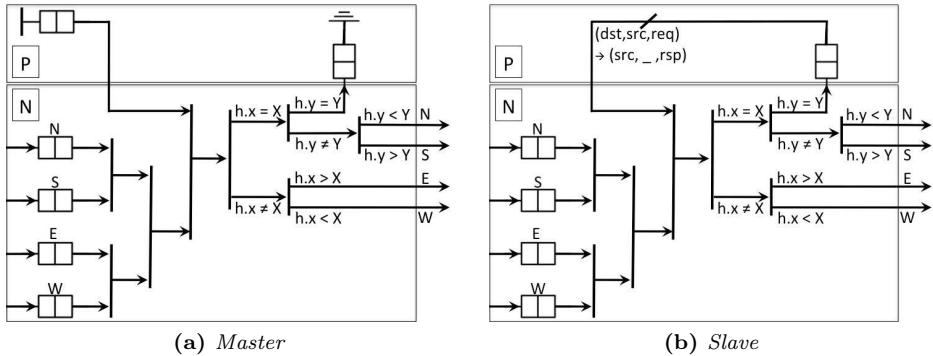

### 1.3.2 Example 2

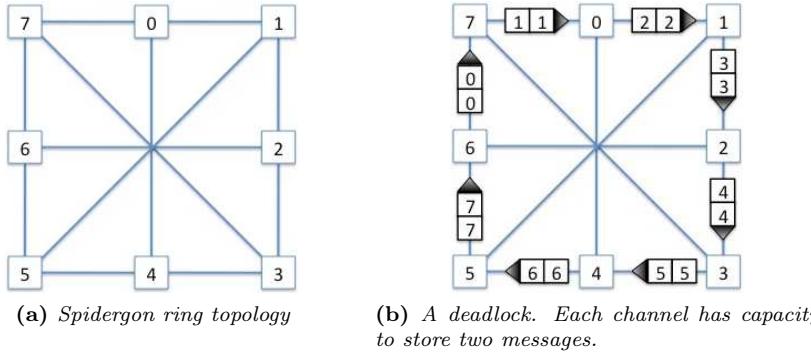

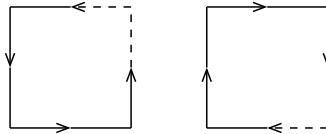

In this example, we abstract from the applications running on top of the network. The cores are simply assumed to be homogeneous. At the network layer, we consider the Spidergon NoC with shortest path routing [32] (see Figure 1.6a). Without further modification, the chip suffers from routing deadlocks. A deadlock can occur if each clockwise channel going out of processing node  $n$  is filled with messages destined for node  $n + 2 \bmod N$  with  $N$  the total number of processing

nodes (see Figure 1.6b).

Figure 1.6: Spidergon of STMElectronics

However, whether this deadlock actually occurs can depend on the link layer. For example, a credit-based flow control can make the network deadlock-free. This transfer protocol moves messages towards a channel only if the total number of messages in the network is below a certain bound  $B$ . The described deadlock can occur only when there are at least  $kN$  messages in the network, with  $k$  the capacity of the channels. Consequently, the transfer protocol ensures deadlock freedom for any  $B$  less than  $kN$ .

### 1.3.3 Isolated versus Integrated

Example 1 shows that a network can be deadlock-free when considered in isolation, whereas considering the system integrally yields deadlocks. Conversely, Example 2 shows that a network that is considered to have deadlocks when viewed in isolation, can actually be deadlock-free when the system in analyzed in its entirety.

Considering the network layer in isolation has been common practice for many years. More so, it is the entire purpose of the OSI model to facilitate a divide-and-conquer approach. First of all, dealing with the huge complexity of the whole system is practically infeasible. Secondly, separating the network from the applications running on top of it allows a modular approach. This separation is often even necessary, when during the design of a communication network it is not known which specific applications run on top of it. In such cases, correctness of the network can only be assessed under generic assumptions on the behavior of the possible applications. This approach has the additional advantage that design and verification efforts are reusable: they are correct for any application that satisfies the assumptions. Thirdly, even though it is the case that when analyzing a network in isolation yields a deadlock this deadlock might not actually occur, the knowledge that the network has deadlocks when considered in isolation is still valuable. This knowledge tells a designer that additional precautions are *required* to ensure deadlock freedom, i.e., that it is necessary to add deadlock-preventing elements to either the application or the link layer.

The greatest disadvantage of the isolated network model is that it is a very abstract model of communication networks. At the application layer it does not

allow different types of cores, or different types of messages. At the link layer it does not allow counters, scoreboards, or synchronizations. Therefore, the result of the analysis does not provide trustworthy results: deadlocks are not necessarily actual deadlocks, and deadlock freedom does not ensure actual deadlock freedom.

The integrated approach has the obvious advantage that the result is more reliable: if the system is proven deadlock-free while considering all three layers monolithically, deadlock freedom of the entire system can be stated with a high degree of confidence. Also, the integrated network model is not restricted in any way: it allows for all kinds of applications such as cache coherency and master/slave protocols and for all kinds of flow control such as synchronizations, duplications, and packet transformations.

The major disadvantage of the integrated network layer model is the enormous increase in complexity. Also, results of a verification effort are not reusable since the effort has been done taking all facets of the system into account.

## 1.4 Contribution of this Thesis

This thesis consists of four parts. Part I, the preamble relates the contributions of this thesis to the current state-of-the-art and provides background information required for the remaining three parts. The contents of the remaining parts are based on fourteen publications, including five journal articles, six peer-reviewed conference papers, and three peer-reviewed workshop papers.

In Part II we apply the ACL2 theorem prover to prove correctness of on-chip interconnects. This part contains two major contributions.

1. We formalize a novel notion of correctness for NoCs.

2. We extend GeNoC, a formal theory of communication networks in the ACL2 theorem prover, with this new notion of correctness. We formulate a set of assumptions and prove a generic theorem which states that *any* interconnection network that satisfies the assumptions is correct. GeNoC will be discussed in detail in the next chapter.

Part II is based on the following publications:

- Freek Verbeek and Julien Schmaltz. *Easy Formal Specification and Validation of Unbounded Networks-on-Chips Architectures*. ACM Transactions on Design Automation of Electronic Systems (TODAES), volume 17 (issue 1), pages 1:1–1:28, January 2012.

- Freek Verbeek and Julien Schmaltz. *Formal Specification of Networks-on-Chips: Deadlock and Evacuation*. Proceedings of Design, Automation and Test in Europe (DATE’10), pages 1701–1706, March 2010.

One of the conclusions presented in Part II is that the absence of deadlocks is the most difficult assumption required to prove correctness. The remainder of this thesis is concerned with establishing deadlock freedom of communication networks.

Part III considers deadlock verification in the isolated network model. It presents the following contributions:

## 1 Introduction

3. We formalize necessary and sufficient conditions for deadlock freedom of communication networks. A careful analysis of existing conditions is presented to show the relevance of our new conditions.

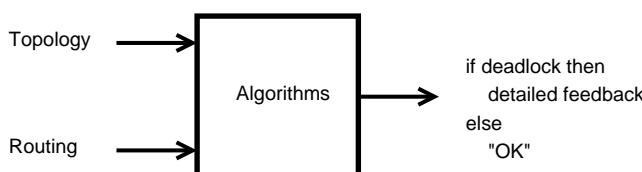

4. We present the tool DCI2 (for: Deadlock Checker In Designs of Communication Interconnects), which automatically decides whether these conditions hold for a given network. Additionally, it detects livelocks and various routing related issues under the *isolated* network model.

5. We prove deadlock detection NP-complete for wormhole networks.

6. Extensive experimental results are provided for non-trivial examples like adaptive fault-tolerant routing and for a chip with wireless transmissions.

The experimental results have been obtained in cooperation with Abdulaziz Alhussien and Nader Bagherzadeh from the University of California, Irvine (UCI). Part III is based on the following publications:

- Abdulaziz Alhussien, Freek Verbeek, Bernard van Gastel, Nader Bagherzadeh and Julien Schmaltz. *A Formally Verified Deadlock-Free Routing Function in a Fault-Tolerant NoC Architecture*. Proceedings of the 25th Symposium on Integrated Circuits and Systems Design (SBCCI'12), august 2012.

- Freek Verbeek and Julien Schmaltz. *Automatic verification for deadlock in networks-on-chips with adaptive routing and wormhole switching*. Proceedings of Networks-on-Chips Symposium (NOCS'11), pages 25–32, May 2011.

- Freek Verbeek and Julien Schmaltz. *A Fast and Verified Algorithm for Providing Store-and-Forward Networks Deadlock-Free*. Proceedings of The 19th Euromicro International Conference on Parallel, Distributed and Network-Based Computing (PDP'11), pages 3–10, February 2011.

- Freek Verbeek and Julien Schmaltz. *On Necessary and Sufficient Conditions for Deadlock-Free Routing in Wormhole Networks*. IEEE Transactions on Parallel and Distributed Systems (TPDS), volume 22 (issue 12), pages 2022–2032, December 2011.

- Freek Verbeek and Julien Schmaltz. *A Comment on “A Necessary and Sufficient Condition for Deadlock-Free Adaptive Routing in Wormhole Networks”*. IEEE Transactions on Parallel and Distributed Systems (TPDS), volume 22 (issue 10), pages 1775–1776, October 2011.

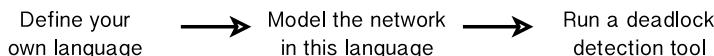

Part IV presents a deadlock detection algorithm in the integrated network model. It contains the following contributions:

7. We provide a syntax to enable the description of micro architectural models of communication fabrics.

8. We provide an algorithm detecting deadlocks in communication fabrics described in this syntax.

Our algorithm is able to deal with many different facets of monolithic network verification such as message dependencies and different types of link layers. In essence, the algorithm reduces the decision of deadlock freedom to solving many SMT instances. The examples presented in this chapter can be proven deadlock-free with this algorithm. Part IV is based on the following publications:

- Freek Verbeek and Julien Schmaltz. *Automatic Generation of Deadlock Detection Algorithms for a Family of Microarchitecture Description Languages of Communication Fabrics*. Proceedings of the IEEE International High Level Design Validation and Test Workshop (HLDVT'12). To appear.

- Freek Verbeek and Julien Schmaltz. *Towards the Formal Verification of Cache Coherency at the Architectural Level*. ACM Transactions on Design Automation of Electronic Systems (TODAES), volume 17 (issue 3), pages 20:1–20:16, June 2012.

- Freek Verbeek and Julien Schmaltz. *Hunting deadlocks efficiently in microarchitectural models of communication fabrics*. Proceedings of Formal Methods in Computer Aided Design (FMCAD'11), pages 223–231, November 2011.

## 1.5 The Role of ACL2 in this Thesis

The ACL2 theorem prover (see Section 2.3.1 for a short introduction and references for further reading) has played a vital role in the realization of this thesis. It has been used extensively to establish the validity of the definitions and proofs of many theorems. The focus of this thesis is on the theorems and the algorithms, but *not* on their verification in ACL2. Any reader interested in details on the ACL2 proofs can find these in the following publications:

- Freek Verbeek and Julien Schmaltz. *Proof Pearl: A formal proof of Dally & Seitz' necessary and sufficient condition for deadlock-free routing in interconnection networks*. Journal of Automated Reasoning (JAR), volume 48 (issue 4), pages 419–439, April 2012.

- Freek Verbeek and Julien Schmaltz. *Formal verification of a deadlock detection algorithm*. Proceedings of the International Workshop on the ACL2 Theorem Prover and its Applications (ACL2'11), pages 103–112, November 2011.

- Freek Verbeek and Julien Schmaltz. *Proof Pearl: A formal proof of Duato's condition for deadlock-free adaptive networks*. Proceedings of Interactive Theorem Proving (ITP'10), pages 67–82, July 2010.

- Freek Verbeek and Julien Schmaltz. *Formal Validation of Deadlock Prevention in Networks-On-Chips*. Proceedings of the International Workshop on the ACL2 Theorem Prover and its Applications (ACL2'09), pages 128–138, May 2009.

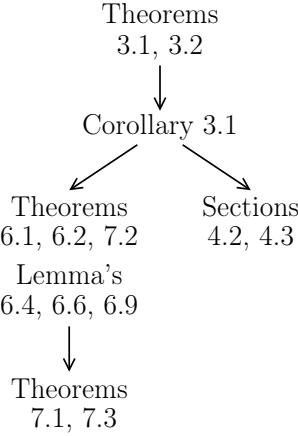

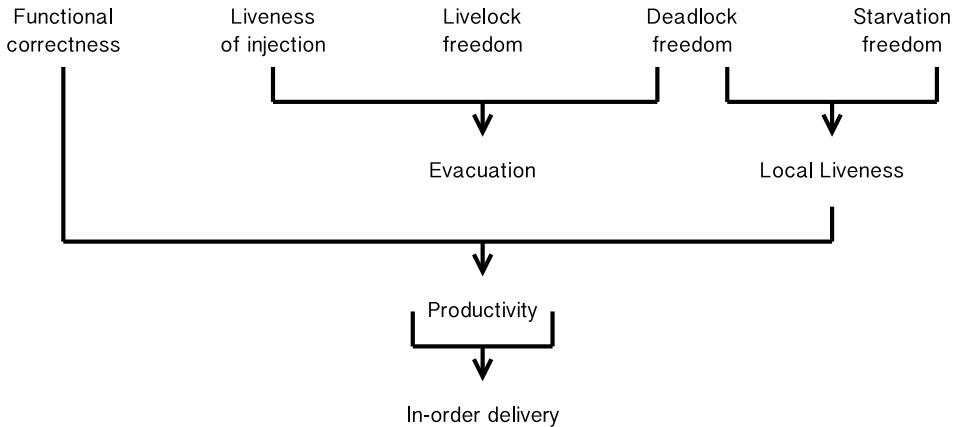

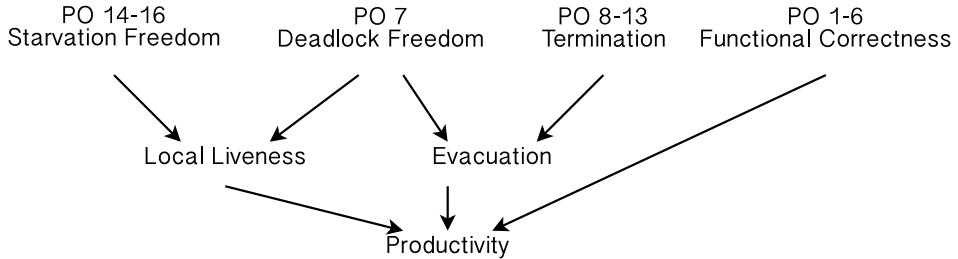

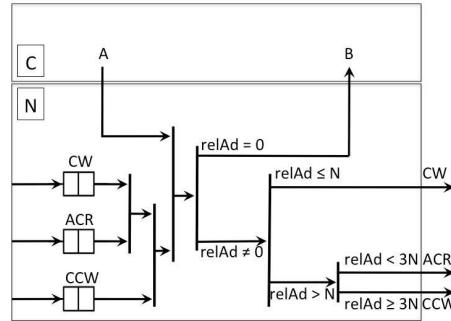

Figure 1.7 provides an overview of the ACL2 proof effort. The arrows do not represent implications, but stand for the structure in which the theorems have

been proven. The upper theorems and the definitions used to prove them have been used in proofs of lower theorems. Theorems 3.1, 3.2 and Corollary 3.1 are part of our extension of the GeNoC framework. The proofs in Sections 4.2 and 4.3 are examples of proofs established applying GeNoC. Theorems 6.1, 6.2, and 7.2 and Lemma's 6.4, 6.6 and 6.9 formulate correctness of our necessary and sufficient conditions. The proofs of these theorems rely upon the GeNoC framework. Finally, Theorems 7.1 and 7.3 formulate correctness of our algorithms, i.e., that they correctly check whether the necessary and sufficient conditions hold for some particular network.

**Figure 1.7:** *Mechanically proven theorems*

All the theorems in Part IV have *not* yet been verified mechanically. Additionally, our proof that deciding deadlock freedom of wormhole networks is co-NP-complete, Theorem 3.3 and Lemma 6.5 have not been formalized in ACL2.

The total proof effort related to this thesis consists of 39.321 lines of ACL2 code. This includes 3446 theorems (ACL2 defthm statements) and 858 definitions (ACL2 defun statements). ACL2 performs – while proving all the theorems – about 2.352.273.987 prover steps. All books are available upon request.

The added value of verifying all these theorems in ACL2 is twofold. First, it helped with getting all definitions completely correct. As example, the definition of a valid configuration in a wormhole network contains many subtleties. Section 6.7.2 (see Page 94) will show that the definitions as they were used in existing literature were incorrect. It was due to our formalization in ACL2 that we were able to formulate accurate and precise definitions. Secondly, the ACL2 theorem prover has greatly helped while *designing* the algorithms presented in this thesis. Our initial proof effort started with flawed algorithms. The final versions presented in Chapter 7 are the result of a mutual recursion between reformulating the algorithms and proving theorems about them. The algorithms contain a post-processing step, which is only required when for some very specific network, some specific *trace* of the algorithms yields an erroneous result. We would not have found the necessity of this post-processing step without proving correctness of the algorithms in ACL2.

---

# CHAPTER 2

## Advances to the State-of-the-art

---

This chapter discusses background information to facilitate the reading of the remaining parts of this thesis. We present the current state-of-the-art in formal verification of interconnection networks, with a focus on the architectures used on-chip. Whenever possible, we clearly show how this thesis advances the current state-of-the-art. After providing background information on interconnection networks, we give an overview on research related to deadlocks in communication networks. Finally, we provide an overview of the mechanical verification efforts related to communication networks.

### 2.1 Communication Networks

During the '00s, a multi-core shift occurred [94, 58]. In 2000, it was already possible to design SoCs with dozens of mutually communicating IP blocks. Following Moore's Law, more and more transistors could be put on a chip each year [98]. In 2009, the Intel single-chip cloud was able to run 48 general purpose – fully programmable – processing cores on one single die [74].

This revolution evoked a discussion on the interconnect between the cores. In 2000, Guerrier and Greiner discuss that the increase in complexity caused by multiple systems on a chip requires a shift from the traditional bus towards an on-chip network [67]. In the same year, Hemani et al. present an NoC, where resources communicate using addressed packets routed to their destination via a communication fabric [72]. Dally and Towles present an example of an on-chip network and discuss several challenges in their design [37]. In 2002, Benini and Micheli state that with more and more cores on a chip, the bus becomes the bottleneck in the overall performance of the system and coin NoC a new paradigm in chip design [8].

Interconnection networks, however, are not new. The importance of networking to communicate between processes was already recognized in the 70's. The ARPA network (the precursor of the Internet) triggered a great amount of research related to the performance, reliability and correctness of interconnects between computers [25]<sup>1</sup>. During the 80's and 90's, the interconnection networks *inside*

---

<sup>1</sup>This paper describes a deadlock on the "Internet" between UCLA and Stanford University.

multicomputers were widely studied [36, 44]. NoCs brought interconnection networks to the level of integrated circuits. What first took hundreds of square meters (e.g., the ASCI Red Super Computer reaching 1 teraflops in 1996), is now embedded on a single die (i.e., Intel’s Teraflops Research Chip with 80 cores).

Wolf recognizes two crucial differences between the early computer networks and the modern on-chip ones [145]. First, embedded systems require predictable performance. Due to the close cooperation between cores, bounds on the latency and throughput become crucial for the performance and correctness of the system. Secondly, constraints posed by power and energy become an issue on every level of abstraction. For example, whereas the interconnect between computers can simply drop and resend messages in order to resolve a deadlock, this becomes very costly in an on-chip network. In addition, Vermeulen et al. note that the topology of an on-chip network is static, whereas off-chip networks often dynamically add and remove links [143].

### Switching in NoCs

Generally, three types of switching are being used: circuit, packet<sup>2</sup> and wormhole switching. Packet and wormhole switching are the most commonly used [112, 107, 140]. Therefore, this thesis is not concerned with circuit switching.

#### Packet Switching

In a network with packet switching, messages are packetized before being injected. A *packet* consists of a payload and a header. The payload is the data of the message that is to be transmitted. The header contains the destination of the packet. A packet is the atomic unit of transfer.

As a packet contains all the information needed to route the packet through a network, it can move autonomously from channel to channel. At each router in the network, one or more next hops are determined. If one of these next hops is able to accept the packet, the packet is forwarded to that next hop. There is no reservation or prebooking of channels.

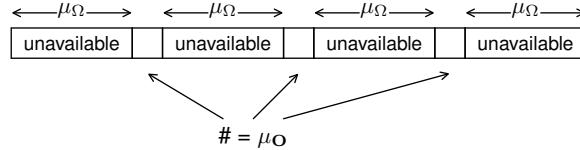

A crucial feature of packet networks is that the size of the packets is fixed and that the network is set up accordingly. A channel with capacity  $n$  can store exactly  $n$  packets. A packet is stored completely in a buffer of a channel. If it is routed towards a next channel, it is removed from its old position and moved integrally to a buffer of the next channel.

Since packets are stored and require new channels to be able to store them before they can move, contention may occur. A channel is available if it has at least one empty buffer. A packet is blocked if all its next hops are unavailable.

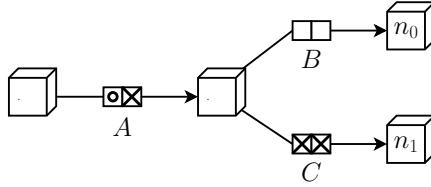

Channels can be implemented in two ways: *queues* and *central buffers*. With queues, the order in which packets arrive at the channel is relevant. Only the packet that arrived first, i.e., the packet at the head of the queue, is considered for forwarding to a next hop. With central buffers, any packet in the channel can be chosen to be forwarded to a next hop.

---

<sup>2</sup>In this thesis, packet switching denotes store-and-forward switching.

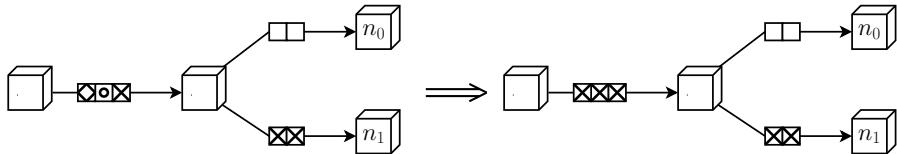

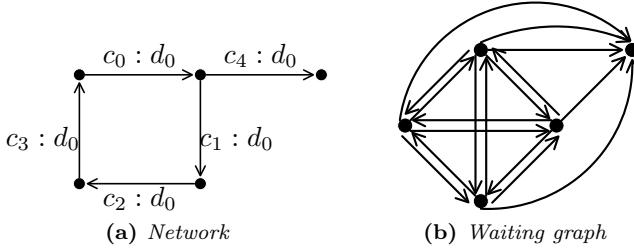

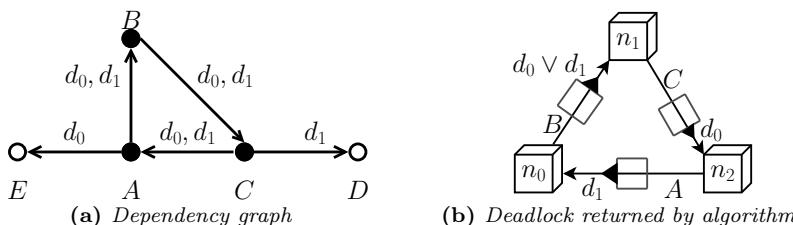

**Figure 2.1:** Network with packet switching. The circle (cross) packets are destined for  $n_0$  ( $n_1$ ).

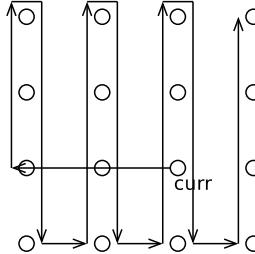

To stress this difference, consider Figure 2.1. The network contains three channels all with capacity 2. Channel  $A$  stores two packets, one destined for processing node  $n_0$  and one destined for processing node  $n_1$ . Channel  $C$  is full. Under queue semantics, none of the packets in channel  $A$  can move if the packet destined for  $n_1$  arrived first. Only the packet at the head of the queue is considered, and this packet cannot move because channel  $C$  has no empty buffer. Under central-buffer semantics, the packet in channel  $A$  destined for  $n_0$  can move.

Packet networks generally tend to have low contention, as packets do not occupy many resources. Adaptive routing can decrease contention even further, as packets move autonomously through the network. However, the storing of the packets in buffers makes latency unpredictable as it depends on the load of the network. Also, the size of the packets bounds the size of the messages that can be transmitted. If one message is divided into multiple packets, then some ordering mechanism has to ensure that packets are delivered in-order. For an in-depth discussion on packet switching, we refer to standard textbooks [38, 48].

### Wormhole Switching

In a network with wormhole switching, messages are split into *worms* before being injected. A worm consists of an arbitrary but finite number of flits. Two types of flits exist. A *header flit* is a flit containing the destination of the message. A *tail flit*, is a flit containing a part of the message that is to be sent. Each message has one header flit, but typically many tail flits. It is common practice to further distinguish between data flits, end-of-worm flits or flits storing the length of the worm. In this thesis, however, this distinction is not necessary and all these flits are denoted simply as tail flits.

When injecting a message, the header flit is injected first and leads the way. The header flit is routed autonomously from channel to channel. Similar to a packet, at each router a set of next hops is determined and the header flit is sent to a next hop that is ready to receive it. As the tail flits do not contain any information on their destination, they follow the header flit in a pipelined fashion.

At each successive channel, flits are stored before they are forwarded to their next hops. Each channel with capacity  $n$  is able to store exactly  $n$  flits. Contention occurs when the header flit has to wait for its next hops to become available.

A channel is available to accept tail flits if it has free buffers to store these flits. A channel is available to accept a header flit only if *all* its buffers are empty. This is of importance for the pipelining process. If channels store flits belonging to different messages, there is no way to distinguish which flits belong to which

message. A channel with tail flits cannot even accept the header flit of its own message.

Consequently, a header flit is blocked if all its next hops are non-empty. A tail flit is blocked if the next channel in the worm is full.

The most important advantage of wormhole networks is that they allow for relatively small buffers, as messages can be split up into many flits. However, as messages may hold many resources simultaneously, contention can be higher. For more details, we refer to standard text books [38, 48].

## 2.2 Deadlocks in Communication Networks

A deadlock is a situation where a set of processes is permanently blocked and no progress is ever possible. This can occur due to a competition for finite resources or reciprocal communications. Classically a deadlock is associated with a circular wait between processes: each process holds a resource needed by the next process [134]. In the context of interconnection networks, processes are messages and resources are channels. A deadlock can occur as messages compete for available channels.

There are three ways to deal with deadlocks: avoidance, prevention, and detection. In networks where deadlocks are avoided, deadlock freedom is ensured dynamically. The on-chip switching has some look-ahead mechanism and bases its decisions on extra information. In contrast, deadlock prevention statically ensures deadlock freedom. The routes messages can take are restricted, e.g., in such a way that messages are not sent into a circular wait. In networks with deadlock detection, routing can be less restricted. An online deadlock detection and recovery mechanism deals with deadlocks that occur as a result of these relaxed routing schemes.

In typical on-chip networks, routing decisions must be taken in a few nanoseconds. On-chip deadlock avoidance is too costly and is generally not considered a solution for NoCs. Some on-chip deadlock detection mechanisms have been proposed by Pinkston [116] and Martinez-Rubio et al. [93]. The most practical way of dealing with deadlocks is to prevent them by designing deadlock-free routing functions. This has been a fruitful research area for many years [11, 35, 18, 61, 28, 132].

### 2.2.1 Necessary and Sufficient Conditions

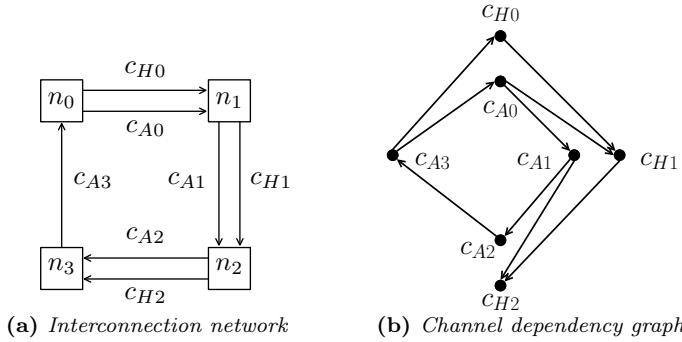

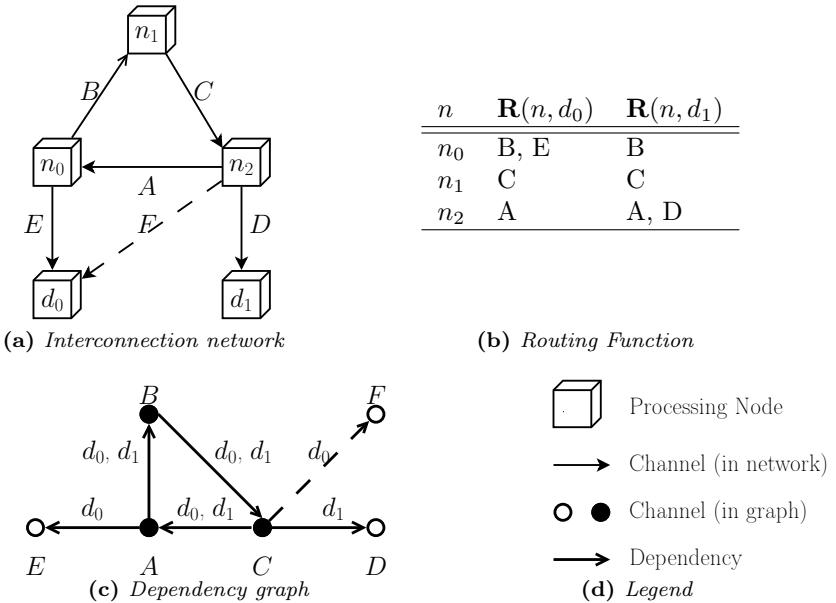

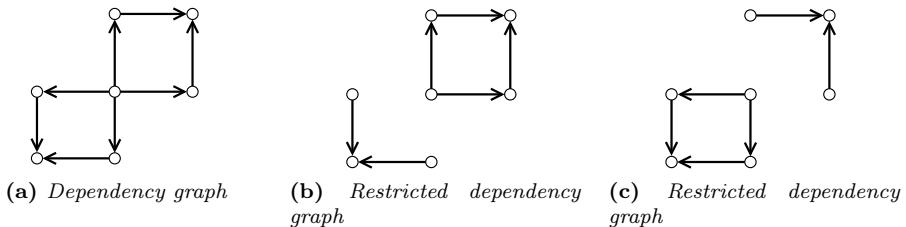

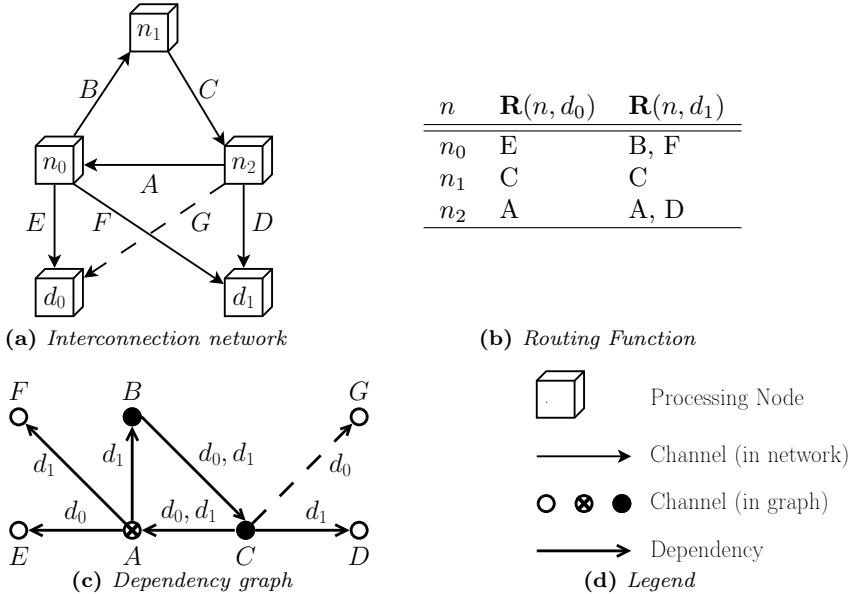

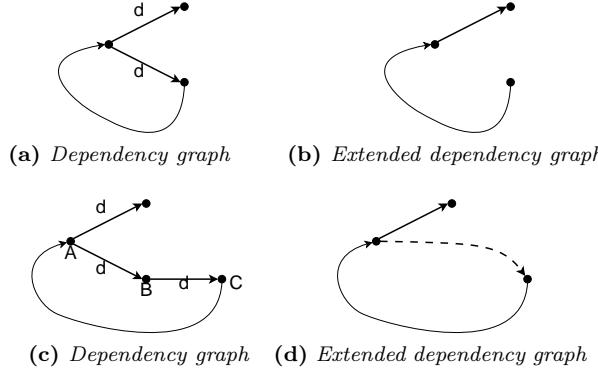

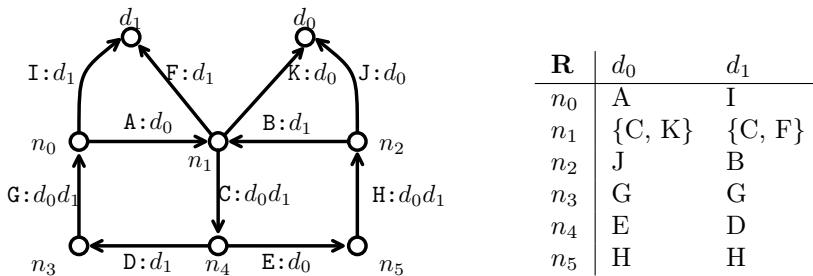

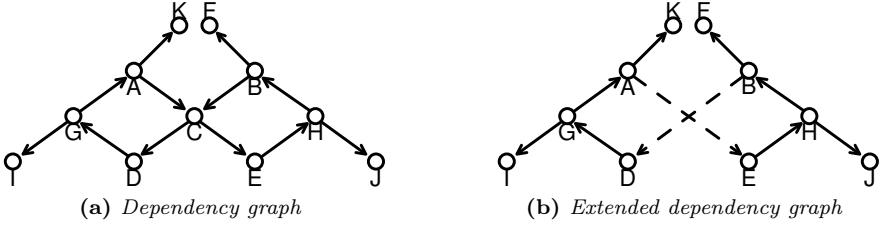

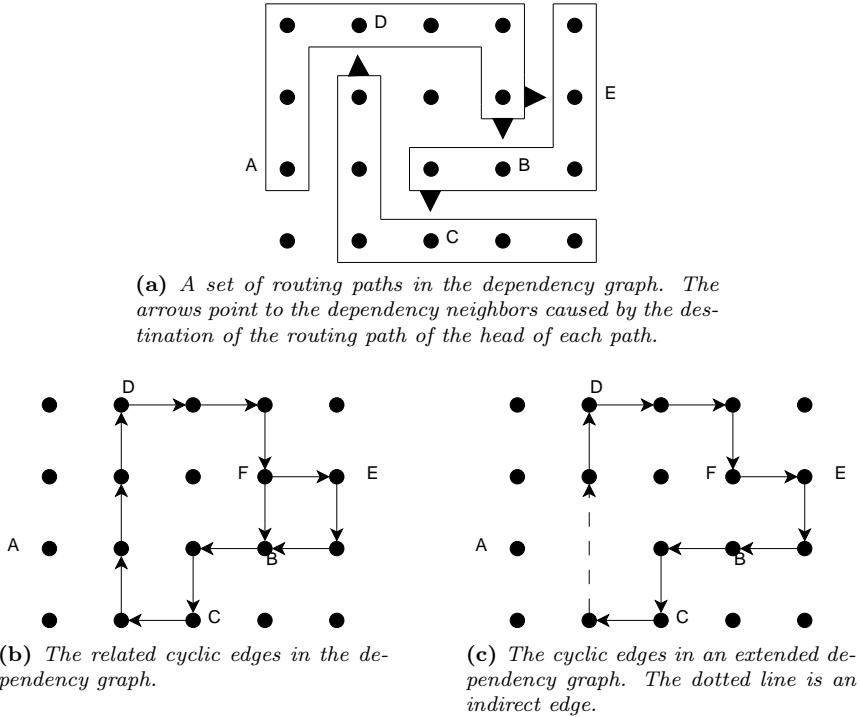

This research has lead to a search for *generic* conditions ensuring that a routing function is deadlock-free [36, 43, 44, 128, 54, 138]. Typically, the dependencies between channels are captured by a *dependency graph*. Early work by Dally and Seitz has shown that an acyclic dependency graph is a necessary and sufficient condition for deadlock-free routing [36]. This original condition only applies to deterministic routing functions.

An interconnection network can have an adaptive routing function. If a message is blocked on its way, an adaptive routing function proposes an alternative next hop allowing further progress. To the best of our knowledge, Chen was the first to notice that a cyclic dependency is not sufficient for deadlock in 1974 [25]. Cypher and Gravano prove a routing function deadlock-free that allows circular dependencies in a packet network [34]. Duato was the first to propose necessary

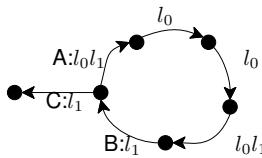

**Figure 2.2:** Example of cyclic dependencies without deadlock[48]

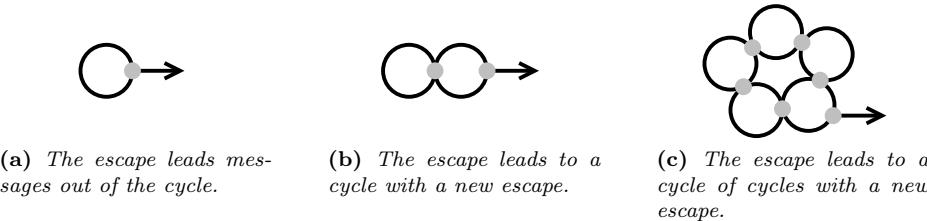

and sufficient conditions for deadlock-free routing in adaptive networks [44, 45]. He noticed that alternative paths could be used to *escape* deadlock situations and that a cyclic dependency is not a sufficient condition to create a deadlock [43]. He used Example 2.1 to demonstrate this [48].

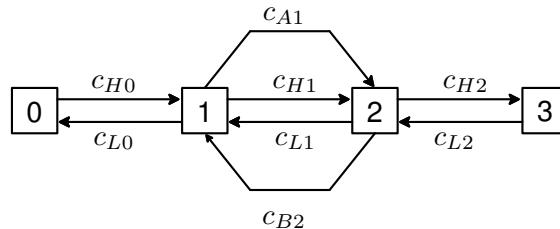

**Example 2.1** Consider the interconnection network in Figure 2.2a. Routing is defined as follows: when routing a message from source  $n_i$  to destination  $n_j$ , the routing function always returns channel  $c_{Ai}$ . It returns channel  $c_{Hi}$  only if  $j > i$ . The  $c_{Hi}$  channels do not form a dependency cycle, implying that they will always eventually become available. The  $c_{Ai}$  channels do form a dependency cycle. However, even if all channels of this cycle are unavailable, messages in node  $n_0$  can always *escape* the cycle by using channel  $c_{H0}$ . After this, the messages in the cycle can progress.

Based on his intuition, he defined and proved a condition capturing the fact that an adaptive network can still be deadlock-free even in the presence of cyclic dependencies between channels [44]. This was a breakthrough in the field as it enables a dramatic reduction in the number of resources to implement fully adaptive routing networks. It is also counterintuitive as it seems that a circular wait is not sufficient for deadlock. Duato's work was not easily accepted by his peers. On Duato's webpage one can read [46]:

Only a complex mathematical proof can show that deadlock freedom can be guaranteed if certain conditions are met. This research was so disruptive when it was developed that it was rejected by several peers and considered to be incorrect, even by the most prominent researchers at that time. However, it was finally accepted and several well-known researchers developed their own version of this theory.

Several more papers have been devoted to generic necessary and sufficient conditions for deadlock-free routing. Duato's condition holds for routing functions which are based on the current location of the message and its destination. Schwiebert and Jayasimha present a condition that holds for routing functions which also base their decisions on the direction from which the message came [128]. Fleury and Fraigniaud extended Duato's result to a broad class of routing functions [54]. Tak-

tak et al. were the first to present a condition that can be checked automatically in polynomial time [138]. Their condition is logically equivalent to Duato's one. These conditions will be discussed in more detail in Chapter 6.

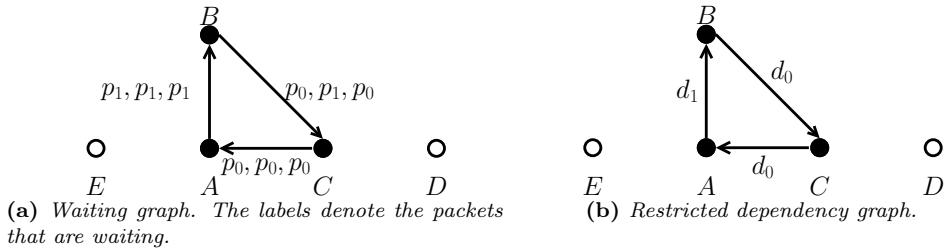

All these papers are devoted to wormhole switching. Wormhole networks are generally more prone to deadlock than packet networks. Messages can hold multiple channels at once. Channels are unavailable more often, as they can only store flits belonging to one message. Both types of network require different definitions and conditions for deadlock freedom. Duato also defined his condition for packet networks [45]. To the best of our knowledge, this is the only necessary and sufficient condition for adaptive deadlock-free routing in packet networks.

**The contribution of this thesis:** Chapter 6 will present new necessary and sufficient conditions for packet and wormhole networks. The proofs of correctness of existing conditions are often complex, highly abstract and counterintuitive. Therefore, we have applied the ACL2 theorem prover to mechanically prove correctness of our conditions. We will show that Duato's seminal condition for wormhole networks is not necessary and sufficient. Our condition is the first static necessary and sufficient condition for deadlock freedom in wormhole networks.

## 2.2.2 Determining Deadlock Freedom

Once necessary and sufficient conditions for the absence of deadlocks have been established, a natural next question is how to determine whether some network actually satisfies such a condition. In other words, how can we use these conditions to establish deadlock freedom of a given design? The condition of Dally and Seitz can easily be checked by computing the dependency graph and performing a linear search for cycles [33]. For adaptive routing however, this is more complicated as cycles are not necessarily deadlocks.

The most straightforward approach of determining that some network satisfies a condition is to just prove this by hand. Such a proof can be done mechanically or with pencil and paper. Advantage is that such proofs can be done leaving the size of the network parametric. However, such proofs become tedious very quickly. They are very time-consuming and require a lot of user interaction.

Another approach of determining that the network is deadlock-free is to limit the design process using some *design methodology*. Duato, Silla, et al. present a design methodology based on Duato's condition [44, 132]. Consider a network and a routing function that are already known to be deadlock-free. New channels and routing capabilities can be added to this network as long as once a message arrives in an original channel, it cannot be routed towards new channels. Duato's condition holds for any network obtained in this way.

Various design methodologies are based on a *turn model* [61, 29]. This model restricts the routing function in such a way that no cyclic dependencies occur. It was initially defined for 2D-mesh topologies. Starobinski et al. use the network calculus to generalize this methodology to general topologies [135]. Palesi et al. incorporate message dependencies, induced by a model of the applications running on the cores, into the dependency graph and provide a design methodology breaking all cycles [110].

These methodologies target static and fault-free networks. Duato, Lysne, et al. present a theory and a corresponding methodology to dynamically reconfigure a routing function in such a way that deadlock freedom is ensured [47, 90]. Their methodology applies to broad class of interconnection networks, both on-chip and off-chip.

An inherent disadvantage of such design methodologies is that they limit the designer. All these methods cannot be applied to arbitrary topologies and routing functions. Also, these methodologies are restrictive, in the sense that many deadlock-free designs are excluded. Most of these methodologies break all dependency cycles. As for adaptive routing a dependency cycle is not necessarily a deadlock, this is very limiting. Finally, these methodologies are manual and therefore error-prone.

A third approach of determining deadlock freedom is to add new channels – either virtual or physical – to a given design [36]. Seiculescu et al. automatically detect cyclic dependencies and determine where new channels can be added to break these [129]. Their approach is based on the sufficient condition that an acyclic dependency graph ensures deadlock freedom.

In 2008, Taktak et al. presented a different approach. They presented a dedicated algorithm to either detect deadlocks or prove deadlock freedom [137, 138]. The work of Taktak et al. will be discussed in more detail in Section 7.8 (see Page 129).

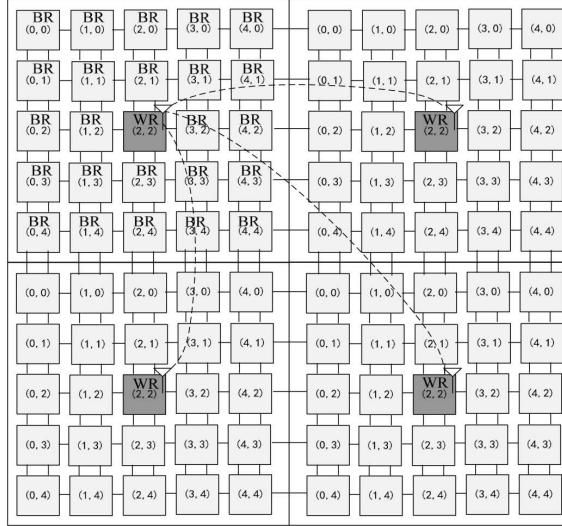

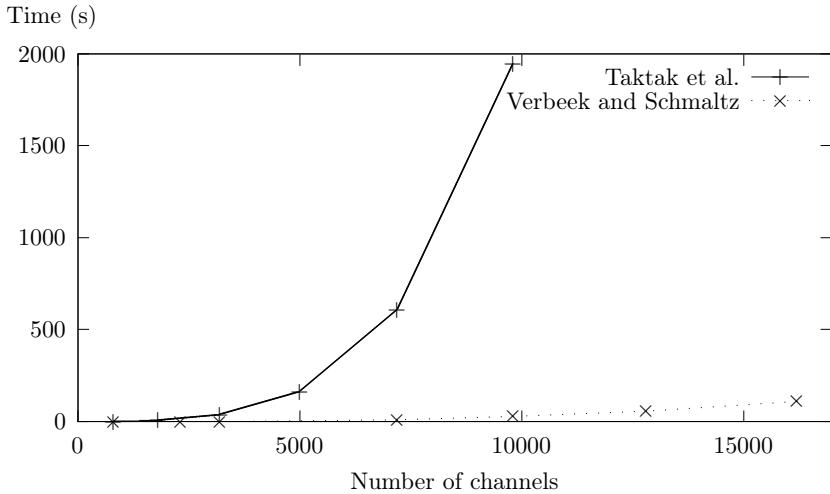

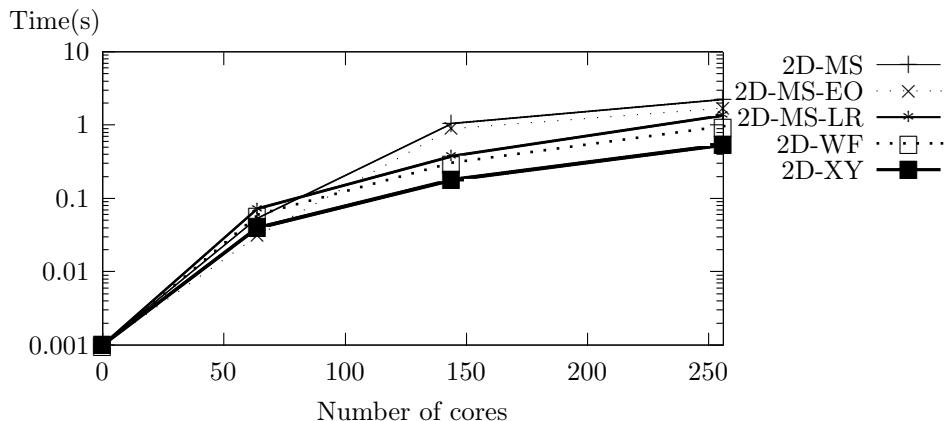

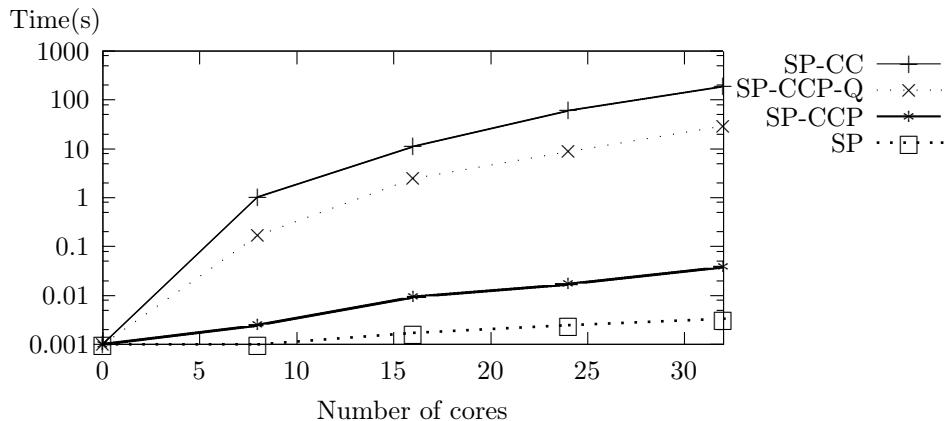

**The contribution of this thesis:** Our approach is similar to that of Taktak et al. Chapter 7 will present two fully automatic decision procedures for deadlock freedom in both packet and wormhole networks. Our wormhole algorithm checks a modified version of our necessary and sufficient condition. This version is only sufficient and therefore our algorithm may identify false deadlocks. We will show that deciding deadlock freedom of wormhole networks is co-NP-complete. This implies that the polynomial algorithm of Taktak et al. does not check a necessary and sufficient condition as well. Indeed, as the correctness of the algorithm of Taktak et al. is – indirectly – based on Duato’s condition, it is subject to false negatives. In contrast, the correctness of our algorithms has been established mechanically, using the ACL2 theorem prover. Our wormhole algorithm is one degree faster than that of Taktak et al. We will show that this improvement has a significant practical impact. As our tool is able to analyze millions of different network topologies efficiently, we are able to apply it to the verification of a fault-tolerant routing function in a mesh of 400 cores. This degree of scalability is not reachable with state-of-the-art tools.

## 2.3 Mechanical Verification of Interconnects

Several specific NoC architectures have been studied using model checking [122, 124, 27], theorem proving [60] or combinations thereof [1]. Regarding formal proofs of deadlock prevention, Gebremichael et al. formally prove a sufficient condition for the  $\mathbb{A}$ ethereal protocol of Philips in a packet-switched network [60]. The main property that has been verified is the absence of deadlock for an arbitrary number of masters and slaves. These works target very specific designs described at a low

level of abstraction. Goossens recognizes the need for more parametric verification: “Ideally, deadlock freedom would be proven for any instance of the NoC.” [63]

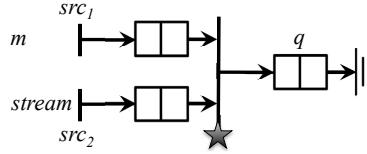

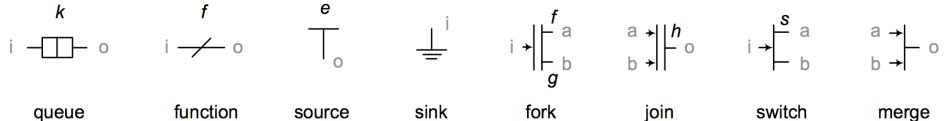

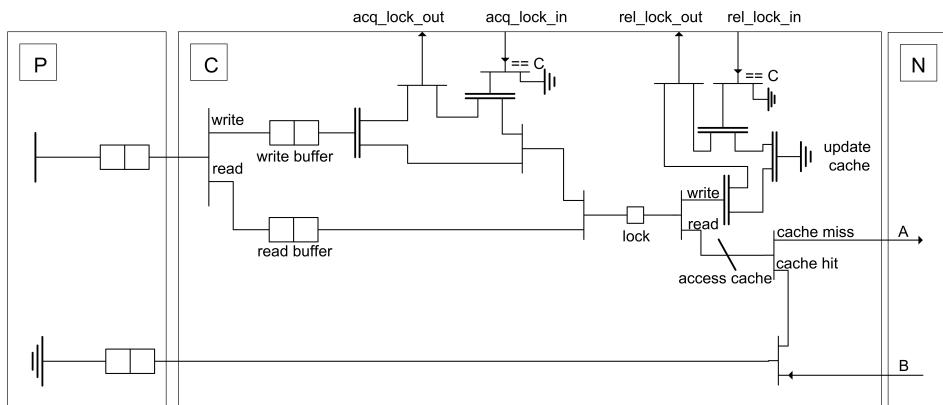

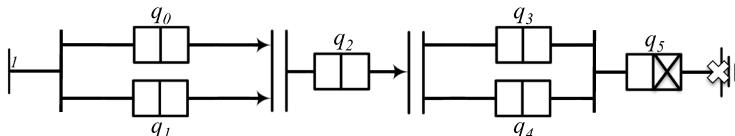

A different methodology is presented by Chatterjee et al. of the Intel Corporation. Recently, Chatterjee et al. proposed xMAS as a formal description language for microarchitectures [24, 23]. This language is based on a restricted set of primitives with well-defined semantics. The methodology consists of automatically generating inductive invariants and using these to model check a design [22]. This way they can establish, among others, deadlock freedom. Chapter 9 will discuss the xMAS language in-depth.

This thesis applies theorem proving to do parametric proofs over NoCs. Since the mid 70’s, interactive theorem provers have been designed to mechanically check formal and detailed proofs. Their development and application in various domains are active research fields. These proof assistants are used in projects about formalizing mathematics (e.g., the FlySpeck project [104, 106]) or in the verification of hardware and software designs (e.g., microprocessors [14, 55, 75], floating point units [123, 76, 10, 69], operating systems [87], entire computing systems [13]). The most popular tools are ACL2 [85], Coq [12], HOL [64], HOL-Light [70], Isabelle [105], and PVS [109].

To the best of our knowledge, the only work that targets parametric proofs over interconnection networks is by Schmaltz et al. [127, 21]. Schmaltz created a generic framework called *GeNoC* for reasoning about NoCs in the ACL2 theorem prover. We shortly introduce the ACL2 theorem prover and the GeNoC framework.

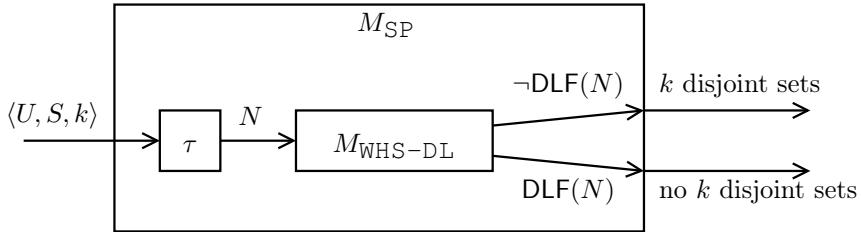

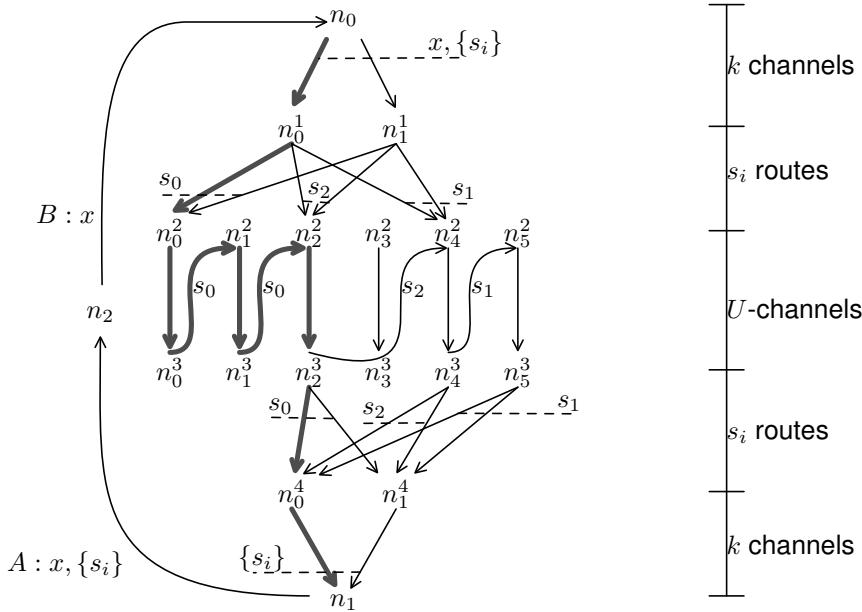

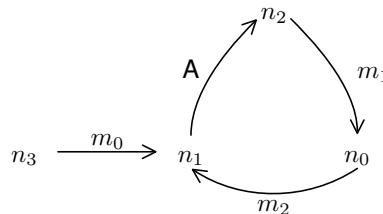

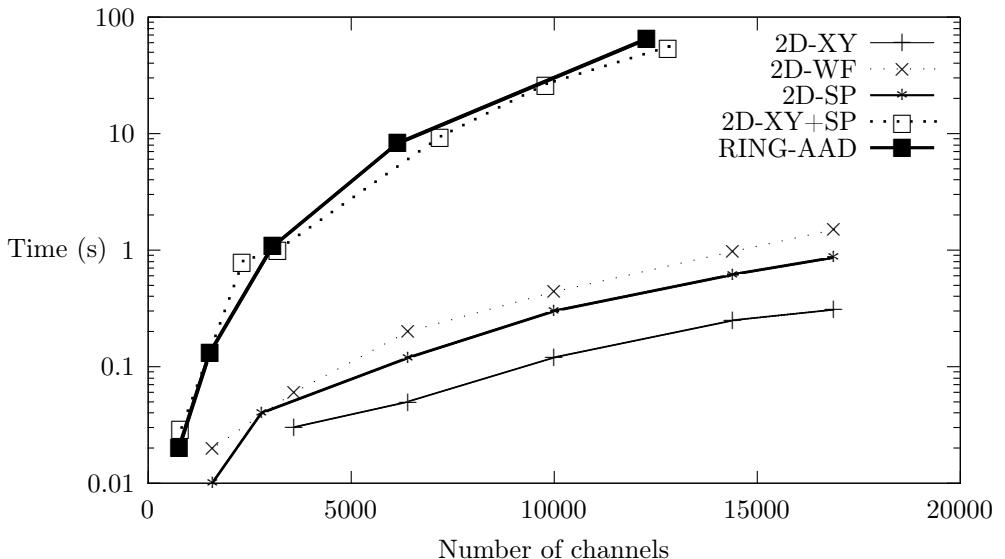

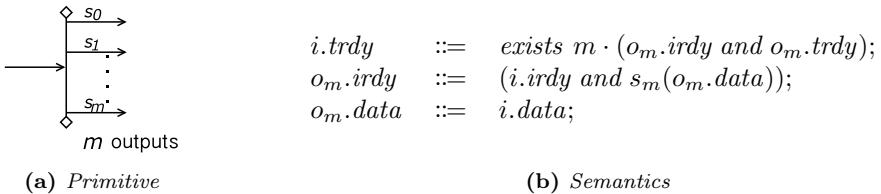

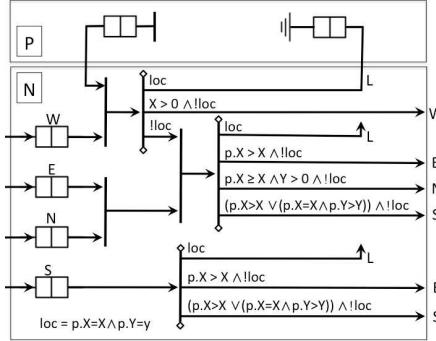

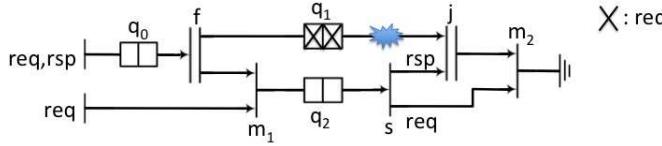

### 2.3.1 ACL2